Курсовая работа: Автоматизация измерений, контроля и испытаний

1. Основы метрологического обеспечения

Под метрологическим обеспечением (МО) понимается установление и применение научных и организационных основ, технических средств, правил и норм, необходимых для достижения единства и требуемой точности измерении. Основной тенденцией в развитии МО является переход от существовавшей ранее сравнительно узкой задачи обеспечения единства и требуемой точности измерений к принципиально новой задаче обеспечения качества измерений.

Качество измерений понятие более широкое, чем точность измерений. Оно характеризует совокупность свойств СИ, обеспечивающих получение в установленный срок результатов измерений с требуемыми точностью (размером допускаемых погрешностей), достоверностью, правильностью, сходимостью и воспроизводимостью.

Понятие "метрологическое обеспечение" применяется, как правило, по отношению к измерениям (испытанию, контролю) в целом. В то же время допускают использование термина "метрологическое обеспечение технологического процесса (производства, организации)", подразумевая при этом МО измерений (испытаний или контроля) в данном процессе, производстве, организации. Объектом МО являются все стадии жизненного цикла (ЖЦ) изделия (продукции) или услуги. Под ЖЦ понимается совокупность последовательных взаимосвязанных процессов создания и изменения состояния продукции от формулирования исходных требований к ней до окончания эксплуатации или потребления.

Так, на стадии разработки продукции для достижения высокого качества изделия производится выбор контролируемых параметров, норм точности, допусков, средств измерения, контроля и испытания. Так же осуществляется метрологическая экспертиза конструкторской и технологической документации. При разработке МО необходимо использовать системный подход, суть которого состоит в рассмотрении указанного обеспечения как совокупности взаимосвязанных процессов, объединенных одной целью достижением требуемого качества измерений. Такими процессами являются:

• установление рациональной номенклатуры измеряемых параметров и оптимальных норм точности измерений при контроле качества продукции и управлении процессами;

• технико-экономическое обоснование и выбор СИ, испытаний и контроля и установление их рациональной номенклатуры;

• стандартизация, унификация и агрегатирование используемой контрольно-измерительной техники;

• разработка, внедрение и аттестация современных методик выполнения измерения, испытаний и контроля (МВИ);

• поверка, метрологическая аттестация и калибровка контрольно-измерительного и испытательного оборудования (КИО), применяемого на предприятии;

• контроль за производством, состоянием, применением и ремонтом КИО, а также за соблюдением метрологических правил и норм на предприятии;

• участие в разработке и внедрении стандартов предприятия;

• внедрение международных, государственных и отраслевых стандартов, а также иных нормативных документов Госстандарта;

• проведение метрологической экспертизы проектов нормативной, конструкторской и технологической документации;

• проведение анализа состояния измерений, разработка на его основе и осуществление мероприятий по совершенствованию МО;

• подготовка работников соответствующих служб и подразделений предприятия к выполнению контрольно-измерительных операций.

Метрологическое обеспечение имеет четыре основы: научную, организационную, нормативную и техническую. Отдельные аспекты МО рассмотрены в рекомендации МИ 2500-98 по метрологическому обеспечению малых предприятий. Разработка и проведение мероприятий МО возложено на метрологические службы (МС). Метрологическая служба служба, создаваемая в соответствии с законодательством для выполнения работ по обеспечению единства измерений и осуществления метрологического контроля и надзора.

2. Цифровые устройства: шифраторы и дешифраторы, сумматоры, счетчики, мультиплексоры, регистры, магнитоэлектронные переключатели

Интегральные счетчики

Интегральный счетчик — цифровое устройство (цифровая микросхема или ее часть), выполненное на интегральных триггерах со схемами управления разной структуры и осуществляющее счет поступающих на его вход импульсов. Счет импульсов в счетчик представляется определенными комбинациями состояний триггеров. При поступлении на вход схемы очередной логической 1 в счетчике устанавливается новая комбинация состояний триггеров, соответствующая числу, превышающему предыдущее на единицу. Такие счетчики называют суммирующими. В цифровой измерительной технике применяют и вычитающие счетчики, в которых в процессе счета входные числа последовательно убывают на единицу, а также реверсивные счетчики, способные переключаться из режима суммирования в режим вычитания и наоборот.

Для представления чисел в счетчиках используются в основном двоичная, десятичная и двоично-десятичная системы счислений. При применении двоичной системы счисления логические уровни на прямых выходах триггеров определяют цифры двоичных разрядов числа. В этом случае каждый разряд числа в счетчике обеспечивается определенным состоянием одного триггера. Максимальное число импульсов, которое может быть записано, составляет N = 2л-1, где п — число разрядов (число триггеров) в счетчике.

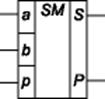

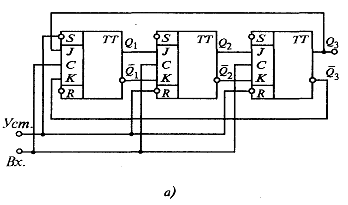

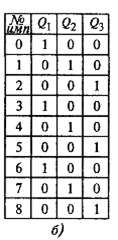

Рассмотрим простейший двоичный кольцевой счетчик, представляющий собой три замкнутых в кольцо JК-триггеров (рис.1, а), по которым под воздействием входных импульсов (точка Вх) циркулирует одна пли несколько кодовых единиц.

В рассматриваемой схеме прямой выход каждого предыдущего триггера соединен с входом J последующего триггера. Тактовые входы С всех триггеров объединены (узел Вх.) и на них поступают счетные импульсы. Перед началом счета первый триггер импульсным сигналом Уст. устанавливается в состояние 1, остальные триггеры — в состояние 0. Этому состоянию счетчика соответствует 0 на выходе Q 3 последнего триггера. После отключения сигнала Уст, начинается счет, и триггеры функционируют как обычные JK-триггеры.

Поскольку на информационных входах первого триггера было установлено J = 0 и К = 1, в момент окончания первого входного импульса он перейдет в состояние логического 0. Второй триггер примет состояние 1, так как на его входах было J = К = 1. Третий триггер не изменит своего предыдущего состояния. Таким образом, кодовая 1 перешла с первого триггера на второй. По окончании каждого следующего входного импульса 1 будет перемещаться от предыдущего триггера к последующему, т.е. переходить по схеме вправо (см. таблицу истинности на рис. 1, б).

рис.1. Кольцевой счетчик:

а – схема; б – таблица истинности

Шифраторы и дешифраторы

Прежде чем перейти к рассмотрению специфических устройств цифровой измерительной техники- шифраторов и дешифраторов, обратимся к системам отображения цифровой информации.

Системы счисления и коды, применяемые в цифровой измерительной технике. Для изображения любых чисел существует некоторое ограниченное число знаков и порядок их написания — это и есть система счисления. В наиболее привычной для нас десятичной системе таких знаков десять: 0, 1, 2,..., 9. Форма записи числа в десятичной систем счисления имеет вид:

![]() (1)

(1)

где 10 i — десятичный разряд; а i — значение символа в соответствующем разряде, которое может быть любым от 0 до 9.

Например, число 583 с помощью трех десятичных разрядов запишется как: N = 583 = 102-5 + 10'-8 + 10°-3.

|

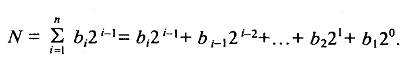

Аналогично записывается целое число и в двоичной системе счисления:

Здесь коэффициенты b i, принимают лишь два значения: 0 и 1. Например, число 583 в двоичной системе запишется в виде

N= 1.29+0.28 + 0.27 + 1. 26+0.25+0.24+0.23+ 1. 22 + 1.2'+ 1.2°. (3)

Следовательно, числу 583 в десятичной системе соответствует число в двоичной - 1001000111. Последнее принято называть кодом числа в двоичной системе счисления. Написание числа в двоичном коде оказывается удобным для проведения арифметических действий по законам булевой алгебры, что применяется в вычислительных устройствах и, в частности, в компьютерах.

При использовании десятичной системы счисления для образования кода требуется десять различных импульсов, например отличающихся амплитудой, длительностью и пр. Такое представление кодов не применяют, так как для образования и его распознавания требуется сложная аппаратура, в то время как для образования и обработки двоичного кода могут быть использованы простые, двоичные элементы, имеющие всего два состояния: единица и нуль. Двоичный код наиболее компактен (экономичен) и пока является основным кодом в компьютерной технике. Однако двоичный код неудобен для управления десятичным цифровым отсчетным устройством измерительной аппаратуры.

Поэтому в цифровой измерительной аппаратуре широко используется двоично-десятичные и тетрадно-десятичные коды, так как представление измеряемой величины на индикаторе должно быть выполнено в привычном для наблюдающего человека десятичном виде, а перевод двоичного кода в десятичный — сложная задача для оператора.

В тетрадно-десятичной системе каждая десятичная цифра (0...9) кодируется четырьмя двоичными числами 0 и 1 (тетрада) при различных носовых коэффициентах. Широко распространен в цифровых измерительных приборах (ЦИП) код 8421, в котором весовыми коэффициентами являются цифры 8, 4, 2, 1 (табл.1).

Таблица 1. Двоично-десятичный код 8421

| Десятичные цифры | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

| Код 8421 | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 |

Если вернуться к числу 583, то в коде 8421 оно будет представлено следующим образом:

583=102(8-0+41+2-0+1-1)+10'(8-1+4-0+20+1-0)+10°(8-0+4-0+21 + 11). (4)

Соответственно тетрадно-десятичная запись имеет вид

0101 1000 0011

Помимо двоично-десятичного кода при построении цифровых измерительных приборов применяются коды и с другими весовыми коэффициентами (тетрадно-десятичные коды), например: 4 2 2 1 и др. Эти коды неоднозначные (т.е. числа можно получить разными комбинациями), но требуют меньше символов, что иногда важно. Для устранения неоднозначности принимают специальные меры.

В широко используемых в цифровой измерительной технике десятичных (декадных) счетчиках цифры разрядов десятичного числа представляются в четырехразрядной двоичной форме, т.е. используется двоично-десятичная система исчисления. При этом для каждого разряда десятичного числа используется четыре триггера и, если число десятичных разрядов к, то для регистрации чисел в десятичном счетчике необходимо задействовать 4к триггеров. Максимальное число записанных импульсов в счетчике в этом случае составляет N = 10k- 1. Десятичные счетчики широко применяют в случаях, когда число поступающих импульсов необходимо представить в привычной для человека десятичной системе счисления.

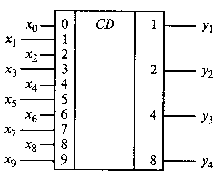

Шифратор (называемый часто кодером) — устройство, преобразующее десятичные числа в двоичную систему счисления. Пусть в шифраторе имеется т входов, последовательно пронумерованных десятичными числами (0, 1, 2, 3,..., т - 1), и п выходов. Поступление сигнала на один из входов вызывает появление на выходах n-разрядного двоичного числа, соответствующего номеру возбужденного входа.

Из теории передачи информации известно, что построить шифраторы с большим числом входов т технически трудно, поэтому они используются для преобразования в двоичную систему счисления небольших десятичных чисел. Для преобразования больших десятичных чисел используются специальные методы.

Шифраторы часто снабжаются клавиатурой, каждая клавиша которой связана с определенным входом шифратора, и на его выходе воспроизводится двоичное число, соответствующее написанному на клавише символу.

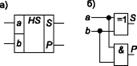

На рис.2 показано условное изображение шифратора, преобразующего первые десять цифр десятичного счисления 0, 1, 2,..., 9 в двоичное представление. Символ CD в обозначении образован из букв, входящих в английское слово CODER, Слева на схеме показано десять входов, обозначенных соответствующими десятичными числами. Справа представлены выходы шифратора: цифрами 1, 2, 4, 8 обозначены весовые коэффициенты двоичных разрядов, соответствующих отдельным выходам.

|

Рис.2. Условное изображение шифратора

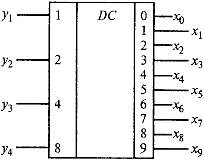

Дешифратор (называемый также декодером) предназначен для обратного преобразования двоичных чисел в сравнительно небольшие по значению десятичные числа. Входы дешифратора служат для подачи двоичных чисел, выходы последовательно нумеруются десятичными числами. Дешифраторы широко используются в цифровой измерительной технике. В частности, их применяют в устройствах, печатающих на бумаге выводимые из цифровой схемы текст или числа. В таких устройствах двоичное число, поступая на соответствующий вход дешифратора, вызывает появление сигнала на его определенном выходе.

На рис. 3. в качестве примера приведено условное изображение одной из простейших структурных схем дешифратора. Символ DC образован из букв английского слова DECODER.

Слева от схемы представлены входы шифратора: цифрами 1, 2, 4, 8 обозначены весовые коэффициенты дешифратора двоичных разрядов. Справа показаны десять выходов, пронумерованных десятичными числами, соответствующими отдельным комбинациям входного двоичного числа. На каждом выходе дешифратора при строго определенной комбинации входного двоичного кода вырабатывается логическая 1.

Рис.3. Условное изображение дешифратора

Сумматоры.

Основной элементарной операцией, выполняемой над кодами чисел в цифровых устройствах, является арифметическое сложение.

Сумматор — логический операционный узел, выполняющий арифметическое сложение кодов двух чисел. При арифметическом сложении выполняются и другие дополнительные операции: учёт знаков чисел, выравнивание порядков слагаемых и тому подобное. Указанные операции выполняются в арифметическо-логических устройствах (АЛУ) или процессорных элементах, ядром которых являются сумматоры.

Сумматоры классифицируют по различным признакам.

В зависимости от системы счисления различают:

· двоичные;

· двоично-десятичные (в общем случае двоично-кодированные);

· десятичные;

· прочие (например, амплитудные).

По количеству одновременно обрабатываемых разрядов складываемых чисел:

· одноразрядные,

· многоразрядные.

По числу входов и выходов одноразрядных двоичных сумматоров:

· четвертьсумматоры (элементы “сумма по модулю 2”; элементы “исключающее ИЛИ”), характеризующиеся наличием двух входов, на которые подаются два одноразрядных числа, и одним выходом, на котором реализуется их арифметическая сумма;

· полусумматоры, характеризующиеся наличием двух входов, на которые подаются одноимённые разряды двух чисел, и двух выходов: на одном реализуется арифметическая сумма в данном разряде, а на другом — перенос в следующий (более старший разряд);

· полные одноразрядные двоичные сумматоры, характеризующиеся наличием трёх входов, на которые подаются одноимённые разряды двух складываемых чисел и перенос из предыдущего (более младшего) разряда, и двумя выходами: на одном реализуется арифметическая сумма в данном разряде, а на другом — перенос в следующий (более старший разряд).

По способу представления и обработки складываемых чисел многоразрядные сумматоры подразделяются на:

· последовательные, в которых обработка чисел ведётся поочерёдно, разряд за разрядом на одном и том же оборудовании;

· параллельные, в которых слагаемые складываются одновременно по всем разрядам, и для каждого разряда имеется своё оборудование.

Параллельный сумматор в простейшем случае представляет собой n одноразрядных сумматоров, последовательно (от младших разрядов к старшим) соединённых цепями переноса. Однако такая схема сумматора характеризуется сравнительно невысоким быстродействием, так как формирование сигналов суммы и переноса в каждом i-ом разряде производится лишь после того, как поступит сигнал переноса с (i-1)-го разряда. Таким образом, быстродействие сумматора определяется временем распространения сигнала по цепи переноса. Уменьшение этого времени — основная задача при построении параллельных сумматоров.

Для уменьшения времени распространения сигнала переноса применяют: конструктивные решения, когда используют в цепи переноса наиболее быстродействующие элементы; тщательно выполняют монтаж без длинных проводников и паразитных ёмкостных составляющих нагрузки и (наиболее часто) структурные методы ускорения прохождения сигнала переноса.

По способу организации межразрядных переносов параллельные сумматоры, реализующие структурные методы, делят на сумматоры:

· с последовательным переносом;

· с параллельным переносом;

· с групповой структурой;

· со специальной организацией цепей переноса.

Среди сумматоров со специальной организацией цепей переноса можно указать:

· сумматоры со сквозным переносом, в которых между входом и выходом переноса одноразрядного сумматора оказывается наименьшее число логических уровней;

· сумматоры с двухпроводной передачей сигналов переноса;

· сумматоры с условным переносом (вариант сумматора с групповой структурой, позволяющий уменьшить время суммирования в 2 раза при увеличении оборудования в 1,5 раза);

· асинхронные сумматоры, вырабатывающие признак завершения операции суммирования, при этом среднее время суммирования уменьшается, поскольку оно существенно меньше максимального.

Сумматоры, которые имеют постоянное время, отводимое для суммирования, независимое от значений слагаемых, называют синхронными.

По способу выполнения операции сложения и возможности сохранения результата сложения можно выделить три основных вида сумматоров:

· комбинационный, выполняющий микрооперацию “S = A плюс B”, в котором результат выдаётся по мере его образования (это комбинационная схема в общепринятом смысле слова);

· сумматор с сохранением результата “S = A плюс B”;

· накапливающий, выполняющий микрооперацию “S = S плюс B”.

Последние две структуры строятся либо на счётных триггерах (сейчас практически не используются), либо по структуре “комбинационный сумматор – регистр хранения” (сейчас наиболее употребляемая схема).

Важнейшими параметрами сумматоров являются:

· разрядность;

· статические параметры: Uвх, Uвх, Iвх и так далее, то есть обычные параметры интегральных схем;

· динамические параметры. Сумматоры характеризуются четырьмя задержками распространения:

· от подачи входного переноса до установления всех выходов суммы при постоянном уровне на всех входах слагаемых;

· от одновременной подачи всех слагаемых до установления всех выходов суммы при постоянном уровне на входе переноса;

· от подачи входного переноса до установления выходного переноса при постоянном уровне на входах слагаемых;

· от подачи всех слагаемых до установления выходного переноса при постоянном уровне на входах слагаемых.

Четвертьсумматор

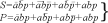

Простейшим двоичным суммирующим элементом является четвертьсумматор. Происхождение названия этого элемента следует из того, что он имеет в два раза меньше выходов и в два раза меньше строк в таблице истинности по сравнению с полным двоичным одноразрядным сумматором. Наиболее известны для данной схемы названия: элемент “сумма по модулю 2” и элемент “исключающее ИЛИ”. Схема (рис. 4) имеет два входа а и b для двух слагаемых и один выход S для суммы. Работу её отражает таблица истинности 1 (табл. 2), а соответствующее уравнение имеет вид

|

|

(5) |

|

Рис. 4 |

Таблица 2

|

Данный элемент выпускается в виде интегральных схем (ИС) типа ЛП5 (серии 133, 155, 530, 531, 533, 555, 1531, 1533); ЛП12 (555); ЛП107 (100, 500, 1500); ЛП2 (561, 564); ЛП14 (1561) и т. п.

Реализуем четвертьсумматор в базисах И-НЕ, ИЛИ-НЕ и с использованием только одного инвертора, для чего преобразуем уравнение (5):

(6)

(6)

![]()

(7) |

||

|

|

(8) |

|

Схемы, полученные по уравнениям (6)–(8), приведены на рис. 5.

![]()

Рис. 5

Полусумматор (рис. 6) имеет два входа a и b для двух слагаемых и два выхода: S — сумма, P — перенос. Обозначением полусумматора служат буквы HS (half sum — полусумма). Работу его отражает таблица истинности 2 (табл. 3), а соответствующие уравнения имеют вид:

|

|

(9) |

|

Рис. 6 |

Таблица 3

|

Из уравнений (9) следует, что для реализации полусумматора требуется один элемент “исключающее ИЛИ” и один двухвходовый вентиль И (рис. б).

Полный одноразрядный двоичный сумматор

Он (рис. 7) имеет три входа: a, b — для двух слагаемых и p — для переноса из предыдущего (более младшего) разряда и два выхода: S — сумма, P — перенос в следующий (более старший) разряд. Обозначением полного двоичного сумматора служат буквы SM. Работу его отражает таблица истинности 3 (табл. 4).

|

Рис. 7 |

Таблица 4

|

Уравнения, описывающие работу полного двоичного сумматора, представленные в совершенной дизъюнктивной нормальной форме (СДНФ), имеют вид:

(10)

(10)

Уравнение для переноса может быть минимизировано:

P = ab + ap + bp. (11)

При практическом проектировании сумматора уравнения (10) и (11) могут быть преобразованы к виду, удобному для реализации на заданных логических элементах с некоторыми ограничениями (по числу логических входов и др.) и удовлетворяющему предъявляемым к сумматору требованиям по быстродействию.

Например, преобразуем уравнения (10) следующим образом:

|

|

(12) |

Из выражений (12) следует, что полный двоичный сумматор может быть реализован на двух полусумматорах и одном двухвходовом элементе ИЛИ. Соответствующая схема приведена на рис. 8.

Рис. 8

Из выражения (12) для S также следует: S = a b p. (13)

Примечание. Так как операция Е в выражении (13) коммутативна (переменные можно менять местами), то следует, что три входа полного двоичного сумматора абсолютно равноправны и на любой из них можно подавать любую входную переменную. Это полезно помнить, разводя печатные платы, на которых установлены ИС сумматоров.

К настоящему времени разработано большое число схем сумматоров. Доказано (нашим отечественным ученым Вайнштейном), что при использовании только одного инвертора нельзя реализовать полный двоичный сумматор со сложностью Pкв < 16, а при двух инверторах — Pкв < 14, где Pкв — вес по Квайну, используемый как оценка сложности любых комбинационных схем. Pкв — это общее число всех входов всех логических элементов схемы без учёта инверторов.

Регистры

Регистр - последовательное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними.

Регистр представляет собой упорядоченную последовательность триггеров, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами. Фактически любое цифровое устройство можно представить в виде совокупности регистров, соединенных друг с другом при помощи комбинационных цифровых устройств.

Регистры классифицируются по следующим видам:

1. Параллельные или накопительные (регистры памяти, хранения);

2. Последовательные или сдвигающие.

В свою очередь сдвигающие регистры делятся:

· по способу ввода-вывода информация: параллельные; последовательные; комбинированные;

· по направлению передачи информации: однонаправленные; реверсивные.

Типичными являются следующие операции:

· прием слова в регистр;

· передача слова из регистра;

· поразрядные логические операции;

· сдвиг слова влево или вправо на заданное число разрядов;

· преобразование последовательного кода слова в параллельный и обратно;

· установка регистра в начальное состояние (сброс)

Элементарной ячейкой электронной памяти является триггер, способный сохранять 1 бит записанной в нем информации. Регистром называется устройство из триггеров, предназначенное для записи, хранения и выдачи информации. Каждый разряд двоичного числа записывается в своем триггере, поэтому число триггеров в регистре определяет разрядность записываемого числа. Наиболее распространенным видом регистров являются регистры сдвига.

Регистры сдвига.

Регистром сдвига называют цифровую схему, состоящую из последовательно включенных триггеров, содержимое которых можно сдвигать на один разряд влево или вправо подачей тактовых импульсов. Регистры сдвига широко применяются в цифровой вычислительной технике для преобразования последовательного кода в параллельный или параллельного в последовательный, а также при построении арифметико-логических устройств. Составляется регистр сдвига из соединенных последовательно триггеров, в которые записываются разряды обрабатываемого кода. При наличии разрешающих сигналов импульс, приходящий на тактовый вход регистра, вызывает перемещение записанной информации на один разряд влево или вправо. На рис. 9 приведена структурная схема регистра сдвига на синхронных JK-триггерах.

Рис. 9 Регистр сдвига на JK - триггерах.

Рассмотрим действие регистра при записи в него числа 0011, начиная с правого - младшего - разряда. До записи числа все триггеры устанавливают в нулевое состояние. Затем на вход схемы подается серия импульсов, соответствующая записываемому числу, а на вход С подаются тактовые импульсы. Сначала на вход поступает импульс, соответствующий первому из записываемых разрядов. В конце тактового импульса он дает Q3 = 1 на выходе левого триггера. В конце следующего тактового импульса информационный импульс продвигается на выход следующего триггера и т. д. Одновременно продвигаются вправо и другие цифры записываемого числа. После прихода четырех тактовых импульсов все число оказывается записанным в четырех триггерах, причем старший разряд числа записи в левом триггере, а младший - в правом. Чтобы записанная информация сохранилась, дальнейший сдвиг прекращается. Это осуществляется прекращением подачи тактовых импульсов. Описанный регистр называется регистром сдвига с последовательным приемом информации. Выдача информации у него может быть как параллельной, так и последовательной. При параллельной выдаче информация снимается одновременно с выходов всех триггеров. Последовательная выдача осуществляется с выхода Q0 при последующих тактовых импульсах. Параллельный прием информации может быть осуществлен подачей ее на выводы предустановки. Мы рассмотрели работу простейшего регистра, осуществляющего сдвиг в одну сторону. Существуют реверсивные регистры сдвига, переключаемые на сдвиг вправо и влево. Если 0 и 1 в регистре трактовать как двоичную запись числа, то сдвиг в одну сторону соответствует делению на 2, а в другую - умножению на 2. Как известно, умножение двух десятичных чисел "столбиком" соответствует сложению частных произведений, сдвинутых поразрядно влево. Аналогично столбиком перемножаются и двоичные числа, но эта операция выполняется проще, так как частные произведения получаются умножением единиц и нулей умножаемого числа на единицы и нули множителя. Следовательно, умножение сводится к операции сложения сдвинутых поразрядно двоичных чисел. Аналогично осуществляется и деление двоичных чисел.

Регистр К155ИР1

Схемотехнику регистров сдвига рассмотрим на примере регистра К155ИР1, упрощенная функциональная схема и условное обозначение которого показано на рис. 10.

Рис. 10. Схема и обозначение регистра сдвига К155ИР1.

Этот регистр содержит четыре тактируемых фронтом D-триггера, соединенных последовательно с помощью ячеек И-ИЛИ. Если на вход V (вывод 6) регистра подан потенциал "нуль", то выход каждого предыдущего триггера оказывается соединенным через ячейку И-ИЛИ со входом D последующего. При этом импульсы, приходящие на тактовый вход C2, будут каждый раз устанавливать последующий триггер в состояние, в котором до этого находился предыдущий. Таким образом осуществляется сдвиг информации вправо. Вход I регистра, связанный со входом D первого триггера, служит для приема информации в виде последовательного кода. С каждым тактовым импульсом на этот вход должен подаваться код нового разряда входной информации. После приема четырех разрядов последовательного кода соответствующий параллельный код может быть получен с выходов триггеров Q1-Q4. Запись параллельного кода в регистр идет по входам D1-D4 при подаче потенциала "I" на вход V и тактового импульса на вход C1. Устанавливая затем V=0 и подавая тактовые импульсы на вход С2, мы обеспечим сдвиг записанного кода. При этом с выхода Q4 последнего триггера снимается последовательный выходной код. Иногда требуется производить в регистре сдвиг информации как вправо, так и влево. В рассматриваемом устройстве такая возможность появляется, если попарно соединить выводы Q4 и D3, Q3 и D2, Q2 и D1. Вход V в этом случае будет играть роль переключателя направления сдвига: если V=1, то тактовые импульсы С1 сдвигают информацию влево, а вход D4 служит для приема последовательного кода; если же V=0, то, как указывалось выше, импульсы С2 будут сдвигать информацию вправо.

Мультиплексор

Мультиплексор — комбинационное устройство, обеспечивающее передачу в желаемом порядке цифровой информации, поступающей по нескольким входам на один выход.

Мультиплексоры

обозначают сочетанием MUX (от англ. multiplexor), а также MS

(от англ. multiplexor selector). Схематически мультиплексор можно

изобразить в виде коммутатора, обеспечивающего подключение одного из нескольких

входов (их называют информационными) к одному выходу устройства. Кроме

информационных входов в мультиплексоре имеются адресные входы и, как правило,

разрешающие (стробирующие). Сигналы на адресных входах определяют, какой

конкретно информационный канал подключен к выходу. Если между числом

информационных входов ![]() и числом адресных

входов действует соотношение

и числом адресных

входов действует соотношение ![]() , то такой

мультиплексор называют полным. Если

, то такой

мультиплексор называют полным. Если ![]() , то

мультиплексор называют неполным. Разрешающие входы используют для расширения

функциональных возможностей мультиплексора. Они используются для наращивания

разрядности мультиплексора, синхронизации его работы с работой других узлов.

Сигналы на разрешающих входах могут разрешать, а могут и запрещать подключение

определенного входа к выходу, то есть могут блокировать действие всего

устройства. Мультиплексоры являются универсальными логическими устройствами, на

основе которых создают различные комбинационные и последовательностные схемы.

Мультиплексоры могут использоваться в делителях частоты, триггерных

устройствах, сдвигающих устройствах и др. Мультиплексоры часто используют для

преобразования параллельного двоичного кода в последовательный. Для такого

преобразования достаточно подать на информационные входы мультиплексора

параллельный двоичный код, а сигналы на адресные входы подавать в такой

последовательности, чтобы к выходу поочередно подключались входы, начиная с

первого и заканчивая последним.

, то

мультиплексор называют неполным. Разрешающие входы используют для расширения

функциональных возможностей мультиплексора. Они используются для наращивания

разрядности мультиплексора, синхронизации его работы с работой других узлов.

Сигналы на разрешающих входах могут разрешать, а могут и запрещать подключение

определенного входа к выходу, то есть могут блокировать действие всего

устройства. Мультиплексоры являются универсальными логическими устройствами, на

основе которых создают различные комбинационные и последовательностные схемы.

Мультиплексоры могут использоваться в делителях частоты, триггерных

устройствах, сдвигающих устройствах и др. Мультиплексоры часто используют для

преобразования параллельного двоичного кода в последовательный. Для такого

преобразования достаточно подать на информационные входы мультиплексора

параллельный двоичный код, а сигналы на адресные входы подавать в такой

последовательности, чтобы к выходу поочередно подключались входы, начиная с

первого и заканчивая последним.

Мультиплексор — устройство, имеющее несколько сигнальных входов, один или более управляющих входов и один выход. Мультиплексор позволяет передать сигнал с одного из входов на выход; при этом выбор желаемого входа осуществляется подачей соответствующей комбинации управляющих сигналов.

Аналоговые и цифровые мультиплексоры значительно различаются по принципу работы. Первые электрически соединяют выбранный вход с выходом (при этом сопротивление между ними невелико — порядка единиц/десятков Ом). Вторые же не образуют прямого электрического соединения между выбранным входом и выходом, а лишь «копируют» на выход логический уровень ('0' или '1') с выбранного входа.

Обобщенная схема мультиплексора:

Обобщенная схема мультиплексора приведена на рис. 11.Мультиплексор MUX (Multiplexor) в общем случае можно представить в виде коммутатора, управляемого входной логической схемой. Входные логические сигналы Xi поступают на входы коммутатора и через коммутатор передаются на выход Y. Управление коммутатором осуществляется входной логической схемой. На вход логической схемы подаются адресные сигналы Ak (Address). Мультиплексоры могут иметь дополнительный управляющий вход E (Enable), который может выполнять стробирование выхода Y. Кроме этого некоторые мультиплексоры могут иметь выход с тремя состояниями: два состояния 0 и 1 и третье состояние — отключенный выход (выходное сопротивление равно бесконечности). Перевод мультиплексора в третье состояние производится сигналом OE (Output Enable).

3. Аналоговые, цифроаналоговые (ЦАП), аналогово-цифровые (АЦП) преобразователи. Операционный усилитель (ОУ), компаратор

Измерительные преобразователи в зависимости от вида (аналоговый, кодированный) входного и выходного сигналов относят к одной из следующих групп: а) аналоговые измерительные преобразователи, у которых на входе и выходе аналоговые сигналы; б) аналого–цифровые измерительные преобразователи, имеющие на входе аналоговый сигнал, а на выходе кодированный сигнал; в) цифроаналоговые измерительные преобразователи, у которых на входе кодированный сигнал, а на выходе аналоговый (квантовый) сигнал.

(14)

(14)

Прежде чем перейти к анализу принципа действия схем аналого-цифровых и цифроаналоговых преобразователей, коротко рассмотри" важнейший элемент интегральной техники - операционный усилитель на котором, в частности, построены современные компараторы (устройства сравнения).

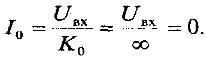

Операционные усилители. Операционным усилителем (ОУ) называют высококачественный интегральный линейный усилитель напряжения, имеющий большой коэффициент усиления (106...107), высокое входное (сотни МОм) и малое выходное (единицы Ом) сопротивления. На рис. 12, а показано условное графическое обозначение ОУ. По отношению к выходу один из входов ОУ является неинвертирующим Uн, а другой — инвертирующим Uи; последний обозначается знаком инверсии (кружок на входе ОУ). Питание ОУ осуществляется от двух одинаковых разнополярных источников +Uп и -Uп (на графических обозначениях источники питания обычно не показывают). При таком питании входные и выходные сигналы могут быть двуполярными, а нулевой входной сигналам соответствует нулевой выходной сигнал. Выходной сигнал ОУ пропорционален дифференциальному входному сигналу — разности входных Uн- Uи.

|

Рис.12. Операционный усилитель:

а – условное графическое обозначение; б – передаточные характеристики

Коэффициент усиления по напряжению К0 собственно ОУ равен отношению выходного напряжения к дифференциальному входному напряжению:

(15)

Передаточные характеристики (рис.12, б) имеют важнейшее значение для ОУ. Если усиливаемый сигнал подан на неинвертирующий вход, а инвертирующий вход заземлен, то знак выходного напряжения совпадает со знаком входного напряжения (линия 1). При подаче сигнала на инвертирующий вход и заземлении неинвертирующего, знак выходного напряжения будет противоположен знаку входного (линия 2). Угол наклона линейных участков передаточных характеристик пропорционален коэффициенту усиления по напряжению К0. Горизонтальные участки передаточных характеристик соответствуют режиму насыщения оконечных транзисторов ОУ, поэтому выходное напряжение

![]() (16)

(16)

В теории интегральной усилительной техники с целью упрощения анализа и расчета схем на операционных усилителях вводят понятие «идеальный» ОУ, для которого справедливы следующие допущения: бесконечно большие коэффициент усиления К0 = оо, входное сопротивление Rвх0 = оо и нулевое выходное сопротивление Rвых0 = 0.

Из этих допущений вытекают два основных свойства (правила анализа) ОУ:

1. Дифференциальный входной сигнал равен нулю

(17)

2. Входы ОУ не потребляют ток от источника входного сигнала

(18)

Изложенное выше понятие идеального ОУ соответствует так называемому принципу «виртуального» (кажущегося) замыкания его инвертирующего и неинвертирующего входов. При виртуальном замыкании, как и при физическом (обычном), напряжение между соединенными зажимами равно нулю. Вместе с тем в отличие от физического замыкания ток между виртуально замкнутыми зажимами не течет. Говоря другим словами, для тока виртуальное замыкание зажимов эквивалентно разрыву электрической цепи.

В зависимости от условий подачи усиливаемого сигнала на входы ОУ и подключения к нему внешних элементов можно получить две фундаментальные схемы включения: инвертирующую и неинвертирующую. Любое схемотехническое решение с применением ОУ базируется на этих включениях. Одно из них осуществлено в компараторе.

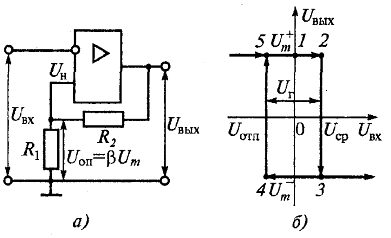

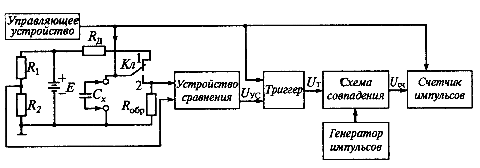

Компаратор — устройство, осуществляющее сравнение двух аналоговых напряжений. В простейшей схеме компаратора входное напряжение сравнивается с некоторым опорным, в качестве которого используется часть выходного напряжения (рис. 14, а).

На инвертирующий вход ОУ поступает входное напряжение, а на неинвертирующий вход подается опорное напряжение Uн= Uon = βUm, снимаемое с делителя R1,R2. Таким образом, ОУ охвачен положительной обратной связью по неинвертирующему входу, и выходное напряжение скачком изменяет свою полярность при сравнении входного и опорного напряжений.

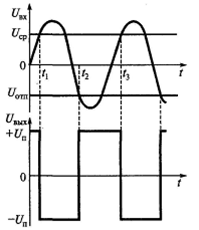

Принцип действия компаратора рассмотрим с помощью передаточной характеристики —

зависимости выходного напряжения от входного (рис.5, б). Пусть входное напряжение UBX = 0, а выходное Uвых= Um+ (точка 1 на рис 5,б). Напряжение на неинвентирующем входе при этом будет:

Uн = βUm+ (19)

где р = Rl/(Rl+R2) — коэффициент передачи резистивной цепи Rt, R2 положительной ОС в компараторе.

Если входное напряжение больше нуля и увеличивается, то при сравнении его амплитуды с опорным, равным напряжению срабатывания U=βUm+, компаратор переключается. При этом произойдет скачкообразное изменение выходного напряжения со значения Um+, на значение U-(переход от точки 2 к точке 3 на рис. 14, б). Дальнейшее увеличение, входного напряжения не изменит состояния компаратора, и напряжение на неинвертирующем входе ОУ будет также постоянным: Uн=βUm-, При уменьшении входного напряжения до значения опорного, равного напряжению отпускания Uвх = Uотп = βUm-, произойдет скачкообразный возврат компаратора в исходное состояние. Выходное напряжение при этом изменится с Um- на βUm+, (переход от точки 4 к точке 5 на рис. 5, б).

|

Рис.14. Компаратор

а – схема; б- передаточная характеристика

Таким образом, передаточная характеристика компаратора имеет вид петли гистерезиса. Такой компаратор обладает триггерным (переключающим) эффектом, и в радиоэлектронике его называют триггером Шмитта. Сумма напряжений срабатывания и отпускания является напряжением гистерезиса.

![]()

(20)

Рис.15.Формирование меандра из синусоиды компаратором

Оно вводится для повышения помехоустойчивости, что позволяет устранить «дребезг» триггера, т.е. случайное его переключение напряжением помех при отсутствии входного сигнала. В компараторе на ОУ амплитуда выходного напряжения практически равна напряжению питания: Uвых = Um± = ±Uп. Компараторы применяют для формирования сигналов прямоугольной формы из различных видов непрерывных сигналов. В частности, при подаче на вход компаратора синусоидального напряжения (рис. 15), на его выходе формируется симметричное прямоугольное колебание — меандр (греч. —узор — геометрический орнамент).

Пусть в момент времени t = 0 напряжение на выходе компаратора Uвых = Um+. В таком состоянии компаратор будет находиться, пока амплитуда входного напряжения UBX < Uср. В момент времени t = tt входное напряжение станет UBX = Uср, и компаратор переключится. При этом выходное напряжение Uвых скачком изменится со значения Um+ на значение Um-. В момент времени t = t2 входное напряжение станет равным Uотп, и произойдет повое переключение компаратора.

3.1 Цифроаналоговые преобразователи

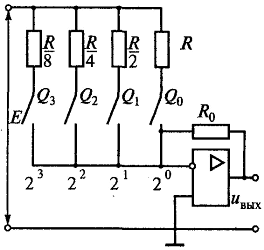

Принцип действия четырехразрядного цифроаналогового преобразователя иллюстрируется с помощью простейшей схемы на ОУ, представленной на рис. 16. Основу схемы составляет матрица резисторов с источником постоянного напряжения, соединенных с инвертирующим входом ОУ ключами, которые управляются двоичным кодом (например, выходным кодом счетчика).

В зависимости от поступающего кода цифрового сигнала подключаются резисторы с различными номиналами сопротивлений. В схеме ключи замыкаются только при поступлении на них команд, соответствующих логической единице. Коэффициенты усиления инвертирующего усилителя по входам 2°, 21, 22 и 23 соответственно равны

(21) K0 = -R0 Qo / R; K1 = -2R0 Q1 / R; К2 = - 4R0 Q2 / R; K3 = -8R0 Q 3 / R

Здесь Qo, Q1, Q2, Q 3 — кодовые числа, принимающие два значения: либо 1 (ключ замкнут), либо 0 (ключ разомкнут).

Из формулы 21 следует, что четырехразрядный двоичный код преобразуется в выходное напряжение, изменяющееся по амплитуде от 0 до 15∆ (напомним, что ∆ — шаг квантования). Например, двоичному числу 1001 соответствует напряжение uвых1 = ∆ (1.1 + 2.0 + 4. 0 + 8. 1) = 9∆, а числу 1100 – uвых2 = 12 ∆. Поскольку на вход резистивной матрицы подается постоянное напряжение Е, то выходное напряжение ЦАП изменяется скачками при переключении кода цифрового сигнала. Сглаживание выходного сигнала осуществляется фильтром низкой частоты (ФНЧ).

|

Рис.16. Схема четырехразрядного ЦАП

Аналого-цифровые преобразователи.

По своей структуре аналого-цифровые преобразователи (АЦП) более сложны, чем ЦАП, причем последние часто являются основным узлом АЦП. В настоящее время существуют три различных метода построения схем АЦП: последовательный, параллельный и последовательно-параллельный.

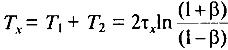

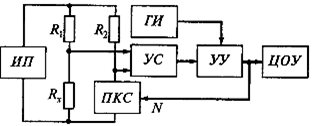

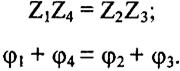

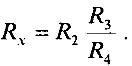

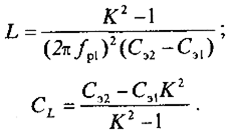

Последовательный (последовательного счета) метод построения АЦП (рис.17) основан на подсчете числа суммирований опорного напряжения младшего разряда, необходимого для получения напряжения, равного входному.

При этом k - разрядный двоичный код одного отсчета определяется в схеме за 2k интервалов дискретизации.

Начало преобразования входного непрерывного сигнала определяется временем поступления импульса запуска, который через.RS-триггер Т подключает счетчик Ст2 к выходу генератора тактовых (счетных) импульсов М. Схема ЦАП D/A, куда поступает цифровой код со счетчика, формирует выходное напряжение uвых, которое сравнивается в компараторе К с входным напряжением uвх. При сравнении этих напряжений, компаратор через логический элемент И (&) выдает сигнал прекращения подачи на счетчик Ст2 тактовых импульсов. В результате осуществляется считывание со счетчика выходного четырехразрядного кода, представляющего в момент окончания преобразования цифровой эквивалент выходного напряжения.

В описанном АЦП значения выходного цифрового кода в процессе преобразования многократно изменяются, поэтому он обладает низким быстродействием.

|

Рис.17.Упрощенная структурная схема АЦП последовательного счета.

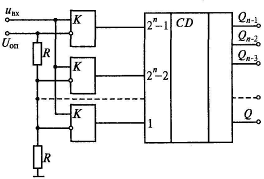

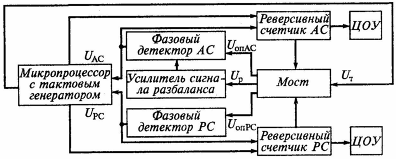

Действие параллельных (по методу считывания) k-разрядных АЦП основано на использовании 2k-1 компараторов (рис.18). Неинвертирующие входы операционных усилителей компараторов объединены, и на них подается непрерывный сигнал, а к каждому инвертирующему входу подключено индивидуальное опорное напряжение, снимаемое с резистивного делителя. Разность между опорным напряжением двух соседних компараторов равна шагу квантования ∆ = U0п / 2k. Компараторы, у которых входное напряжение превысит соответствующее опорное напряжение, вырабатывают логическую 1, а остальные - логический 0. Информация с выходов компараторов поступает на шифратор CD, который преобразует ее в двоичный код.

Параллельные схемы обладают наибольшим быстродействием среди других типов АЦП. Однако для повышения точности измерений и уменьшения мощности шумов квантования в параллельных АЦП требуется увеличение числа компараторов.

Рис.18. Структурная схема параллельного АЦП

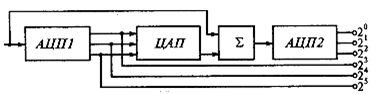

В последовательно-параллельных схемах АЦП используется сочетание методов последовательного и параллельного преобразования сигналов, что существенно увеличивает быстродействие последовательных преобразователей и уменьшает объем параллельных.

На рис.19. показана структурная схема шестиразрядного аналого-цифрового преобразователя данного типа, в которой используются два трехразрядных параллельных АЦП, один трехразрядный ЦАП и сумматор ∑.

|

Рис.19. Структурная схема последовательно- параллельного АЦП

Аналого-цифровой преобразователь формирует из входного напряжения три старших разряда выходного кода, соответствующие значениям 23, 24, и 25. Эти разряды поступают на вход трехразрядного ЦАП, в котором они вновь преобразуются в аналоговое напряжение, отличающееся от входного напряжения uвх на величину погрешности преобразования схемы АЦП1. Аналоговое напряжение с выхода схемы ЦАП подается на сумматор ∑, где оно вычитается из входного напряжения uвх. Полученное разностное напряжение подается на АЦП2, в котором оно преобразуется в три младших цифровых разряда22, 21, 2° выходного кода преобразователя.

В заключение отметим следующее. Перспективным направлением развития ЦИП является применение микропроцессоров, которые обеспечивают управление процессом измерения, самодиагностику, автоматическую градуировку по заданной программе, а также первичную обработку результатов измерения (линеаризацию функции преобразования, коррекцию погрешностей, сжатие данных, т.е. уменьшение избыточности измеряемой информации). В настоящее время элементной базой ЦИП являются аналоговые и цифровые интегральные микросхемы, что позволяет достигнуть высокого быстродействия и малых габаритных размеров приборов. Применение интегральных микросхем большой степени интеграции значительно расширило функциональные возможности ЦИП и повысило их надежность при одновременном снижении потребления энергии. Многие ЦИП имеют автоматический выбор пределов измерения, повышающий точность измерения при большом динамическом диапазоне входного сигнала. Большинство ЦИП могут выполнять операции интегрирования и фильтрации, что значительно повышает их помехоустойчивость.

В последние годы получили применение аналого-дискретные измерительные приборы (АДИП). В отличие от ЦИП в них используют квазианалоговые отсчетные устройства, в которых роль указателя выполняет светящаяся полоса или светящаяся точка, меняющие дискретно свою длину (полоса) или положение (точка) относительно шкалы. Квазианалоговые отсчетные устройства управляются кодом. Такие приборы сочетают в себе достоинства аналоговых приборов (аналоговые отсчетные устройства) и ЦИП (код на выходе).

В настоящее время сформировалось новое направление в метрологии и электроизмерительной технике — компьютерно-измерительные системы (КИС) и их разновидность — виртуальные приборы.

4. Микропроцессоры и микроЭВМ

Микропроцессор - процессор, выполненный в виде одной либо нескольких взаимосвязанных интегральных схем. Микропроцессор состоит из цепей управления, регистров, сумматоров, счетчиков команд и очень быстрой памяти малого объема.

Некоторые микропроцессоры дополняются сопроцессорами, расширяющими возможности микропроцессоров и набор выполняемых команд.

4.1 Основные характеристики микропроцессора

Микропроцессор характеризуется:

1) тактовой частотой, определяющей максимальное время выполнения переключения элементов в ЭВМ;

2) разрядностью, т.е. максимальным числом одновременно обрабатываемых двоичных разрядов. Разрядностть МП обозначается m/n/k/ и включает:

m - разрядность внутренних регистров, определяет принадлежность к тому или иному классу процессоров;

n - разрядность шины данных, определяет скорость передачи информации;

k - разрядность шины адреса, определяет размер адресного пространства. Например, МП i8088 характеризуется значениями m/n/k=16/8/20;

3) архитектурой. Понятие архитектуры микропроцессора включает в себя систему команд и способы адресации, возможность совмещения выполнения команд во времени, наличие дополнительных устройств в составе микропроцессора, принципы и режимы его работы. Выделяют понятия микроархитектуры и макроархитектуры.

Микроархитектура микропроцессора - это аппаратная организация и логическая структура микропроцессора, регистры, управляющие схемы, арифметико-логические устройства, запоминающие устройства и связывающие их информационные магистрали.

Макроархитектура - это система команд, типы обрабатываемых данных, режимы адресации и принципы работы микропроцессора.

В общем случае под архитектурой ЭВМ понимается абстрактное представление машины в терминах основных функциональных модулей, языка ЭВМ, структуры данных. Структура типового микропроцессора

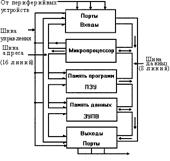

Архитектура типичной небольшой вычислительной системы на основе микроЭВМ показана на рис. 20. Такая микроЭВМ содержит все 5 основных блоков цифровой машины: устройство ввода информации, управляющее устройство (УУ), арифметико-логическое устройство (АЛУ) (входящие в состав микропроцессора), запоминающие устройства (ЗУ) и устройство вывода информации. Микропроцессор координирует работу всех устройств цифровой системы с помощью шины управления (ШУ). Помимо ШУ имеется 16-разрядная адресная шина (ША), которая служит для выбора определенной ячейки памяти, порта ввода или порта вывода. По 8-разрядной информационной шине или шине данных (ШД) осуществляется двунаправленная пересылка данных к микропроцессору и от микропроцессора. Важно отметить, что МП может посылать информацию в память микроЭВМ или к одному из портов вывода, а также получать информацию из памяти или от одного из портов ввода. Постоянное запоминающее устройство (ПЗУ) в микроЭВМ содержит некоторую программу (на практике программу инициализации ЭВМ). Программы могут быть загружены в запоминающее устройство с произвольной выборкой (ЗУПВ) и из внешнего запоминающего устройства (ВЗУ). Это программы пользователя

Рис. 20. Архитектура типового микропроцессора

В качестве примера, иллюстрирующего работу микроЭВМ, рассмотрим процедуру, для реализации которой нужно выполнить следующую последовательность элементарных операций:

1.Нажать клавишу с буквой "А" на клавиатуре.

2. Поместить букву "А" в память микроЭВМ.

3. Вывести букву "А" на экран дисплея.

Это типичная процедура ввода-запоминания-вывода, рассмотрение которой дает возможность пояснить принципы использования некоторых устройств, входящих в микроЭВМ.

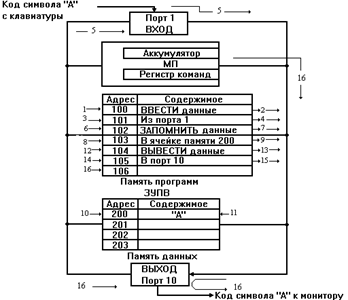

На рис. 21 приведена подробная диаграмма выполнения процедуры ввода-запоминания-вывода. Обратите внимание, что команды уже загружены в первые шесть ячеек памяти. Хранимая программа содержит следующую цепочку команд:

1. Ввести данные из порта ввода 1.

2. Запомнить данные в ячейке памяти 200.

3. Переслать данные в порт вывода 10.

Рис. 21. Диаграмма выполнения процедуры ввода-запоминания-вывода.

В данной программе всего три команды, хотя на рис. 21 может показаться, что в памяти программ записано шесть команд. Это связано с тем, что команда обычно разбивается на части. Первая часть команды 1 в приведенной выше программе - команда ввода данных. Во второй части команды 1 указывается, откуда нужно ввести данные (из порта 1). Первая часть команды, предписывающая конкретное действие, называется кодом операции (КОП), а вторая часть - операндом. Код операции и операнд размещаются в отдельных ячейках памяти программ. На рис. 21 КОП хранится в ячейке 100, а код операнда - в ячейке 101 (порт 1); последний указывает откуда нужно взять информацию.

В МП на рис. 21 выделены еще два новых блока - регистры: аккумулятор и регистр команд. Рассмотрим прохождение команд и данных внутри микроЭВМ с помощью занумерованных кружков на диаграмме. Напомним, что микропроцессор - это центральный узел, управляющий перемещением всех данных и выполнением операций.

Итак, при выполнении типичной процедуры ввода-запоминания-вывода в микроЭВМ происходит следующая последовательность действий:

1. МП выдает адрес 100 на шину адреса. По шине управления поступает сигнал, устанавливающий память программ (конкретную микросхему) в режим считывания.

2. ЗУ программ пересылает первую команду ("Ввести данные") по шине данных, и МП получает это закодированное сообщение. Команда помещается в регистр команд. МП декодирует (интерпретирует) полученную команду и определяет, что для команды нужен операнд.

3. МП выдает адрес 101 на ША; ШУ используется для перевода памяти программ в режим считывания.

4. Из памяти программ на ШД пересылается операнд "Из порта 1". Этот операнд находится в программной памяти в ячейке 101. Код операнда (содержащий адрес порта 1) передается по ШД к МП и направляется в регистр команд. МП теперь декодирует полную команду ("Ввести данные из порта 1").

5. МП, используя ША и ШУ, связывающие его с устройством ввода, открывает порт 1. Цифровой код буквы "А" передается в аккумулятор внутри МП и запоминается. Важно отметить, что при обработке каждой программной команды МП действует согласно микропроцедуре выборки-декодирования-исполнения.

6. МП обращается к ячейке 102 по ША. ШУ используется для перевода памяти программ в режим считывания.

7. Код команды "Запомнить данные" подается на ШД и пересылается в МП, где помещается в регистр команд.

8. МП дешифрирует эту команду и определяет, что для нее нужен операнд. МП обращается к ячейке памяти 103 и приводит в активное состояние вход считывания микросхем памяти программ.

9. Из памяти программ на ШД пересылается код сообщения "В ячейке памяти 200". МП воспринимает этот операнд и помещает его в регистр команд. Полная команда "Запомнить данные в ячейке памяти 200" выбрана из памяти программ и декодирована.

10. Теперь начинается процесс выполнения команды. МП пересылает адрес 200 на ША и активизирует вход записи, относящийся к памяти данных.

11. МП направляет хранящуюся в аккумуляторе информацию в память данных. Код буквы "А" передается по ШД и записывается в ячейку 200 этой памяти. Выполнена вторая команда. Процесс запоминания не разрушает содержимого аккумулятора. В нем по-прежнему находится код буквы "А".

12. МП обращается к ячейке памяти 104 для выбора очередной команды и переводит память программ в режим считывания.

13. Код команды вывода данных пересылается по ШД к МП, который помещает ее в регистр команд, дешифрирует и определяет, что нужен операнд.

14. МП выдает адрес 105 на ША и устанавливает память программ в режим считывания.

15. Из памяти программ по ШД к МП поступает код операнда "В порт 10", который далее помещается в регистр команд.

16. МП дешифрирует полную команду "Вывести данные в порт 10". С помощью ША и ШУ, связывающих его с устройством вывода, МП открывает порт 10, пересылает код буквы "А" (все еще находящийся в аккумуляторе) по ШД. Буква "А" выводится через порт 10 на экран дисплея.

В большинстве микропроцессорных систем (МПС) передача информации осуществляется способом, аналогичным рассмотренному выше. Наиболее существенные различия возможны в блоках ввода и вывода информации. Подчеркнем еще раз, что именно микропроцессор является ядром системы и осуществляет управление всеми операциями. Его работа представляет последовательную реализацию микропроцедур выборки-дешифрации-исполнения. Однако фактическая последовательность операций в МПС определяется командами, записанными в памяти программ.

Таким образом, в МПС микропроцессор выполняет следующие функции:

- выборку команд программы из основной памяти;

- дешифрацию команд;

- выполнение арифметических, логических и других операций, закодированных в командах;

- управление пересылкой информации между регистрами и основной памятью, между устройствами ввода/вывода;

- отработку сигналов от устройств ввода/вывода, в том числе реализацию прерываний с этих устройств;

- управление и координацию работы основных узлов МП.

4.2 Логическая структура микропроцессора

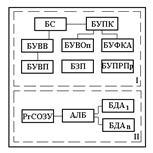

Логическая структура микропроцессора, т. е. конфигурация составляющих микропроцессор логических схем и связей между ними, определяется функциональным назначением. Именно структура задает состав логических блоков микропроцессора и то, как эти блоки должны быть связаны между собой, чтобы полностью отвечать архитектурным требованиям. Срабатывание электронных блоков микропроцессора в определенной последовательности приводит к выполнению заданных архитектурой микропроцессора функций, т. е. к реализации вычислительных алгоритмов. Одни и те же функции можно выполнить в микропроцессорах со структурой, отличающейся набором, количеством и порядком срабатывания логических блоков. Различные структуры микропроцессоров, как правило, обеспечивают их различные возможности, в том числе и различную скорость обработки данных. Логические блоки микропроцессора с развитой архитектурой показаны на рис. 22

Рис. 22. Общая логическая структура микропроцессора: I - управляющая часть, II - операционная часть; БУПК - блок управления последовательностью команд; БУВОп - блок управления выполнением операций; БУФКА - блок управления формированием кодов адресов; БУВП - блок управления виртуальной памятью; БЗП - блок защиты памяти; БУПРПр - блок управления прерыванием работы процессора; БУВВ - блок управления вводом/выводом; РгСОЗУ - регистровое сверхоперативное запоминающее устройство; АЛБ - арифметико-логический блок; БДА - блок дополнительной арифметики; БС - блок синхронизации.

При проектировании логической структуры микропроцессоров необходимо рассмотреть:

1) номенклатуру электронных блоков, необходимую и достаточную для реализации архитектурных требований;

2) способы и средства реализации связей между электронными блоками;

3) методы отбора если не оптимальных, то наиболее рациональных вариантов логических структур из возможного числа структур с отличающимся составом блоков и конфигурацией связей между ними.

При проектировании микропроцессора приводятся в соответствие внутренняя сложность кристалла и количество выводов корпуса. Относительный рост числа элементов по мере развития микроэлектронной технологии во много раз превышает относительное увеличение числа выводов корпуса, поэтому проектирование БИС в виде конечного автомата, а не в виде набора схем, реализующих некоторый набор логических переключательных функций и схем памяти, дает возможность получить функционально законченные блоки и устройства ЭВМ.

Использование микропроцессорных комплектов БИС позволяет создать микроЭВМ для широких областей применения вследствие программной адаптации микропроцессора к конкретной области применения: изменяя программу работы микропроцессора, изменяют функции информационно-управляющей системы. Поэтому за счет составления программы работы микропроцессоров в конкретных условиях работы определенной системы можно получить оптимальные характеристики последней.

Если уровень только программной "настройки" микропроцессоров не позволит получить эффективную систему, доступен следующий уровень проектирования - микропрограммный. За счет изменения содержимого ПЗУ или программируемой логической матрицы (ПЛМ) можно "настроиться" на более специфичные черты системы обработки информации. В этом случае частично за счет изменения микропрограмм затрагивается аппаратный уровень системы. Технико-экономические последствия здесь связаны лишь с ограниченным вмешательством в технологию изготовления управляющих блоков микроЭВМ.

Изменение аппаратного уровня информационно-управляющей микропроцессорной системы, включающего в себя функциональные БИС комплекта, одновременно с конкретизацией микропрограммного и программного уровней позволяет наилучшим образом удовлетворить требованиям, предъявляемым к системе.

Решение задач управления в конкретной системе чисто аппаратными средствами (аппаратная логика) дает выигрыш в быстродействии, однако приводит к сложностям при модификации системы. Микропроцессорное решение (программная логика) является более медленным, но более гибким решением, позволяющим развивать и модифицировать систему. Изменение технических требований к информационно-управляющей микропроцессорной системе ведет лишь к необходимости перепрограммирования работы микропроцессора. Именно это качество обеспечивает высокую логическую гибкость микропроцессоров, определяет возможность их широкого использования, а значит и крупносерийного производства.

По виду обрабатываемых входных сигналов различают цифровые и аналоговые микропроцессоры. Сами микропроцессоры цифровые устройства, однако могут иметь встроенные аналого-цифровые и цифро-аналоговые преобразователи. Поэтому входные аналоговые сигналы передаются в МП через преобразователь в цифровой форме, обрабатываются и после обратного преобразования в аналоговую форму поступают на выход. С архитектурной точки зрения такие микропроцессоры представляют собой аналоговые функциональные преобразователи сигналов и называются аналоговыми микропроцессорами. Они выполняют функции любой аналоговой схемы (например, производят генерацию колебаний, модуляцию, смещение, фильтрацию, кодирование и декодирование сигналов в реальном масштабе времени и т.д., заменяя сложные схемы, состоящие из операционных усилителей, катушек индуктивности, конденсаторов и т.д.). При этом применение аналогового микропроцессора значительно повышает точность обработки аналоговых сигналов и их воспроизводимость, а также расширяет функциональные возможности за счет программной "настройки" цифровой части микропроцессора на различные алгоритмы обработки сигналов.

Обычно в составе однокристальных аналоговых МП имеется несколько каналов аналого-цифрового и цифро-аналогового преобразования. В аналоговом микропроцессоре разрядность обрабатываемых данных достигает 24 бит и более, большое значение уделяется увеличению скорости выполнения арифметических операций.

Отличительная черта аналоговых микропроцессоров способность к переработке большого объема числовых данных, т. е. к выполнению операций сложения и умножения с большой скоростью при необходимости даже за счет отказа от операций прерываний и переходов. Аналоговый сигнал, преобразованный в цифровую форму, обрабатывается в реальном масштабе времени и передается на выход обычно в аналоговой форме через цифро-аналоговый преобразователь. При этом согласно теореме Котельникова частота квантования аналогового сигнала должна вдвое превышать верхнюю частоту сигнала.

Сравнение цифровых микропроцессоров производится сопоставлением времени выполнения ими списков операций. Сравнение же аналоговых микропроцессоров производится по количеству эквивалентных звеньев аналого-цифровых фильтров рекурсивных фильтров второго порядка. Производительность аналогового микропроцессора определяется его способностью быстро выполнять операции умножения: чем быстрее осуществляется умножение, тем больше эквивалентное количество звеньев фильтра в аналоговом преобразователе и тем более сложный алгоритм преобразования цифровых сигналов можно задавать в микропроцессоре.

Одним из направлений дальнейшего совершенствования аналоговых микропроцессоров является повышение их универсальности и гибкости. Поэтому вместе с повышением скорости обработки большого объема цифровых данных будут развиваться средства обеспечения развитых вычислительных процессов обработки цифровой информации за счет реализации аппаратных блоков прерывания программ и программных переходов.

По характеру временной организации работы микропроцессоры делят на синхронные и асинхронные.

Синхронные микропроцессоры - микропроцессоры, в которых начало и конец выполнения операций задаются устройством управления (время выполнения операций в этом случае не зависит от вида выполняемых команд и величин операндов).

Асинхронные микропроцессоры позволяют начало выполнения каждой следующей операции определить по сигналу фактического окончания выполнения предыдущей операции. Для более эффективного использования каждого устройства микропроцессорной системы в состав асинхронно работающих устройств вводят электронные цепи, обеспечивающие автономное функционирование устройств. Закончив работу над какой-либо операцией, устройство вырабатывает сигнал запроса, означающий его готовность к выполнению следующей операции. При этом роль естественного распределителя работ принимает на себя память, которая в соответствии с заранее установленным приоритетом выполняет запросы остальных устройств по обеспечению их командной информацией и данными.

По организации структуры микропроцессорных систем различают микроЭВМ одно- и многомагистральные.

В одномагистральных микроЭВМ все устройства имеют одинаковый интерфейс и подключены к единой информационной магистрали, по которой передаются коды данных, адресов и управляющих сигналов.

В многомагистральных микроЭВМ устройства группами подключаются к своей информационной магистрали. Это позволяет осуществить одновременную передачу информационных сигналов по нескольким (или всем) магистралям. Такая организация систем усложняет их конструкцию, однако увеличивает производительность.

По количеству выполняемых программ различают одно- и многопрограммные микропроцессоры.

В однопрограммных микропроцессорах выполняется только одна программа. Переход к выполнению другой программы происходит после завершения текущей программы.

В много- или мультипрограммных микропроцессорах одновременно выполняется несколько (обычно несколько десятков) программ. Организация мультипрограммной работы микропроцессорных управляющих систем позволяет осуществить контроль за состоянием и управлением большим числом источников или приемников информации.

4.3 Понятие о микроЭВМ на примере однокристального микроЭВМ серии К1816

МикроЭВМ этой серии разработаны для использования в качестве микроконтроллеров, для которых требуются короткие программы, небольшой объем оперативной памяти и ограниченные возможности ввода-вывода. Серия К1816 выпускается в четырех модификациях, отличающихся быстродействием, объемом программной и оперативной памяти, а также способом программирования ПЗУ (см. табл. 5). Однокристальные микроЭВМ серии К1816 размещены в 40-выводном корпусе и имеют два вывода питания +5 В, один из которых Ucc подводит питание к микроЭВМ, а другой UDD - к внутреннему ОЗУ, что позволяет сохранять в нем данные во время сбояпитания.

4.4 Архитектура микроЭВМ

Как было указано ранее, особенностью архитектуры микроконтроллера является логическое и физическое разделение памяти на программную и данных. Программная память представлена только ПЗУ, так как в К1816 отсутствуют программные средства оперативной записи команд и программ. Память может расширяться путем подключения внешних БИС: программная — на 2 Кбайта, данных — на 256 байт. Возможно также расширение средств ввода-вывода за счет использования интерфейсных БИС серии К580.

Таблица 5

| Параметр | Модификация КР1816ВЕ | |||

| 35 | 39 | 48 | 49 | |

| Тип программной памяти | - | - | ППЗУ | ПЗУ |

| Объем внутренней программной памяти, Кбайт | - | - | 1 | 2 |

| Объем ОЗУ, байт | 64 | 128 | 64 | 128 |

| Максимальная тактовая частота, МГц | 6 | 11 | 6 | 11 |

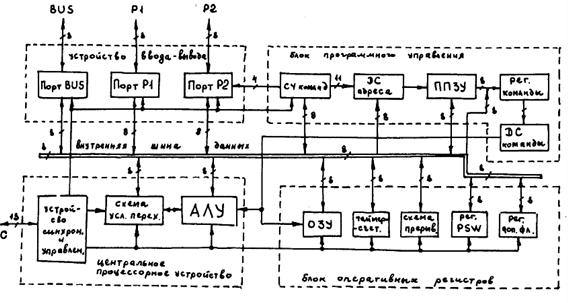

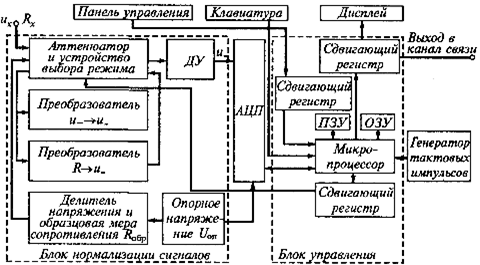

Структурная схема однокристальной ЭВМ приведена на рис. 23. Она во многом напоминает нам схему микропроцессора серии К580. Основными отличиями К1816 от МП580 являются:

1. Увеличен объем внутренней сверхоперативной памяти данных.

2. Введена память команд.

3. Введен аппаратный таймер.

4. Используется мультиплексирование данных и адреса в порту ввода/вывода.

5. Увеличено число сигналов логического воздействия на микроЭВМ.

Элементы структурной схемы могут быть объединены в четыре блока (обведены пунктирной линией):

· центральное процессорное устройство;

· блок программного управления;

· устройство ввода-вывода;

· блок оперативных регистров.

Центральное процессорное устройство включает в себя устройство синхронизации и управления, АЛУ и схему условных переходов, которая организует условные переходы по битам регистра флажков АЛУ и внешним сигналам управления ТО и Т1. АЛУ строится аналогично МП580 — оно выполняет операции накапливающего типа в двоичной и десятичной арифметике. Устройство синхронизации и управления связано с периферийными устройствами 13-разрядной шиной С {12: 0}, отдельные провода которой несут на себе следующие сигналы (в скобках указаны аналоги сигналов МП580):

BQ1, BQ2 - подключение кварца или LC — цепи синхронизации встроенного тактового генератора или входа внешнего тактового генератора;

WR (WR) — запись во внешнюю память данных, запись из порта BUS во внешнее устройство;

RD (DBIN) — чтение из внешней памяти или из внешних устройств, подключенных к порту BUS

ALE (C) (address latch enable) — стробирование внешней памяти;

SR (RESET) (set-reset) - инициализация микроЭВМ;

INT (INT) — сигнал запроса на прерывание;

SS — организация пошагового выполнения программы (используется совместно с ALE);

PME (periphery memory enable) - стробирование внешней памяти при чтении.

|

Рис.23.

EMA (external memory access} — доступ к внешней памяти. Используется также при программировании и проверке ППЗУ; PR (periphery register) — расширение каналов ввода/вывода. Используется также при программировании ППЗУ; ТО — ввод условия для JTO/JNTO или выход тактовых сигналов после выполнения команды ENTO CLK; TI — ввод условия для JT1/JNT1 или ввод счетчика внешних событий после выполнения команды STRT CNT.

Блок программного управления преобразует коды команд программы в сигналы управления. Он включает в себя счетчик команд (PC), дешифратор адреса команды, ППЗУ, регистр команды (IR) и дешифратор команды (IDC). В отличие от МП580, этот блок может работать как с внутренней, так и с внешней памятью. В последнем случае код адреса РС {11: 0} подается на внешнюю программную память, а байтный код команды записывается непосредственно в регистр команды.

Устройство ввода/вывода включает в себя три байтных порта BUS, PI и Р2. Порты Р\ и Р2 имеют идентичные характеристики. При выводе информации данные от ЭВМ записываются в регистры порта и остаются там неизменными до следующей записи.

При вводе информации входной код, поддерживаемый неизменным на время действия импульса RD, маскируется кодом регистра порта и передается в микроЭВМ. Если код вводится без изменений, предварительно, еще до ввода, в регистре порта должен быть записан единичный код маски. Записанный в режиме вывода код регистра порта может программно модифицироваться. Порт Р2 используется также для подключения расширителя ввода/вывода и выдачи четырех старших разрядов программного счетчика РС{11: 8 }.

Порт BUS реализует двунаправленный канал передачи данных. Он передает восемь младших разрядов кода адреса команд РС{1: 0} или кода адреса данных ADRD {7: 0} при работе с внешней программной памятью или памятью данных и байт данных D{1: 0} при работе с внешней памятью или схемами расширения (интерфейсные БИС серии К580). По завершению передачи данных порт переходит в третье состояние.

Блок оперативных регистров включает в себя ОЗУ, таймер-счетчик, регистр состояния программы, схему прерывания и регистр дополнительных флажков. Оперативное запоминающее устройство имеет объем либо в 64 байта (BE 35/48), либо 128 байт (BE 39/49). Назначение отдельных ячеек ОЗУ изображено на рис. 24

Ячейки с адресами 0 + 7 и 24 + 31 образуют два банка регистров общего назначения. Выбор банка осуществляется по состоянию триггера номера банка RBF, а регистра внутри банка — по трехбитному коду адреса регистра в банке N{2:0} (режим прямой регистровой адресации).

К любой ячейке ОЗУ (в том числе и ячейкам банка регистров) можно обратиться по их полному адресу в режиме косвенной регистровой адресации по содержимому регистров R0 или R1 выбранного банка регистров.

В отличие от МП580, в котором стековая память располагается вне микропроцессора и имеет, практически, неограниченный объем (до 64 Кбайт), стек КР816 содержит всего 16 ячеек и обеспечивает запись восьми двухбайтных слов, необходимых для возврата на основную программу после завершения подпрограммы или обработки прерывания. Каждое слово содержит значение адреса возврата PC(11:0} и старшую тетраду слова состояния программы PSW. Напомним, что в МП580 PSW характеризовало состояние аккумулятора и регистра флажков (PSW = F.A). К1816 биты PSW имеют другой смысл: PSW{2:0} (SP{2:0} — указатель стека (адреса отсчитываются от нижней границы стека для двух соседних ячеек (см. рис. 2.2)); PSW{3} = 1 — разряд забит единицей; PSW{4} = RBF — номер банка регистров; PSW{5} = FO - флаг пользователя. PSW{6} = AC(adjust carry) - дополнительный флаг переноса; PSW{7} = C – флаг переноса.

Слово состояния программы хранится в регистре состояния программы и изменяется либо в процессе выполнения команд программы, либо при возврате на основную программу (только старшая тетрада PSW). Флажки пользователя (Fl, RBF, CNTF, INTF) не поместившиеся в регистре PSW, фиксируются триггерами регистра дополнительных флажков. Восьмиразрядный таймер-счетчик считает поступающие из вне через Т1 сигналы и генерирует временные задержки без отвлечения АЛУ от выполнения основной программы. Переключение режимов таймера осуществляется программно. Содержимое счетчика считывается или загружается с помощью аккумулятора. При инкрементном переполнении счетчика (FF -> 00) устанавливается флаг переполнения TF и счет продолжается. Переполнение, если есть на то разрешение, вызывает прерывание программы, которое обслуживается подпрограммой прерывания по адресу 07H. В режиме генерации временных задержек счетчик запитывается от делителя основной тактовой частоты Fbq на 480. При Fbq = 6 МГц квант задержки составляет 80 мкс. Задержки более 80x256=20480 мкс формируются программными средствами. Одноуровневая схема прерываний обеспечивает приоритет прерывания (внешнее прерывание INT — старший, флаг таймера TF — младший) и программное маскирование прерываний. МикроЭВМ КР1816 работает аналогично МП580. Инициализация работы КР1816 происходит при подаче импульса SR длительностью порядка 50 мкс. При этом осуществляются следующие действия:

· программный счетчик сбрасывается в О (PC = 0);

· указатель стека сбрасывается в О (SP = 0);

· выбирается нулевой банк регистров (RBF = 0);

· выбирается нулевой банк программной памяти (MBF = 0);

· блокируется внешнее прерывание (INTF=0);

· порты Р1 и Р2 устанавливаются в режим приема;

· останавливается таймер/счетчик;

· сбрасываются флаги F0 и F1.

Выполнение программы начинается с команды нулевого адреса. Каждая команда занимает от одного до двух байт программной памяти и выполняется внутри цикла команды. Этот цикл делится на машинные циклы (цикл обращения к памяти/цикл генерации ALE), длительность которых составляет 15 периодов сигнала синхронизации Tbq. Это соотношение помогает подсчитывать время выполнения программы и формировать калиброванные временные задержки.

Программа выполняется до тех пор, пока не будут сформированы коды всех управляющих сигналов. После этого микроЭВМ переходит в режим ожидания, выход из которого происходит только в случае либо повторной инициализации программы, либо действия одного из внешних или внутренних сигналов прерывания. При входе в программу по вектору внешнего прерывания управление передается команде по адресу ООЗН, а по вектору прерывания по таймеру — команде по адресу 007Н.

5. Цифровые измерительные приборы (ЦИП). Структурная схема. Основные характеристики.

Цифровым измерительным прибором (ЦИП) называется средство измерения, автоматически вырабатывающее дискретные сигналы измерительной информации, показания которого представлены в цифровой форме.

По виду измеряемых величин цифровые измерительные приборы подразделяются на:

- вольтметры и амперметры постоянного и переменного тока (напряжения);

- омметры и мосты постоянного и переменного тока;

- комбинированные приборы;

- измерители частоты, интервалов времени и фазового сдвига;

- специализированные ЦИП, предназначенные для определения времени срабатывания различных элементов и т.д.

Диапазон измеряемых посредством ЦИП величин обычно весьма широкий и разбивается на ряд поддиапазонов. Выбор нужного поддиапазона в процессе измерения производится вручную или автоматически. Измерение на выбранном поддиапазоне всегда осуществляется автоматически.

Основными классификационными признаками ЦИП принято считать вид измеряемой величины и способ преобразования, определяющие такие важные характеристики, как точность и быстродействие. По виду входных физических величин ЦИП объединяют в следующие основные группы приборов для измерения:

- постоянного и переменного тока (напряжения);

- параметров R, L и С электрических цепей;

- временньгх параметров (частоты, периода, временного интервала, фазы).

Разновидностями ЦИП, входящих в упомянутые группы, являются средства измерений с микропроцессорами, виртуальные приборы на основе компьютеров и цифровые осциллографы.

Наиболее важными техническими характеристиками ЦИП, определяющими возможность их использования для конкретной измерительной задачи, являются: пределы измерения, цена деления, входное сопротивление, быстродействие, точность, помехоустойчивость и надежность. Цену деления шкалы ЦИП можно определить по формуле.

z = xmax/10m (22)

где Xmax — максимальное значение предела измерения; т — число разрядов десятичного цифрового отсчета.

Для каждого предела измерения цена деления постоянна и определяет максимально возможную разрешающую способность для данного типа ЦИП.

Разрешающая способность ЦИП — это изменение цифрового отсчета на единицу первого (младшего) разряда. Иногда под разрешающей способностью понимают значение цены деления младшего (для многопредельных приборов) предела ЦИП.

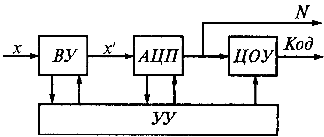

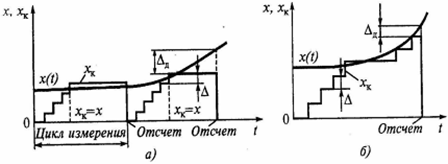

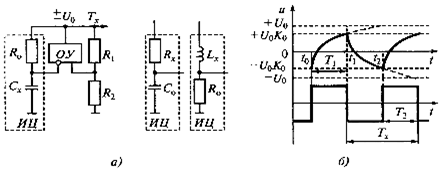

Быстродействие определяется максимальным интервалом времени необходимым для выполнения одного полного цикла измерения (для, ЦИП это время измерения и время индикации) или преобразования (для, АЦП) входной величины. Для ЦИП с равномерной временной дискретизацией этот интервал измерения определяется шагом дискретизации ∆t, а, быстродействие — количеством измерений (преобразований) в 1 с, т.е, значением 1/(∆t).