Реферат: Импульсно-статические, динамические, квазистатические триггеры

БЕЛОРУССКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ИНФОРМАТИКИ И РАДИОЭЛЕКТРОНИКИ

КАФЕДРА РЭС

РЕФЕРАТ

НА ТЕМУ:

«Импульсно-статические триггеры. Динамические триггеры. Квазистатические триггеры»

МИНСК, 2009

Импульсно-статические триггеры

К импульсно-статическим триггерам (ИСТ) относятся триггеры, характеризующиеся следующими признаками:

1. памятью статического типа;

2. управлением сигналами потенциального типа;

3. содержанием в схеме элементов, вырабатывающих сигналы кратковременного (импульсного) воздействия на статические элементы памяти.

По способам управления записью такие триггеры не отличаются столь широким многообразием, как статические триггеры, поскольку среди них отсутствуют триггеры видов L, LF и их модификации с индексом f.

Среди ИСТ возможны

разновидности следующих видов: ![]() ,

, ![]() ,

, ![]() и

и ![]() . По логике работы ИСТ

имеют сходство со статическими триггерами аналогичного вида управления, но

вместе с тем в их работе имеются и определенные различия, которые необходимо

учитывать при их применении. ИСТ (в отличие от статических триггеров)

обозначаются индексом «i»,

например

. По логике работы ИСТ

имеют сходство со статическими триггерами аналогичного вида управления, но

вместе с тем в их работе имеются и определенные различия, которые необходимо

учитывать при их применении. ИСТ (в отличие от статических триггеров)

обозначаются индексом «i»,

например ![]() ,

, ![]() ,

, ![]() ,

, ![]() и других типов.

и других типов.

Триггеры видов ![]() ,

, ![]()

Такие триггеры работают по следующему алгоритму: при отсутствии переключающего фронта ТИ информация может принимать на входах любые состояния: при этом информация на выходах не меняется. При поступлении переключающего фронта ТИ в схеме управления вырабатывается импульсный сигнал, который, поступая на входы собственно триггера, устанавливает его в соответствующее состояние. Одновременно за счет действия переключающего фронта осуществляется запрет на прием информации, которая с этого момента может изменяться, но это изменение не отразится на состоянии триггера.

Особенности триггеров

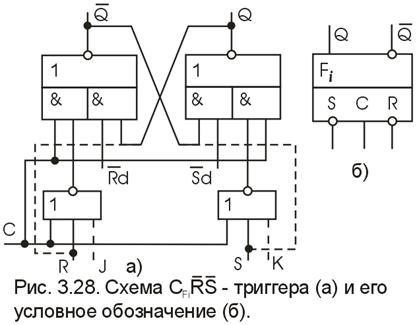

рассмотрим на примере ![]() -триггера, схема

которого показана на рис. 3.28.

-триггера, схема

которого показана на рис. 3.28.

Схема триггера содержит

собственно триггер ![]() типа на элементах

И-ИЛИ-НЕ (

типа на элементах

И-ИЛИ-НЕ (![]()

![]() ) и схему управления на

элементах ИЛИ-НЕ (элементы входов R и S), назначение которой заключается в

выработке импульсного сигнала в момент действия переключающего фронта ТИ. При

подключении

) и схему управления на

элементах ИЛИ-НЕ (элементы входов R и S), назначение которой заключается в

выработке импульсного сигнала в момент действия переключающего фронта ТИ. При

подключении ![]() и

и ![]() ко входам триггера (как

это показано на рис. 1 штриховыми линиями) устройство будет работать в качестве

триггера

ко входам триггера (как

это показано на рис. 1 штриховыми линиями) устройство будет работать в качестве

триггера ![]() -типа, а с дополнительными

входами — в качестве триггера

-типа, а с дополнительными

входами — в качестве триггера ![]() -типа.

-типа.

По сравнению с аналогичными схемами вида F статического типа данная схема значительно проще в реализации и требует меньшего числа вентилей.

К недостаткам следует отнести меньшую помехоустойчивость вследствие того, что управляющие сигналы воздействуют на входы собственно триггера в течение небольшого интервала времени ТИ, тогда как в статических триггерах сигнал действует на входы собственно триггера в течение всей длительности ТИ.

Важным преимуществом таких схем является и то, что они позволяют довольно легко устанавливать триггер в исходное состояние по входам Rd и Sd независимо от уровня сигнала на входе С.

Динамические триггеры

Динамические триггеры (ДТ) отличаются следующими признаками:

1. динамическим (кратковременным) хранением информации (как правило, для хранения информации используются паразитные емкости затворов МДП-транзисторов);

2. наличием многофазного (многотактного) импульсного управления или питания;

3. управлением сигналами ограниченной длительности, то есть импульсными сигналами;

4. содержанием схемой управления устройств для формирования импульсов многофазного управления.

Наибольшее распространение получили ДТ, выполненные на основе МДП-транзисторов, хотя известны ДТ, на основе биполярных транзисторов. По способам управления записью ДТ являются триггерами вида [L]. В отличие от статических триггеров, такие триггеры обозначают индексом «d».

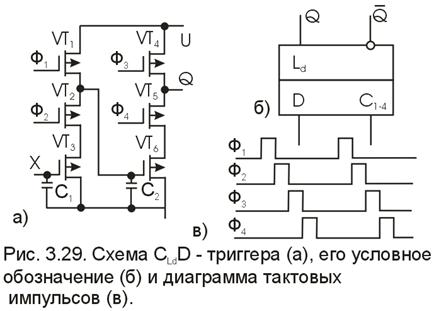

В практике проектирования

цифровых устройств ДТ в основном представлены триггерами ![]() типа, хотя в принципе

возможны и другие функциональные типы. В качестве примера рассмотрим схему

типа, хотя в принципе

возможны и другие функциональные типы. В качестве примера рассмотрим схему ![]() триггера, приведенную на

рис. 3.29.

триггера, приведенную на

рис. 3.29.

Триггер собран на МДП-транзисторах p-типа, где под С понимается серия из четырех сдвинутых во времени импульсов. Триггер построен на основе двух инверторов, один из которых содержит транзисторы VT1-VT3, а второй транзисторы VT4-VT6 и управляется серией из четырех сдвинутых во времени импульсов. Затвор транзистора VT3 первого инвертора является информационным входом (входом D) триггера, а выход второго инвертора (Q) является выходом разряда.

Рассмотрим процесс записи информации в триггер (пусть D=1). При поступлении Ф1 открывается транзистор VT1 и происходит заряд конденсатора С2 в цепи затвора транзистора VT6 до уровня 1. После окончания Ф1 поступает Ф2, который откроет транзистор VT2, а поскольку открыт транзистор VT3 уровнем D=1, то конденсатор С2 окажется разряжен (С2=0). Затем поступает Ф3, открывающий транзистор VT4, через который заряжается выходной конденсатор С1 (следующего каскада) и являющийся его входом. После окончания Ф3 поступает Ф4, открывающий транзистор VT5. Поскольку транзистор VT6 закрыт уровнем Q=0, то конденсатор С1 (следующего каскада) останется заряженным до уровня Q=1.

Таким образом, в результате действия серии из четырех импульсов сигнал с уровнем 1, действующий на его входе, оказался зафиксированным на выходе триггера, то есть произошла запись информации. Аналогично триггер будет установлен в 0 при D=0.

Нетрудно видеть, что если во время действия Ф1 или Ф2 информация на входе будет изменяться, то триггер будет реагировать на это изменение так же, как триггеры L-типа, поскольку схема не вырабатывает сигнал блокировки, который бы запрещал прием информации.

Из описания работы триггера следует, что он не может хранить информацию сколь угодно долго, так как ее запоминание осуществляется на емкостях затворов, то есть требуется периодическая подзарядка емкости, что и достигается серией из четырех импульсов. Этим же обстоятельством объясняется и тот факт, что триггер управляется сигналами ограниченной длительности. В интегральной схемотехнике ДТ применяются в основном при проектировании сдвигающих регистров.

Квазистатические триггеры

Квазистатические триггеры (КТ) характеризуются следующими признаками:

1. управлением сигналами ограниченной длительности;

2. наличием тактирующих (фазных) импульсов, используемых только для записи информации (при хранении информации тактирующие импульсы не требуются);

3. наличием двух типов памяти — статической и динамической;

4. содержанием в составе схемы управления устройства для формирования фазных импульсов.

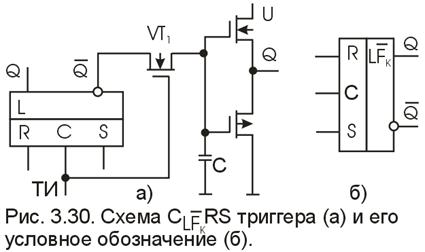

На рис. 3.30 показана

обобщенная схема КТ на примере RS-триггера.

Схема содержит следующие элементы: статический элемент памяти; схему

формирования фазных импульсов (СФИ); коммутирующий транзистор (VT1); динамический элемент памяти в виде емкости «С»

затвора выходного инвертора; выходной инвертор. Статический элемент памяти

выполнен в виде ![]() триггера. Однако

это совсем не обязательно, так как может использоваться любой другой

функциональный тип триггера вида L или F. Схема формирования фазных импульсов

имеет всего одну связь с затвором коммутирующего транзистора, то есть роль СФИ

выполняет тактирующий импульс. В общем случае эта схема формирует не более трех

фазных импульсов, число которых определяется организацией схемы статического

триггера.

триггера. Однако

это совсем не обязательно, так как может использоваться любой другой

функциональный тип триггера вида L или F. Схема формирования фазных импульсов

имеет всего одну связь с затвором коммутирующего транзистора, то есть роль СФИ

выполняет тактирующий импульс. В общем случае эта схема формирует не более трех

фазных импульсов, число которых определяется организацией схемы статического

триггера.

Коммутирующий транзистор и выходной инвертор выполнены на КМДП-элементах.

Роль динамического элемента памяти выполняет емкость затвора КМДП-транзистора выходного инвертора.

По способам управления

записью информации КТ относятся к триггерам видов ![]() ,

,

![]() , хотя возможны и триггеры

видов

, хотя возможны и триггеры

видов ![]() ,

, ![]() .

.

В отличие от статических

данные триггеры будем обозначать дополнительным индексом К, например ![]() ,

, ![]() триггеры и др.

триггеры и др.

В интегральной

схемотехнике КТ наиболее часто применяются при построении сдвигающих регистров,

а среди их функциональных типов — как правило ![]() триггеры.

Наиболее распространены триггеры двух- и четырехфазного действия. Схемы КТ

выполняются с применением меньшего числа МДП-транзисторов, чем это необходимо

для построения аналогичных триггеров статического типа. Сравнительная простота

построения КТ позволяет выполнить их как на МДП-транзисторах p-типа, так и на дополняющих

МДП-транзисторах (КМДП).

триггеры.

Наиболее распространены триггеры двух- и четырехфазного действия. Схемы КТ

выполняются с применением меньшего числа МДП-транзисторов, чем это необходимо

для построения аналогичных триггеров статического типа. Сравнительная простота

построения КТ позволяет выполнить их как на МДП-транзисторах p-типа, так и на дополняющих

МДП-транзисторах (КМДП).

ЛИТЕРАТУРА

1. Новиков Ю.В. Основы цифровой схемотехники. Базовые элементы и схемы. Методы проектирования. М.: Мир, 2001. - 379 с.

2. Новиков Ю.В., Скоробогатов П.К. Основы микропроцессорной техники. Курс лекций. М.: ИНТУИТ.РУ, 2003. - 440 с.

3. Пухальский Г.И., Новосельцева Т.Я. Цифровые устройства: Учеб. пособие для ВТУЗов. СПб.: Политехника, 2006. - 885 с.

4. Преснухин Л.Н., Воробьев Н.В., Шишкевич А.А. Расчет элементов цифровых устройств. М.: Высш. шк., 2001. - 526 с.

5. Букреев И.Н., Горячев В.И., Мансуров Б.М. Микроэлектронные схемы цифровых устройств. М.: Радио и связь, 2000. - 416 с.

6. Соломатин Н.М. Логические элементы ЭВМ. М.: Высш. шк., 2000. - 160 с.