Дипломная работа: Розробка цифрових засобів ПЛІС в інтегрованому середовищі проектування MAX+PLUS II

Міністерство освіти і науки України

Національний технічний університет України

“Київський політехнічний інститут”

Приладобудівний факультет

Кафедра приладів та систем орієнтації і навігації

Атестаційна магістерська робота

на тему:

Розробка цифрових засобів ПЛІС в інтегрованому

середовищі проектування MAX+PLUS II

Київ 2009

Зміст

Анотація

Перелік умовних позначень, символів, скорочень і термінів

Вступ

1. Генезис програмувальних логічних інтегральних схем, їх класифікація та архітектура

2. Призначення та структура системи автоматизованого проектування MAX+PLUS II

3. Додатки системи автоматизованого проектування MAX+PLUS II

4. Процедура розробки нового проекту в системі автоматизованого проектування MAX+PLUS II

5. Процедура компіляції створеного проекту в системі автоматизованого проектування MAX+PLUS II

6. Загальні відомості про мову описання апаратури AHDL

7. Реалізація в інтегрованому середовищі MAX+PLUS II базових пристроїв мікроелектроніки

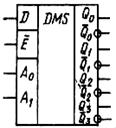

7.1 Теоретичні відомості про тригери

7.1.1 RS-тригер

7.1.2 Синхронний RS-тригер

7.1.3 D-тригер

7.1.4 JK-тригер

7.1.5 Програми реалізації тригерів в інтегрованому середовищі MAX+PLUS II

7.1.6 Результати програмної реалізації тригерів

7.2 Теоретичні відомості про регістри

7.2.1 Послідовні регістри зсуву

7.2.2 Паралельні регістри зсуву

7.2.3 Програма реалізації регістрів в інтегрованому середовищі MAX+PLUS II

7.2.4 Результати програмної реалізації регістрів

7.3 Теоретичні відомості про лічильники

7.3.1 Лічильник з крізним переносом

7.3.2 Асинхронний лічильник з модулем 10

7.3.3 Лічильник віднімання

7.3.4 Програми реалізації лічильників в інтегрованому середовищі MAX+PLUS II

7.3.5 Результати програмної реалізації лічильників

7.4 Теоретичні відомості про мультиплексори, демультиплексори, шифратори, дешифратори

7.4.1 Мультиплексор

7.4.2 Демультиплексор

7.4.3 Шифратор

7.4.4 Дешифратор

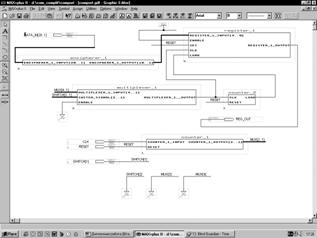

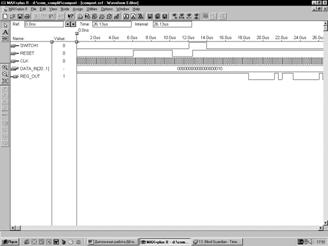

7.4.5 Програми реалізації мультиплексорів, демультиплексорів, шифраторів, дешифраторів в інтегрованому середовищі MAX+PLUS II

7.4.6 Результати програмної реалізації мультиплексорів, демультиплексорів, шифраторів, дешифраторів

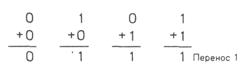

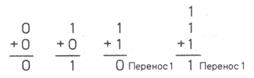

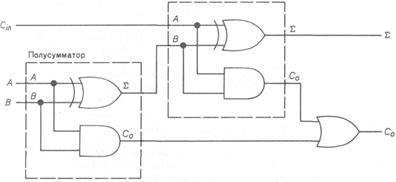

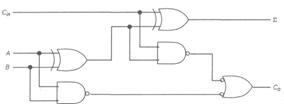

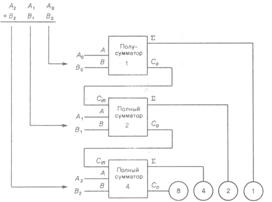

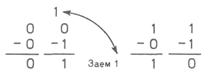

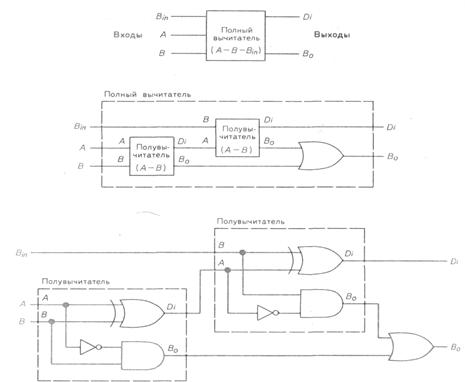

7.5 Теоретичні відомості про суматори, віднімачі

7.5.1 Суматори

7.5.2 Віднімачі

7.5.3 Програми реалізації суматорів, віднімачів в інтегрованому середовищі MAX+PLUS II

7.5.4 Результати програмної реалізації суматорів, віднімачів

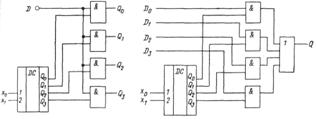

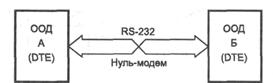

8. Проект реалізації COM-порту в САПР MAX+PLUS II

8.1 Теоретичні відомості про послідовні порти і протокол RS-232

8.2 Структура COM-порту при його реалізації в САПР MAX+PLUS II

8.3 Програми структурних компонентів COM-порту мовою AHDL в САПР MAX+PLUS II

8.4 Результати програмної реалізації COM-порту в САПР MAX+PLUS II

Висновки

Використана література

Анотація

Дипломна робота викладена на 108 аркушах, містить 61 ілюстрацію, 17 таблиць і 20 посилань на джерела інформації, що мають відношення до даного тематичного напрямку.

Метою дипломної роботи є створення інформаційно-програмної бази для роботи з інтегрованим середовищем MAX+PLUS II.

Роботою передбачено теоретичний опис основних приладів мікроелектроніки разом з їх програмною реалізації за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II. В роботі проведено генезис програмувальних логічних інтегральних схем, їх класифікація, архітектура, детально розписана процедура створення нового проекту і процес його компіляції.

З метою більш детального пояснення взаємозв’язку різних додатків зазначеного середовища в дипломній роботі реалізовано проект послідовного COM-порту, що складається з декількох базових мікроелектронних пристроїв, принципи дії яких було описано у відповідних розділах.

Результатом дипломної роботи є описання основ роботи з інтегрованим середовищем MAX+PLUS II, підкріплене прикладами розробки і моделювання конкретних пристроїв. Вони можуть використовуватися як в дидактичних, так і в науково-дослідницьких цілях.

В подальшому можливий розвиток і доповнення роботи за наступними напрямками: створення програмно-інформаційної бази найбільш поширених мікроелектронних приладів на основі ПЛІС фірми Altera; визначення можливості інтеграції інтегрованого середовища MAX+PLUS II з іншими пакетами та системами автоматичного проектування; створення на базі ПЛІС мікропроцесорних пристроїв з відносно малими габаритами і споживчою потужністю.

Ключові слова (словосполучення): архітектура пристрою, електроніка, гнучка логіка, мікроелектронний пристрій, моделювання поведінки, послідовний порт, програмувальна логічна інтегральна схема, програмування, компіляція, система автоматичного проектування.

Перелік умовних позначень, символів, скорочень і термінів

АДП – апаратура передачі даних;

БМК – базовий матричний кристал;

ПЛІС – програмувальна логічна інтегральна схема;

ПЛМ – програмувальна логічна інтегральна матриця;

ПЛП – програмувальний логічний пристрій;

ППЗП – програмувальній постійній запам’ятовуючій пристрій;

ООД – одно кінцевий об’єкт передачі даних

САПР – система автоматизованого проектування;

СБФ – система булєвих функцій;

AMD – Advanced Micro Devices;

CLK – CLocK;

CPLD – Complex Programmable Logic Device;

DCE – Data Communication Equipment;

DTE – Data Transfer Equipment;

ENA – ENAble;

FLEX – Flexible Logic Element Matrix;

FPGA – Field Programmable Gate Array;

GA – Gate Array;

GAL – Generic Array Logic;

IOB – Input/Output Element;

JTAG – Joint Test Action Group;

LAB – Logic Array Block;

LE – Logic Element;

MAX – Multiple Array Matrix;

PLA – Programmable Logic Array;

PLD – Programmable Logic Devices;

PLS – Programmable Logic Sequencers;

PROM – Programmable Read Only Memory;

SPLD – Standart Programmable Logic Devices.

Вступ

Широке впровадження електроніки й автоматики в усі сфери людської діяльності, що спостерігається в даний час, пред'являє все більш жорсткі вимоги до виробів електронної техніки. Це пов'язано, з одного боку, зі зростанням важливості і складності розв'язуваних задач, а, з іншого боку, необхідністю поліпшення таких характеристик, як швидкодія, надійність, споживана потужність, габарити, вартість та інше. Одним з шляхів вирішення даної проблеми є широке використання програмувальних логічних інтегральних схем (ПЛІС - Programmable Logic Devices - PLDs).

ПЛІС являють собою нову елементну базу, що володіє гнучкістю замовлених ВІС і доступністю традиційної "твердої" логіки.

Головною відмітною властивістю ПЛІС, на відміну від “жорсткої” логіки, є можливість настроювання на виконання заданих функцій самим користувачем. Сучасні ПЛІС характеризуються низькою вартістю, високою швидкодією, значними функціональними можливостями, багаторазовістю перепрограмування, низкою споживаною потужністю й інше.

При цьому час розробки на основі ПЛІС навіть досить складних проектів може складати усього кілька годин. Власно кажучи, розробка пристроїв на основі ПЛІС являє собою нову технологію проектування електронних схем, включаючи їх виготовлення і супроводження. Доказом перспективності нової елементної бази служить щорічна поява нових поколінь ПЛІС, а також постійно зростаючий обсяг випуску вже розроблених ПЛІС.

Істотною перешкодою широкого практичного використання ПЛІС є відсутність ефективних методів синтезу. Справа в тому, що в основу архітектури сучасних ПЛІС покладена структура програмувальних логічних матриць (ПЛМ — Programmable Array Logics — PALs), що являє собою пари матриць: І й АБО, у якій програмується матриця І, а матриця АБО має фіксоване положення. Методи й алгоритми синтезу на такій структурі одержали назву двухуровнего синтезу і бурхливо розвивалися в 80-х роках. З часом інтерес дослідників на багато років залучив багаторівневий синтез, використовуваний при проектуванні цифрових систем на основі FPGA (Field Programmable Gate Array).

В останні роки спостерігається явне протиріччя: архітектури ПЛІС бурхливо розвиваються й удосконалюються, а методи проектування на їх основі залишаються без зміни.

Інтегроване середовище MAX+PLUS II фірми Altera пропонує повний спектр можливостей логічного дизайну: різноманітні засоби опису проектів з ієрархічною структурою, потужний логічний синтез, компіляцію з заданими часовими параметрами, розподілення на підпрограми основного проекту, функціональне і часове тестування (симуляцію), тестування декількох взаємопов’язаних властивостей, аналіз часових параметрів системи, автоматичну локалізацію помилок, а також програмування і верифікацію помилок.

Відносно низьку популярність даного інтегрованого середовища серед вітчизняних проектувальників можливо пояснити відсутністю детальної та ємної документації українською мовою про можливості та властивості MAX+PLUS II. Ліквідацію саме такого інформаційного браку і було взято автором за стратегічну мету написання дипломної роботи.

Для спрощення розуміння читачем структурної організації і функціонального призначення додатків інтегрованого середовища в роботі наведено генезис програмувальних логічних інтегральних схем, їх класифікація, архітектура, детально розписана процедура створення нового проекту і процес його компіляції.

В дипломній роботі наведено приклади опису в інтегрованому середовищі MAX+PLUS II всіх базових пристроїв мікроелектроніки, як то:

1) JK-тригера, D-тригера, RS-тригера;

2) послідовних регістрів зсуву, паралельних кільцевих регістра зсуву;

3) лічильників з крізним переносом, асинхронних лічильників, лічильників віднімання, універсального лічильника;

4) шифраторів, дешифраторів, мультиплексорів, демультиплексорів (з використанням функцій алгебри логіки і таблиць дійсності);

5) суматорів, віднімачів.

1. Генезис програмувальних логічних інтегральних схем, їх класифікація та архітектура

Історія розвитку програмувальних логічних інтегральних схем (ПЛІС) або програмувальних логічних пристроїв (ПЛП - Programmable Logic Devices - PLD) починається з появи на початку 70-х років програмувальних постійних запам'ятовуючих пристроїв (ППЗП - Programmable Read Only Memory - PROM). Перший час програмувальні постійні запам’ятовуючі пристрої використовувалися винятково для збереження даних, пізніше їх стали застосовувати для реалізації логічних функцій. Однак, необхідність приведення логічних функцій до завершеної диз’юнктивної нормальної форми не дозволяло використовувати PROM для реалізації функцій великих розмірів.

Спеціально для реалізації систем булєвих функцій (СБФ) великого числа змінних були розроблені і з 1971 р. стали випускатися промисловістю програмувальні логічні матриці (ПЛМ - Programmable Logic Arrays - PLAs). PLA дуже широко розповсюджені в якості універсальної елементної бази цифрових пристроїв, тому саме PLA можна вважати першими PLD.

Удосконалювання архітектури PLA призвело до появи програмувальних матриць логіки (ПЛМ - Programmable Array Logics - PALs), що дотепер визначають найбільш популярну архітектуру PLD. Перші PAL були розроблені фірмою Monolithic Memories у 1976 році, а вироблятися вони почали з 1977 року фірмою Advanced Micro Devices (AMD). З моменту своєї появи PAL стали успішно конкурувати з PLA і в даний час завдяки ряду позитивних властивостей практично цілком замінили програмувальні користувачем PLA.

Подальше удосконалювання технології виробництва інтегральних схем на початку 90-х років призвело до можливості реалізації на одному кристалі декількох PAL, поєднуваних програмувальними з'єднаннями. Подібні архітектури одержали назва складних ПЛП (Сomplex PLD - CPLD), відповідно всі розроблені раніше PLD стали називати стандартними ПЛУ (Standart PLD - SPLD) або класичними ПЛУ (Classic PLD).

Паралельно з PLD також розвивалися архітектури вентильних матриць (Gate Array - GA) і матриць логічних осередків (Logic Cell Array - LCA), у російськомовній літературі вони отримали назву базових матричних кристалів (БМК). Перші вентильні матриці були напівзамовленими, тобто програмувалися під час виготовлення, що стримувало їх широке практичне використання. Однак у 1985 році фірма Xilinix випустила програмовану користувачем вентильну матрицю (Field Programmable Gate Array — FPGA). Це дало сильний поштовх до широкого поширення вентильних матриць і конкуренції їх з PLD. Хоча FPGA і не є предметом дослідження даної роботи, згадування про них необхідно для порівняльного аналізу архітектур CPLD і FPGA.

В даний час спостерігається бурхливий розвиток архітектур CPLD і FPGA, зниження їхньої вартості, підвищення швидкодії і функціональної потужності (табл. 1.1). Це дозволяє припустити, що в найближчі п'ять років основу елементної бази цифрових систем будуть складати CPLD і FPGA.

Табл. 1.1. Перспективність складних програмувальних логічних пристроїв (CPLD).

| Параметри | 1985 | 1990 | 1995 | 2000 | 2005 |

| Число вентилів, шт. |

8×102 |

5×103 |

5×104 |

1×106 |

2×106 |

| Число виводів, шт. |

6.4×101 |

2.56×102 |

5×102 |

1×103 |

2×103 |

| Число транзисторів, шт. |

8.5×103 |

2×106 |

6×106 |

2.25×108 |

5×108 |

| Швидкодія, нс | 40 | 15 | 3.5 | 1.5 | 0.75 |

У російськомовній літературі немає чіткого поділу між PLD, PAL, PLA, SPLD, CPLD і FPGA. Найчастіше всі ці пристрої називають програмувальними логічними інтегральними схемами, чому в англомовній літературі відповідає термін programmable logic (рис. 1.1) – програмувальна логіка.

В даний час програмувальні логічні пристрої прийнято поділяти на два великих класи: стандартні програмувальні логічні пристрої (SPLD) і складні програмувальні логічні пристрої (CPLD). За своїми функціональними можливостями, ступенями інтеграції і способові використання до складних програмувальних логічних пристроїв наближаються програмовані користувачем логічні матриці.

Рис. 1.1. Класифікація програмувальних логічних інтегральних схем

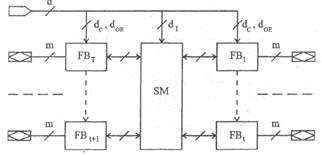

Структуру більшості SPLD умовно можливо подати у вигляді сукупності двох матриць взаємно ортогональних провідників: матриці І (AND) і матриці АБО (OR). Вхідні сигнали звичайно надходять на парафазні входи матриці І, що на ортогональних шинах дозволяє реалізувати будь-які кон’юнкції вхідних змінних. Виходи матриці І з'єднані з входами матриці АБО та на виходах реалізує диз'юнкції сигналів, що надходять.

Сукупність вихідних шин матриці І утворює множину проміжних шин PLD (product terms) або просто термів (terms).

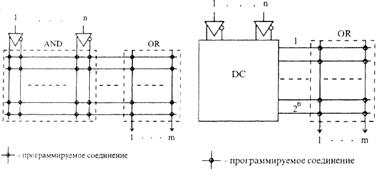

Рис. 1.2. Структура PLA Рис. 1.3. Структура PROM

В залежності від того, яка матриця програмується, матриця І чи матриця АБО, SPLD прийнято поділяти на три класи: PLA, PROM і PAL. У PLA (рис. 1.2) програмуються обидві матриці: матриця І та матриця АБО. У PROM (рис. 1.3) матриця І постійно налаштована на функції повного дешифратора, а програмується тільки матриця АБО.

У структурі PAL (рис. 1.4), навпаки, програмується тільки матриця І, а матриця АБО має фіксоване налагодження, при якій q проміжних шин зв'язується з одним виходом. Це дозволяє матрицю АБО реалізувати у виді сукупності q-входових диз‘юнкторов.

На перший погляд може показатися, що PAL значно уступають PLA за своїми можливостями, оскільки вводиться обмеження на число проміжних шин, що приєднуються до одного виходу. Практика ж показує, що дане обмеження в більшості застосувань не критично.

Якщо все-таки це трапляється, можливо об'єднати кілька виходів по АБО за допомогою логічного елемента або провідним з'єднанням (для інверсної логіки).

Рис. 1.4. Структура PAL.

З іншого боку, у PAL програмується тільки одна матриця І, що значно спрощує структуру PAL і, як наслідок, приводить до зниження вартості пристрою і підвищенню його швидкодії. Крім того, спрощення матриці АБО дозволило додати в структуру PAL ланцюг зворотного зв'язку і вихідні буфери, завдяки чому PAL набули нових якостей.

Вихідні буфери PAL являють собою програмувальні макроосередки, що і визначають архітектуру PAL. Макроосередки PAL можуть включати вихідний інвертор із трьома станами, тригери різного типу, вентилі "АБО, що вилучає" і ін. Відповідно до типу вихідних макроосередків PAL поділяють на функціональні групи: комбінаційні, реєстрові, універсальні, асинхронні й ін. У свою чергу виробники поділяють PAL на сімейства, у яких виділяють серії пристроїв, причому в одній серії можуть зустрічатися пристрої з різних функціональних груп. Більш того, різні типи вихідних макроосередків можуть одночасно зустрічатися в одній PAL.

Безумовно, приведена класифікація не охоплює всієї розмаїтості SPLD. Наприклад, структуру, що дуже нагадує PLA, мають програмувальні логічні секвенсери (Programmable Logic Sequencers - PLS), а узагальнені матриці логіки (УМЛ - Generic Array Logics - GAL) подібні PAL.

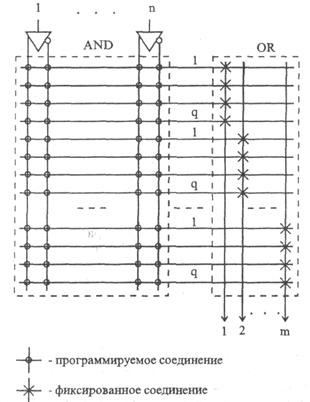

Рис.1.5. Узагальнена структура CPLD

Складними PLD прийнято називати мікросхеми високого ступеня інтеграції, структура яких являє собою сукупність функціональних блоків з архітектурою PAL (рис. 1.5), поєднаних програмувальною матрицею переключень (Switch Matrix - SM).

Багатьма фірмами випускаються різні структури CPLD. Наприклад, фірма AMD свої CPLD назвала КМОП-макроматриці високої щільності (Macro Array CMOS High-density - MACH). Фірма Altera випускає кілька видів CPLD: багаторазові матричні таблиці (Multiple Array Matrix - MAX) і FLASH-пристрої, названі за засобом перепрограмування елементів, що здатні до багаторазового налагоджування.

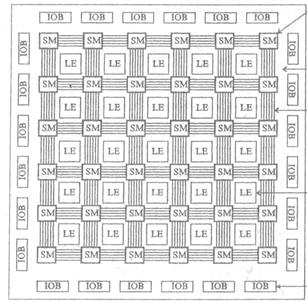

Подальший розвиток структура складних PLD одержала в мікросхемах фірми Altera, названих матрицями елементів гнучкої логіки (Flexible Logic Element Matrix - FLEX), узагальнена структура яких подана на рис. 1.6. Тут відсутня звична PAL-структура, а є лише блоки логічних елементів, поєднувані в LAB-модулі (LAB - Logic Array Block) по 8 елементів у кожнім. Відмінною рисою FLEX-пристроїв є те, що матриця переключень реалізована у вигляді горизонтальних і вертикальних каналів з’єднань (каналів трасування).

Рис. 1.6. Структура FLEX-пристроїв

Це дозволило значно зменшити площу кристала, займаного матрицею переключень, без суттєвого зниження властивостей CPLD. Елементи введення-виведення (IOE - Input/Output Element), що обслуговують зовнішні виводи, приєднуються безпосередньо до каналів з’єднань.

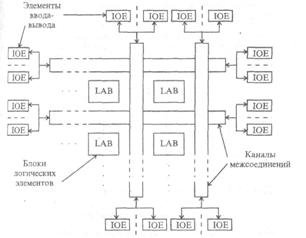

Архітектуру FPGA доцільно розглянути на прикладі пристроїв фірми Xilinix. Основу структури FPGA (рис. 1.7) складає матриця логічних елементів (Logic Element - LE), між якими розташовується поле з’єднань: сукупність вертикальних і горизонтальних каналів.

Якщо в FLEX-пристроях лінії каналів з’єднань безперервні і проходять через всю довжину або ширину кристала, то в FPGA лінії каналів складаються з окремих сегментів, що з'єднуються програмувальними матрицями переключень. По боках кристала FPGA розташовані блоки введення-виведення (Input/Output Blocks - IOBs).

Рис.1.7. Структура FPGA фірми Xilinix

Розглянута класифікація PLD стосується лише їх архітектури. Існують класифікації PLD за типом налагоджуваного елемента, кількістю перепрограмувань, затримці при проходженні сигналів и так далі. Виходячи з поставленого технічного завдання проектувальник самостійно обирає тип програмуємих логічних інтегральних схем, користуючись співвідношенням основних параметрів PLD (табл. 1.1) до ціни конкретної мікросхеми. Чималу роль при обранні елементної бази відіграють і досвід проектувальника, а також доступність програмних засобів ефективного синтезу логічної схеми. Останнім часом компанії-виробники PLD звернули увагу на розробку саме таких програмних пакетів.

2. Призначення та структура системи автоматизованого проектування MAX+PLUS II

Система автоматизованого проектування MAX+PLUS II являє собою інтегроване середовище для розробки цифрових пристроїв на базі програмувальних логічних інтегральних схем фірми Altera. Він забезпечує виконання всіх етапів, необхідних для випуску готових виробів:

1) створення проектів логічних пристроїв;

2) синтез структур і трасування внутрішніх зв'язків програмувальних логічних інтегральних схем;

3) підготовку даних для програмування або конфігурацію програмувальних логічних інтегральних схем (компіляцію);

4) верифікацію проектів (функціональне моделювання і часовий аналіз), програмування або конфігурацію програмувальних логічних інтегральних схем.

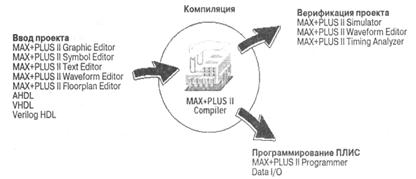

Наданий на рис. 2.1 склад програмного забезпечення системи автоматизованого проектування MAX+PLUS II є повним комплектом, що забезпечує створення логічних дизайнів для пристроїв фірми Altera з програмувальною логікою, в тому числі і родин пристроїв ACEX 1000, MAX 7000, MAX 9000, FLEX 6000, FLEX 8000, FLEX 10000.

Рис. 2.1. Середовище проектування в системі MAX+PLUS II

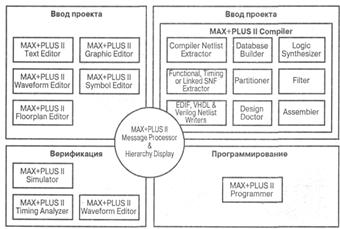

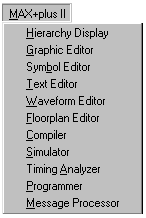

В систему автоматизованого проектування MAX+PLUS II входять 11 додатків (рис. 2.2).

Рис. 2.2. Додатки в системі MAX+PLUS II

Сукупність ієрархічно пов’язаних файлів називається проектом (project). Можливо описати проект (Design Entry) у вигляді файла на мові описання апаратури, створеного в зовнішньому редакторі, або в текстовому редакторі MAX+PLUS II (Text Editor), у вигляді схеми електричної принципової за допомогою графічного редактора (Graphic Editor); у вигляді часової діаграми, створеної в сигнальному редакторі (Waveform Editor). Для зручності роботи зі складними ієрархічними проектами кожному проекту нижчого рівня ієрархії може бути поставлений у відповідність символ, редагування якого відбувається за допомогою символьного редактора (Symbol Editor). Редагування розміщення вузлів по логічним блокам і виводам програмувальних логічних інтегральних схем відбувається за допомогою порівневого планувальника (Floorplan editor).

Верифікація проекту (Project verification) виконується за допомогою симулятора (simulator), результати роботи якого зручно проглянути в сигнальному редакторі. Тестові впливи створюються також в сигнальному редакторі.

Компіляція проекту, в тому числі і витягнення із списку з’єднань компонентів (Netlist Extractor), побудова бази даних (Data Base Builder), логічний синтез, зволікання часових, функціональних параметрів (SNF Extractor), розбиття на частини (Partioner), трасування (Fitter) і формування файла програмування і завантаження (Assembler) виконуються за допомогою компілятора (Compiler) системи.

Безпосереднє програмування або завантаження конфігурації пристроїв з використанням відповідного апаратного забезпечення виконується з використанням модуля програматора (Programmer).

Більшість характерних рис і команди – такі, як відкриття файлів, введення назначених пристроїв, виводів і логічних елементів, компіляція плинного проекту – схожі для багатьох додатків системи MAX+PLUS II. Редактори для розробки проекту (графічний, текстовий, сигнальний) мають багато спільного з допоміжними редакторами (порівневого планування та символьний). Кожний редактор розробки проекту дозволяє виконувати схожі завдання схожим способом.

Можливо легко комбінувати різні типи файлів в ієрархічному проекті, обираючи для кожного функціонального блоку той формат описання проекту, який є більш зручним. Бібліотека мегафункцій і макрофункцій, що надається фірмою Altera, в тому числі і функції з бібліотеки параметризованих модулів, забезпечує додаткові можливості для описання проекту.

Можна одночасно працювати з різними додатками системи MAX+PLUS II. Наприклад, можна відкрити декілька файлів проекту і переносити інформацію з одного проекту в інший, або наприклад проглянути все дерево проекту.

Основою системи MAX+PLUS II є компілятор, що забезпечує потужні засоби обробки проекту, при цьому можливо задавати різні режими роботи компілятора. Автоматична локалізація помилок, видача повідомлень і достатньо широка документація про помилки прискорюють і полегшують проведення змін в проекті. Стало можливим створювати вихідні файли в різних форматах для різних цілей, таких, як робота функцій, часових параметрів і зв’язку декількох пристроїв, аналізу часових параметрів, програмування пристрою.

3. Додатки системи автоматизованого проектування MAX+PLUS II

Програмне забезпечення системи автоматизованого проектування MAX+PLUS II складається з 11 додатків і головної керуючої оболонки.

Різні додатки, що забезпечують створення файлу проекту, можуть бути активізовані миттєво, що дозволяє користувачу переключатися між ними за допомогою миші або командного меню. В цей же час може працювати один з фонових додатків, наприклад компілятор, симулятор, часовий аналізатор, програматор. Одні і ті ж команди різних додатків працюють однаково, що полегшує процес роботи розробки проекту.

Вікно будь-якого додатку можна згорнути до піктограми, не закриваючи самого додатку, а потім знову його розкрити.

В табл. 3.1 наведено піктограми і описання додатків.

Табл. 3.1. Додатки системи автоматизованого проектування MAX+PLUS II

| Піктограма | Назва | Функціональне призначення доданку |

|

|

Огляд ієрархії (Hierarchy Display) |

Відображає плинну ієрархічну структуру файлів у вигляді дерева з гілками, що являють собою підпроекти. Можна візуально визначити чи є файл проекту схемним, текстовим чи сигнальним; які файли відкрити в даний момент; які допоміжні файли в проекті доступні для редагування. Можна також безпосередньо відкрити або закрити один або декілька файлів дерева і ввести ресурси |

|

|

Графічний редактор (Graphic Editor) |

Дозволяє розробляти схемний логічний дизайн в форматі реального відображення на екрані WYSIWYNG. Використовуючи розроблені фірмою Altera примітиви, мегафункції і макрофункції в якості основних блоків розробки, користувач може також використовувати свої символи |

|

|

Символьний редактор (Symbol Editor) |

Дозволяє редагувати існуючі і створювати нові символи |

|

|

Текстовий редактор (Text Editor) |

Дозволяє створювати і редагувати текстові файли проекту, що написані на мовах AHDL, VHDL і Verilog HDL. Крім того, в даному редакторі можна створювати, розглядати і редагувати інші файли формату ASCII, що використовуються іншими додатками MAX+PLUS II |

|

|

Сигнальний редактор (Waveform Editor) |

Виконує подвійну функцію: це інструмент для розробки проекту і одночасно - інструмент для введення текстових сигналів і спостережень тестування |

|

|

Порівневий планувальник (Floorplan Editor) |

Дозволяє графічним засобам створювати призначення виводам приладу і ресурсів логічних елементів та блоків. Можна редагувати розташуванням виводів на кресленні корпуса пристрою і призначити сигнали окремим логічним елементам на більш детальній схемі логічної структури |

|

|

Компілятор (Compiler) |

Обробляє логічні проекти, що розроблені для сімейств Altera Classic, MAX 5000, MAX 7000, MAX 9000, FLEX 6000, FLEX 8000, i FLEX 10k. Більшість завдань виконується автоматично, але користувач може керувати процесом компіляції повністю або частково |

|

|

Симулятор (Simulator) |

Дозволяє тестувати логічні сигнали і внутрішню синхронізацію логічної схеми, що проектується. Можливі три варіанти тестування: функціональне, часове і тестування декількох поєднаних між собою пристоїв |

|

|

Аналізатор часових параметрів (Timing Analyzer) |

Аналізує роботу логічного ланцюга, що проектується після того, як вона була синтезована та імітизована компілятором, дозволяє оцінювати затримки в схемі |

|

|

Програматор (Programmer) |

Дозволяє програмувати, конфігурувати, проводити верифікацію і досліджувати пристрої фірми Altera |

|

|

Генератор повідомлень (Message Processor) |

Видає на екран повідомлення про помилки, попереджуючі і інформаційні повідомлення про стан проекту користувача і дозволяє користувачу автоматично знайти джерело, повідомлення у вихідному або допоміжному файлі (файлах) і порівневому плані призначень |

4. Процедура розробки нового проекту в системі автоматизованого проектування MAX+PLUS II

Процедуру розробки нового проекту від концепції до завершення можливо спрощено представити наступним чином:

1. створення нового файлу проекту або ієрархічної структури декількох файлів проекту з використанням різних редакторів розробки проекту в системі MAX+PLUS II, тобто графічного, текстового і сигнального редакторів;

2. присвоєння імені файлу проекту верхнього рівня (Top of hierarchy) як імені проекту (Project name);

3. призначення родини програмувальних логічних інтегральних схем для реалізації проекту. Користувач може сам призначати конкретний пристрій або передати цю дію компілятору з метою оцінки наявних ресурсів;

4. відкриття вікна компілятора і його запуск кнопкою “Start” для початку компіляції проекту. Якщо користувач бажає, він може підключати модуль витягу часових затримок Timing SNF Extractor для створення файлу розводки, що використовується при тестуванні часових параметрів;

5. у випадку успішної компіляції – тестування і часовий аналіз, для проведення якого необхідно виконати наступні дії:

5.1. для проведення часового аналізу відкрити вікно “Timing Analyzer”, вибрати режим аналізу і натиснути кнопку “Start”;

5.2. для проведення тестування треба спочатку створити файл каналу тестування (*.scf), використовуючи сигнальний редактор, або в файлі вектора тестування (*.vec), використовуючи текстовий редактор;

6. програмування або завантаження конфігурації синтезованого приладу відбувається шляхом запуску програматора (Programmer) с наступною вставкою пристрою в програмувальний адаптер програматора MPU (Master Programming Unit) або за допомогою підключення пристрою MasterBlaster, ByteBlaster або кабелю завантаження FLEX (FLEX Download Cable) до приладу, що програмується в системі;

7. вибір кнопки “Program” для програмування приладу з пам’яттю EPROM (MAX, EPC) або вибір кнопки Configure для завантаження конфігурації приладу з пам’яттю типа SRAM (FLEX).

При роботі в системі MAX+PLUS II слід відрізняти різницю між файлами проекту, допоміжними файлами і проектами.

Файл проекту – це графічний, текстовий або сигнальний файл, створений за допомогою графічного або сигнального редактора редактору середовища MAX+PLUS II. Цей файл містить логіку проекту і обробляється компілятором. Компілятор автоматично обробляє наступні файли проекту:

1) графічні файли проекту (*.gdf);

2) текстові файли проекту на мові AHDL (*.tdf);

3) сигнальні файли проекту (*.wdf);

4) файли проекту на мові VHDL (*.vhd);

5) файли проекту на мові Verilog (*.v);

6) схемні файли OrCAD (*.sch);

7) вхідні файли EDIF (*.edf);

8) файли формату Xilinix Netlist (*.xnf);

9) файли проекту Altera (*.adf);

10) файли цифрового автомату (*.smf).

Допоміжні файли – це файли, що пов’язані з проектом MAX+PLUS II, але вони не є частиною ієрархічного дерева проекту. Більшість таких файлів не містить опису логічних функцій проекту. Деякі з них створюються автоматично додатками системи MAX+PLUS II, інші – користувачем.

Проект складається зі всіх файлів ієрархічної структури дизайну, в тому числі допоміжних і вхідних файлів. Ім’ям проекту є ім’я файлу верхнього рівня без розширення. Система MAX+PLUS II виконує компіляцію, тестування, часовий аналіз і програмування відразу всього проекту, хоча користувач може в цей час редагувати файли цього проекту в рамках іншого проекту.

Для кожного проекту слід створювати окремий підкаталог в робочому каталозі системи (\max2work).

При запуску системи MAX+PLUS II автоматично відкривається її головне вікно (Main Window) (рис. 4.1), меню, що охоплює всі додатки системи. В самому верхньому рядку написано ім’я останнього проекту, з яким працював користувач. Два наступні рядки є типовим для Windows: рядок основного меню і панель інструментів, в лівій частині якої знаходяться звичайні інструменти Windows (New, Open, Save, Print, Cut, Copy, Paste, Undo), а в правій – специфічні інструменти пакета, за допомогою яких відбувається запуск основних додатків пакету.

Рис. 4.1. Головне вікно системи автоматизованого проектування MAX+PLUS II

Запуск компонентів системи зручно проводити через вікно меню MAX+PLUS II (рис. 4.2), що містить в собі вкладене підменю виклику основних додатків: огляд ієрархії, графічний редактор, символьний редактор, текстовий редактор, сигнальний редактор, порівневий планувальник, компілятор, симулятор, аналізатор часових параметрів, програматор та генератор повідомлень, функціональне призначення яких вже описано в попередньому розділі.

В ієрархічній структурі проекту на будь-якому рівні дозволяється змішане використання файлів з розширеннями .gdf, .tdf, .vhd, .v, .edf, .sch. Однак, файли з розширенням .wdf, .xnf, .adf, .smf повинні бути або на самому нижньому ієрархічному рівні проекту, або бути єдиним файлом.

У всіх доданках MAX+PLUS II є можливість за допомогою команд з меню “Assign” (Призначити) вводити, редагувати і знищувати типи призначених ресурсів, пристроїв, і параметрів, які керують компіляцією проекту, логічним синтезом і розділенням на частини. На рис. 4.3 представлено команди меню Assign. Користувач може робити призначення для плинного проекту незалежно від того, чи відкритий будь-який файл проекту або вікно додатків.

Рис. 4.2. Вікно меню MAX+PLUS II Рис. 4.3. Меню призначень проекту Assign

Система MAX+PLUS II зберігає інформацію для проекту в файлі з розширенням .acf. Зміна призначень, зроблених у вікні порівневого планувальника також зберігаються в форматі .acf. Крім того, користувач має можливість редагувати acf-файл проекту в текстовому редакторі.

Наступні функції є загальними для всіх додатків MAX+PLUS II: призначення пристрою, ресурсів і зондів, збереження попередніх версій, глобальні опції пристрою в проекті, глобальні параметри проекту, глобальні вимоги до часових параметрів проекту, глобальний логічний синтез проекту.

Ресурс є частиною пристрою Altera, як, наприклад контакт або логічний елемент, який виконує конкретне, визначене користувачем завдання. Керування компіляцією проекту і його часовими параметрами здійснюється за допомогою різноманітних призначень. Існують наступні типи призначень.

Clique assignment (призначення кліка) – задає які саме логічні функції повинні залишатись разом. Групування логічних функцій в кліки гарантує, що вони реалізуються в одному і тому ж блоці логічної структури пристрою, одному ряді або пристрої.

Chip assignment (призначення чіпа) – задає які логічні функції повинні бути реалізовані в одному і тому ж пристрої у випадку розділення проекту на частини (декілька пристроїв).

Pin assignment (призначення виводу) – призначає вхід або вихід однієї логічної функції, такої, як примітив або мегафункція, конкретному контакту або горизонтальному (вертикальному) ряду виводів ПЛІС.

Location assignment (призначення вічка) – задає розміщення логічної функції (вузла) в конкретному логічному елементі. В полях даного вікна можна задати номер виводу, логічний осередок або блок, а також, використовуючи кнопки “Change” і “Delete”, змінити призначення.

Probe assignment (призначення зонду) – присвоює легке для запам’ятання унікальне ім’я входу чи виходу логічної функції.

Connected pin assignment (призначення з’єднаних виводів) – задає зовнішнє поєднання двох або більше виводів на схемі користувача. Дана інформація корисна і в режимі тестування часових параметрів схеми і при тестуванні декількох скомпонованих проектів.

Local routing assignment (призначення місцевого трасування) – присвоює коефіцієнт розподілення за виходом вузла логічного елементу, що знаходиться в тому ж блоці логічних елементів або ж у сусідньому блоці логічних елементів, суміжним з обраним вузлом, з використанням місцевих зв’язків. Місцеве трасування також здійснюється між вузлом, що поміщений в блок логічних елементів на периферії пристрою, і вихідним контактом, з яким він поєднаний. Призначення місцевого трасування здійснюється за допомогою команди “Assign/Local routing”.

Device assignment (призначення пристрою) – призначає тип ПЛІС, в якому буде втілений плинний проект. Якщо проект складається з декількох пристроїв, то дана функція здійснює призначення чіпів конкретним пристроям. Можна також вибрати опцію Auto і надати компілятору право обирати пристрій з заданої родини пристроїв. Процесом автоматичного вибору пристрою можна керувати, задаючи діапазон і число пристроїв в родині. Якщо проект є занадто великим для реалізації в одному пристрої, можна задати тип і число додаткових пристроїв. Для вибору пристрою використовується команда “Assign/Device”.

Logic option assignment (призначення логічної опції) – керує синтезом окремих логічних функцій під час компіляції з використанням стилю логічного синтезу і окремих опцій логічного синтезатора. Фірма Altera забезпечує велику кількість логічних опцій, і також готових стилів, кожний з яких уявляє собою зібрання установок для логічних опцій, об’єднане одним іменем стилю синтезу (Synthesis style). Користувач може використовувати готові стилі або створювати нові. Стилі синтезу дозволяють настроювати опції синтезу на певні родини пристроїв, враховуючи при цьому архітектуру родини. Для налагодження стилів синтезу використовується команда “Assign/Logic Options”.

Timing assignment (призначення часових параметрів) – керує логічним синтезом і підгонкою окремих логічних функцій з метою отримання необхідних значень для часу затримки. Користувач також може вирізати з’єднання між шляхами для конкретного сигналу та іншими осередками або блоками проекту. Призначення часових параметрів блоку відбувається за командою “Assign/Timing Requirements”.

Можна вводити глобальні часові вимоги для проекту, задаючи загальні характеристики для часу затримки, використовуючи команду “Assign/Global Project Timing Requirements”.

Для призначення глобальних параметрів логічного синтезу проекту використовують команду “Assign/Global Project Logic Synthesis”.

5. Процедура компіляції створеного проекту в системі автоматизованого проектування MAX+PLUS II

Спочатку компілятор дістає інформацію про ієрархічні зв’язки між файлами проекту і перевіряє проект на звичайні помилки введення дизайнів. Він створює організаційну карту проекту і потім, комбінуючи всі файли проекту, перетворює їх в базу даних без ієрархії, яку він здатен ефективно обробляти.

Компілятор використовує різноманітні засоби збільшення ефективності проекту і мінімізації використання ресурсів пристрою. Якщо проект занадто великий, щоб бути реалізованим в одній програмувальній логічній інтегральній схемі – компілятор може автоматично розбити його на частини для реалізації в декількох пристроях того ж самого сімейства програмувальних логічних інтегральних схем, при цьому мінімізуються число з’єднань між пристроями. В файлі звітності (.rpt) буде відображено яким чином проект реалізуватиметься: в одному або декількох пристроях.

Компілятор може автоматично компілювати проект. Існують можливості задати обробку проекту у відповідності з точними вказівками розробника. Наприклад, можливо задати стиль логічного синтезу проекту та інші параметри логічного синтезу в рамках всього проекту. Крім того, зручно задавати часові вимоги в рамках всього проекту, точно вказати розбиття великого проекту на частини для реалізації в декількох пристроях і обрати варіанти параметрів пристроїв, що будуть використані для всього проекту в цілому. Користувач здатний обирати кількість виводів і логічних елементів, які залишатимуться не використаними під час плинної компіляції, щоб зарезервувати їх для наступних модифікацій проекту.

Компіляцію можна запустити з будь-якого додатку MAX+PLUS II з вікна компілятора. Компілятор автоматично обробляє всі вхідні файли плинного проекту.

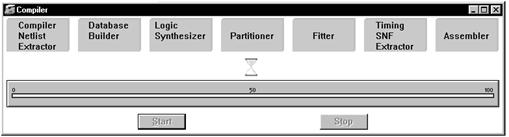

Процес компіляції можна бачити у вікні компілятора (рис. 5.1) в наступному вигляді:

1) спустошується і перевертається пісковий годинник, що вказує на активність компілятора;

2) висвітлюються, за чергою, прямокутники модулів компілятора;

3) під прямокутником модуля компілятора з’являється піктограма вихідного файлу, що був генерований даним модулем;

4) відсоток завершення компіляції поступово збільшується (до 100%);

5) під час розбиття та монтажу кнопка компілятора Stop (Стоп) перетворюється в кнопку Stop/Show Status (Стоп/Показати стан), яку користувач може вибрати для відкриття діалогового вікна, в якому відображається плинний стан розбиття і монтажу проекту;

6) при виявленні в процесі компіляції будь-яких помилок або можливих проблем автоматично відкривається вікно обробника повідомлень, в якому відображається список повідомлень про помилку, що попереджують та інформаційних повідомлень, а також відразу дається довідка по виправленню помилки. Крім того, користувач може визначити джерела повідомлень в файлах проекту або в його порівневому плані призначень.

Рис. 5.1. Процес компіляції проекту

Компілятор системи автоматичного проектування MAX+PLUS II обробляє проект, використовуючи наступні модулі та утиліти:

1) екстрактор списку ланцюгів (Compiler Netlist Extractor), що включає програми для читання форматів EDIF, VHDL, Verilog, XNF;

2) будівник бази даних (Database Builder);

3) логічний синтезатор (Logic Synthesizer);

4) роздільник (Partitioner);

5) трасувальник (Fitter);

6) екстрактор для функціонального тестування (Functional SNF Extractor);

7) екстрактор для тестування часових параметрів (Timing SNF Extractor);

8) екстрактор для тестування компонування (Linked SNF Extractor);

9) програма для запису вихідного файла в формат EDIF (EDIF Netlist Writer);

10) програма для запису вихідного файла в формат Verilog (Verilog Netlist Writer);

11) програма для запису вихідного файла в формат VHDL (VHDL Netlist Writer);

12) модуль асемблера (Assembler);

13) утиліта діагностики проекту (Design Doctor Utility).

Модуль екстрактора форматів (Compiler Netllist Extractor) перетворює кожний файл проекту в один або декілька двійкових файлів з розширенням .cnf (compiler netlist file). Оскільки компілятор підставляє значення всіх параметрів, що використовуються в параметризованих функціях, вміст cnf-файлу може змінюватись при послідовній компіляції, якщо значення параметрів змінюється. Даний модуль також створює і файл ієрархічних взаємозв’язків, з розширенням .hif (hierarchy interconnect file). В цьому файлі документуються ієрархічні зв’язки між файлами проекту, а також інформація, необхідна для показу ієрархічного дерева у вікні “Hierarchy Display”. Крім того, даний модуль створює файл бази даних вузлів з розширенням .ndb (node database), в якому містяться імена вузлів проекту для бази даних призначень ресурсів.

Модуль будівника бази даних (Database Builder) використовує файл ієрархічних зв’язків для компонування створених компілятором cnf-файлів, в яких міститься описання проекту. На основі даних про ієрархічну структуру проекту даний модуль копіює кожний cnf-файл в одну базу даних без ієрархічної структури. Таким чином, ця база даних зберігає електричні зв’язки проекту.

При створенні бази даних модуль досліджує логічну повноту та узгодженість проекту, а також перевіряє прикордонні зв’язки і наявність синтаксичних помилок. На цій стадії компіляції виявляється більшість помилок, які можуть бути тут же легко виправлені. Кожний модуль компілятора послідовно обробляє і поновлює цю базу даних.

Перший раз, коли компілятор обробляє проект, всі файли проекту компілюються. Користувач має можливість обрати “швидку повторну компіляцію” (smart recompile) для створення розширеної бази даних проекту, що дозволяє прискорити наступні компіляції. Використовуючи можливість повної повторної компіляції (total recompile), є можливість зробити вибір між повторною компіляцією лише тих файлів, які редагувались після останньої компіляції, і повною повторною компіляцією.

Модуль логічного синтезу (Logic Synthesizer) використовує ряд алгоритмів, що зменшує використання ресурсів і прибирають дубльовану логіку, забезпечуючи тим самим ефективне використання структури логічного елемента для архітектури цілої родини пристроїв. Крім того логічний синтезатор шукає логіку для не поєднаних вузлів. Якщо він знаходить такий вузол, він прибирає примітиви, що відносяться до такого вузла.

Якщо проект не вміщується при монтажі в одному пристрої, модуль роздільника (Partitioner) розділяє базу даних на декілька ПЛІС однією і тіє ж самої родини, намагаючись при цьому розділити проект на мінімальну кількість пристроїв.

Використовуючи базу даних, поновлену модулем розбиття, модуль трасування (Fitter) приводить у відповідність вимоги проекту з відомими ресурсами одного або декількох пристроїв. Він призначає кожній логічний функції положення логічного елемента, що її реалізує та обирає відповідні шляхи взаємозв’язків і призначень виводів.

Екстрактор для функціонального тестування (Functional SNF Extractor) створює файл для функціонального тестування з розширенням .snf. Компілятор генерує цей файл перед синтезом проекту, він містить всі вузли, що присутні в початкових файлах проекту.

Екстрактор для тестування часових параметрів (Timing SNF Extractor) створює, якщо компіляція проекту пройшла без помилок, файл для тестування часових параметрів, що містить дані про часові параметри проекту. Розширення файлу також - .snf.

Екстрактор для тестування компонування (Linked SNF Extractor) створює файл (.snf) для тестування компонування декількох проектів (на рівні плати). Такий файл комбінує інформацію з snf-файлів двох типів: для тестування часових параметрів і функціонального тестування, що були синтезовані для цих декількох проектів окремо.

Програма для запису вихідного файла в формат EDIF (EDIF Netlist Writer). Компілятор MAX+PLUS II може взаємодіяти з більшістю стандартних програмних засобів системи автоматичного проектування, що можуть читати файли стандартного формату EDIF 200 або EDIF 300. Даний модуль компілятора, що містить програму запису в формат EDIF, створює один або декілька файлів в форматі EDIF, з розширенням .edo.

Програма для запису вихідного файла в формат Verilog (Verilog Netlist Writer). Необов’язковий модуль програми запису в формат Verilog генерує вихідні файли з розширенням .vo, що містять інформацію про функції та їх часові параметри, отримані після проведення синтезу.

Програма для запису вихідного файла в формат VHDL (VHDL Netlist Writer). Необов’язковий модуль компілятора з програмою запису в формат VHDL генерує один або декілька вихідних файлів (.vho) на мові VHDL з синтаксисом 1987 або 1993.

Модуль асемблера (Assembler) перетворює призначення логічних елементів, виводів і пристроїв, зроблених модулем трасування, в програмний образ для пристрою у вигляді одного або декількох двійкових об’єктних файлів для програматора (.pof) і об’єктних файлів SRAM (.sof).

Утіліта діагностики проекту (Design Doctor Utility) перевіряє логіку кожного файлу проекту з метою виявлення елементів, які можуть викликати проблеми надійності на системному рівні. Ці проблеми виявляються лише після запуску пристрою “в залізі”. Існує можливість обирати одне з трьох попередніх правил обробки проекту з різними рівнями.

6. Загальні відомості про мову описання апаратури AHDL

Мова описання апаратури AHDL (Altera Hardware Description Language) розроблена фірмою Altera і призначена для описання комбінаційних і послідовних логічних пристроїв, групових операцій, цифрових автоматів з урахуванням особливостей ПЛІС фірми Altera. Він повністю інтегрується з системою автоматичного проектування MAX+PLUS II. Файли описання апаратури, написані на мові AHDL, мають розширення .tdf (Text design file). Для створення tdf-файлу можна використовувати як текстовий редактор системи MAX+PLUS II, так і будь-який інший. Проект, виконаний у вигляді tdf-файлу, компілюється і використовується для формування файлу програмування або завантаження ПЛІС фірми Altera.

Оператори та елементи мови AHDL є достатньо потужними та універсальними засобами описання алгоритмів функціонування цифрових пристроїв. Мова описання апаратури AHDL дає можливість створювати ієрархічні проекти в рамках однєї цієї мови або ж в ієрархічному проекті використовувати як tdf-файли, написані на мові AHDL, так і інші типи текстового описання апаратури. Для створення проектів на AHDL можна, звичайно, користуватись будь-яким текстовим редактором, але текстовий редактор системи MAX+PLUS II надає ряд додаткових можливостей для введення, компіляції і верифікації проекту.

Файли, створені на мові AHDL, легко інтегруються в ієрархічну структуру проекту. Система MAX+PLUS II дозволяє автоматично створювати символ компонента, алгоритм функціонування якого описано tdf-файлом, а потім вставити його в файл схемного описання (gdf-файл). Додатково, користувач може вводити власні функції, крім розроблених фірмою Altera близько 300 макрофункцій. Для всіх функцій, включених до макробібліотеки системи MAX+PLUS II, фірма Altera поставляє файли з розширенням .inc (include design file).

При розподіленні ресурсів пристроїв проектувальник може користуватись програмами текстового редактору або операторами мови AHDL. Крім того, розробник може перевірити синтаксис і зробити повну компіляцію. Будь-які помилки автоматично фіксуються обробником повідомлень та інформація про їх наявність з’являється у вікні текстового редактору, що оптимізує час розробки пристрою.

7. Реалізація в інтегрованому середовищі MAX+PLUS II базових пристроїв мікроелектроніки

7.1 Теоретичні відомості про тригери

Базовою структурною одиницею для побудови комбінаційних логічних схем є логічний елемент (вентиль). У випадку послідовних логічних схем роль такої структурної одиниці відіграє тригер. В даному розділі дипломної роботи буде розглянуто різні види тригерів.

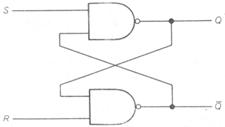

7.1.1 RS-тригер

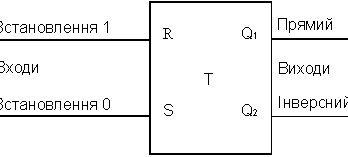

Умовне позначення RS-тригеру подано на рис. 7.1.1: RS-тригер має два входи R і S та два виходи Q1 та Q2. В тригерах виходи завжди знаходяться в протилежних (компланарних) станах. Іншою мовою, якщо на вході Q1 ми маємо логічну одиницю, то на виході Q2 буде рівень логічного нуля, і навпаки.

Входи R і S розглядуваного тригера називають відповідно входом встановлення 1 і входом встановлення 0.

|

|

|

|

|

|

|

Рис. 7.1.1. Умовне позначення RS-тригеру

Принцип роботи RS-тригеру ілюструє його таблиця дійсності (табл. 7.1.1).

Табл. 1.1. Таблиця дійсності RS-тригеру

| Режим роботи | Входи | Виходи | |||

| S | R |

Q1 |

Q2 |

Вплив на вихід Q1 |

|

| Заборонений стан | 0 | 0 | 1 | 1 |

Заборонено – не використовується |

| Встановлення 1 | 0 | 1 | 1 | 0 |

Для встановлення Q1 в 1 |

| Встановлення 0 | 1 | 0 | 0 | 1 |

Для встановлення Q1 в 0 |

| Збереження | 1 | 1 |

Q1 |

Q2 |

Залежить від попереднього стану |

При поданні на обидва входи тригера рівня логічного нуля (R=S=0) на обох виходах встановлюється логічна одиниця (Q1=Q2=1). Це заборонений стан тригеру; він не використовується. Згідно другому рядку таблиці дійсності на виході Q1 встановлюється логічна 1. В даному випадку кажуть, що тригер встановлений у стан 1. Згідно третього рядка, при S=1 і R=0 відбувається скидання сигналу на вході Q1 (очищення виходу Q1) до рівня логічного 0. Це значить, що тригер встановлено у стан 0. Четвертий рядок таблиці дійсності відповідає R=S=1. В даному випадку тригер знаходиться в стані спокою: на виходах Q1 і Q2 зберігаються попередні комплементарні рівні сигналу. Це режим збереження.

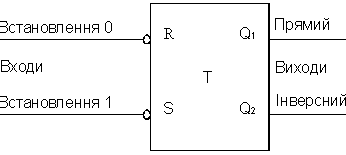

Із табл. 7.1.1 видно, що встановлення тригеру у стан 1 (встановлення 1 на виході Q1) ініціює логічний 0 на вході S. Аналогічно встановлення тригеру в стан 0 (встановлення 0 на виході Q1) ініціює логічний 0 на вході R. Так як зміна стану RS-тригеру обумовлена появою 0 на одному з його входів, то вірогідніше, точнішим зображенням даної схеми було б умовне графічне зображення, приведене на рис. 7.1.2.

Рис. 7.1.2. Умовне графічне позначення RS-тригеру

Рис. 7.1.3. RS-тригер, побудований на логічних елементах І-НЕ

Особливу увагу треба звернути на інвертуючі кола у входів R та S. Вони показують, що активним рівнем сигналу для встановлення тригеру в стан 1 і 0 є рівень логічного 0 на одному із входів. RS-тригер часто називають RS-фіксатором, або тригером з роздільними входами.

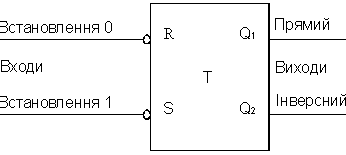

7.1.2 Синхронний RS-тригер

Умовне графічне позначення для синхронного RS-тригеру показано на рис. 7.1.4. Воно подібне до звичайного RS-тригеру; відмінність полягає в появі одного додаткового, так званого синхронізуючого входу, що позначається CLK.

Рис. 7.1.4. Умовне графічне позначення синхронного RS-тригеру

Принцип роботи синхронного RS-тригеру ілюструє його таблиця дійсності (табл. 7.1.2).

Табл. 7.1.2. Таблиця дійсності синхронного RS-тригеру

| Режим роботи | Входи | Виходи | ||||

| CLK | S | R |

Q1 |

Q2 |

Вплив на вихід Q1 |

|

| Збереження |

|

0 | 0 | Без змін | Без змін | |

| Встановлення 0 |

|

0 | 1 | 0 | 1 |

Для встановлення Q1 в 0 |

| Встановлення 1 |

|

1 | 0 | 1 | 0 |

Для встановлення Q1 в 1 |

| Заборонений стан |

|

1 | 1 | 1 | 1 |

Заборонено – не використовується |

Тільки верхні три рядки таблиці дійсності описують реальні режими роботи RS-тригеру. Нижній рядок відповідає забороненому стану і ніколи не використовується. З таблиці видно, що стан виходів синхронного RS-тригеру може змінюватись лише в моменти приходу тактових імпульсів. В даному випадку кажуть, що тригер працює синхронно: процес переключення його знаходиться в синхронізмі з тактовими імпульсами.

Важливу роль в багатьох цифрових схемах відіграє ще одна характеристика RS-тригеру – наявність пам’яті. Дійсно, якщо тригер встановлений в стан 1 або 0, то він залишається в такому стані навіть при деяких змінах вхідних сигналів.

Рис. 7.1.5. Синхронний RS-тригер, побудований на логічних елементах І-НЕ

Щоб отримати синхронний RS-тригер, в схему звичайного RS-тригеру потрібно ввести два додаткових логічних елемента І-НЕ, як показано на рис. 7.1.5.

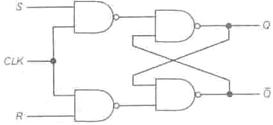

7.1.3 D-тригер

Умовне графічне позначення D-тригеру подано на рисунку 7.1.6. У цього тригера є лише один інформаційний вхід D, а також синхронізуюзуючий вхід CLK.

D-тригер часто називають тригером з затримкою. Слово “затримка” означає те, що відбувається з даними (інформацією), що поступає на вхід D. Інформаційний сигнал (0 або 1), поступаючи на цей вхід затримується у тригері рівно на один такт, перед тим як з’явитись на виході Q.

Рис. 7.1.6. Умовне графічне позначення D-тригеру

Спрощена таблиця дійсності для D-тригеру подана нижче.

Табл. 7.1.3. Таблиця дійсності D-тригеру

| Вхід | Вихід |

|

Dn |

Qn+1 |

| 0 | 0 |

| 1 | 1 |

Слід звернути увагу, що сигнал на виході Q в такті n+1 повторює сигнал, що був на вході D в попередньому такті n.

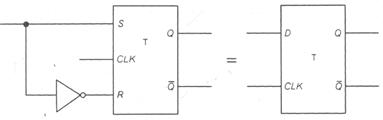

D-тригер можливо отримати з тактуємого RS-тригеру, додаючи до останнього інвертор, як показано на рис. 7.1.7.

Рис. 7.1.7. Схема D-тригера

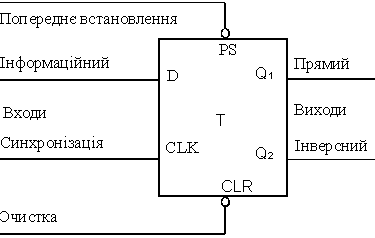

На рис. 7.1.8 показано умовне позначення типового серійно випускаємого D-тригеру. Він має два додаткових входи – попереднього встановлення (PS) і очищення (CLR). Логічний 0 на вході PS ініціює встановлення логічної 1 на виході Q. Логічний 0 на вході CLR ініціює очистку виходу Q.

В активних станах входи PS і CLR блокують дію входів D і CLK; при розблокуванні входи D і CLK діють аналогічно звичайному D-тригеру, що зображений на рис. 7.1.6.

|

|

|

Рис. 7.1.8. Умовне графічне позначення серійного інтегрального D-тригеру

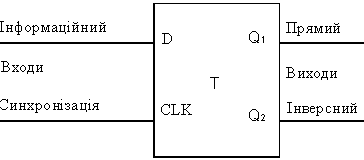

7.1.4 JK-тригер

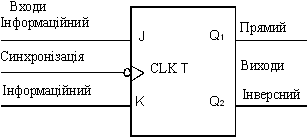

JK-тригер – це універсальний тригер, що має характеристики всіх інших типів тригерів. Умовне графічне позначення JK-тригеру подано на рис. 7.1.9. JK-тригер має два інформаційні входи: J і K, і вхід синхронізації CLK і, як і всі тригери два комплементарних виходи Q1 і Q2. Таблиця дійсності для JK-тригера приведена в табл. 7.1.4. Коли на обидва входи J і K подається рівень логічного 0, тригер блокується, і стан його виходів не змінюється. В цьому випадку тригер знаходиться в режимі збереження.

|

|

Рис. 7.1.9. Умовне графічне позначення JK-тригеру

Табл. 7.1.4. Таблиця дійсності JK-тригеру

| Режим роботи | Входи | Виходи | ||||

| CLK | J | K |

Q1 |

Q2 |

Вплив на вихід Q1 |

|

| Збереження |

|

0 | 0 | Без змін |

Без змін – блокування |

|

| Встановлення 0 |

|

0 | 1 | 0 | 1 |

Скидання або очищення Q1 в 0 |

| Встановлення 1 |

|

1 | 0 | 1 | 0 |

Для встановлення Q1 в 1 |

| Переключення |

|

1 | 1 | Переключення |

Зміна стану на протилежний |

Рядки 2 і 3 таблиці дійсності описують режими, що відповідають встановленню тригера в стани 0 на 1. Рядок 4 ілюструє дуже важливий режим роботи JK-тригера – переключення. Якщо на обох входах J і K встановлена логічна 1, то наступні тактові імпульси будуть викликати перекидання рівнів сигналів на виходах тригера від 1 до 0, от 0 до 1 і так далі. Така робота подібна переключенню тумблера, звідки і походить назва режиму.

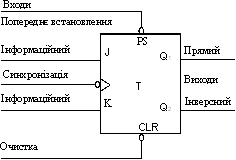

Умовне графічне позначення JK-тригера, що входить до складу інтегральної схеми показано на рис. 7.1.10. В порівнянні з тригером на рис. 7.1.9 даний тригер має два додаткових асинхронних входи (вхід попереднього встановлення і вхід очищення).

Синхронними входами є інформаційні входи J та K і синхронізуючий вхід CLK.

Рис. 7.1.10. Умовне графічне позначення серійного інтегрального JK-тригеру

При реалізації тригерів за допомогою мови AHDL доцільно користуватись примітивами тригерів.

В табл. 7.1.5 наведено всі примітиви тригерів, що використовуються при описанні роботи апаратури.

Табл. 7.1.5. Примітиви тригерів в AHDL

| Примітив | Прототип примітиву |

| DFF |

FUNCTION DFF (D, CLK, CLRN, PRN) RETURNS (Q) |

| DFFE |

FUNCTION DFFE (D, CLK, CLRN, PRN, ENA) RETURNS (Q) |

| TFF |

FUNCTION TFF (T, CLK, CLRN, PRN) RETURNS (Q) |

| TFFE |

FUNCTION TFFE (T, CLK, CLRN, PRN, ENA) RETURNS (Q) |

| JKFF |

FUNCTION JKFF (J, K, CLK, CLRN, PRN) RETURNS (Q) |

| JKFFE |

FUNCTION JKFFE (J, K, CLK, CLRN, PRN, ENA) RETURNS (Q) |

| SRFF |

FUNCTION SRFF (S, R, CLK, CLRN, PRN) RETURNS (Q) |

| SRFFE |

FUNCTION SRFFE (S, R, CLK, CLRN, PRN, ENA) RETURNS (Q) |

| LATCH |

FUNCTION LATCH (D, ENA) RETURNS (Q) |

Виводи тригерів:

D, T, J, K, S, R – інформаційні входи;

CLK – вхід тактового сигналу (активний перепад 0->1);

CLRN – вхід асинхронного скидання тригера (активний рівень – логічний нуль);

PRN – вхід асинхронного встановлення тригера (активний рівень – логічний нуль);

ENA – вхід дозволу роботи (активний рівень – логічна одиниця).

7.1.5 Програма реалізації тригерів в інтегрованому середовищі MAX+PLUS II

Програма для реалізації тригерів за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд:Title "triggers";

Subdesign triggers

(

D,T,J,K,S,R,CLK,CLRN,PRN,ENA : input;

Q1,Q2,Q3,Q4,Q5,Q6,Q7,Q8,Q9 : output;

)

Begin

Q1 = DFF(D,CLK,CLRN,PRN); Q2 = DFFE (D,CLK,CLRN,PRN,ENA);

Q3 = TFF (T,CLK,CLRN,PRN); Q4 = TFFE (T, CLK, CLRN, PRN, ENA);

Q5 = JKFF (J, K, CLK, CLRN, PRN);

Q6 = JKFFE (J,K, CLK, CLRN, PRN, ENA);

Q7 = SRFF (S, R, CLK, CLRN, PRN);

Q8 = SRFFE (S, R, CLK, CLRN, PRN, ENA);

Q9 = LATCH (D, ENA);

End;

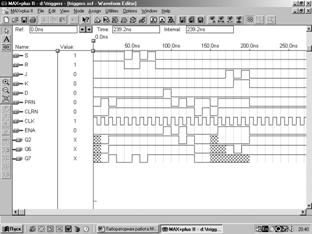

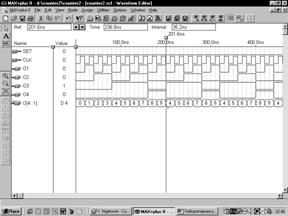

7.1.6 Результати програмної реалізації тригерів

На рис. 7.1.11 зображено вікно сигнального редактору проекту “triggers”.

Рис.7.1.11. Результати тестування RS-, D-, JK-тригерів

7.2 Теоретичні відомості про регістри

7.2.1 Послідовні регістри зсуву

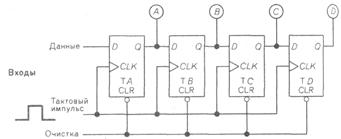

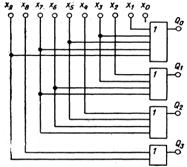

Схема одного з типових регістрів зсуву подана на рис. 7.2.1. Цей регістр реалізований на 4 D-тригерах. Такий регістр має назву 4-розрядний регістр зсуву, оскільки він дозволяє зберігати 4 двійкових розряди даних А, B, C, D.

Рис.7.2.1. 4-розрядний послідовний регістр зсуву

За допомогою табл. 7.2.1 і рис. 7.2.1 ми маємо можливість спостерігати за роботою цього пристрою. Спочатку очистимо регістр (встановимо рівні логічного нуля на його виходах А, B, C, D). Для цього потрібно подати логічний 0 на вхід очищення CLR. Отриманому стану регістра зсуву відповідає рядок 1 табл. 7.2.1 До приходу тактового імпульсу виходи регістру залишаються в стані 0000. Подамо перший імпульс на синхронізуючий вхід CLK; індикатор покаже число 1000 (рядок 3 в табл. 7.2.1), оскільки на тактовому імпульсі логічна 1 з інформаційного входу тригера TA переноситься на його логічний вихід Q. Тепер при наявності логічної 1 на інформаційному вході регістру ця одиниця з кожним тактовим імпульсом вводиться в розряд А, а введені раніше одиниці зсуваються на одну позицію (розряд) вправо (тактові імпульси 2 і 3 в табл. 7.2.1). Таким самим чином при подачі на інформаційний вхід логічного 0 цей нуль при кожному тактовому імпульсі вводиться в розряд А, а введені раніше одиниці та нулі зсуваються вправо (тактові імпульси 4-8 в табл. 7.2.1). Перед приходом тактового імпульсу 9 на інформаційному вході встановлюється 1, а перед приходом імпульсу 10 цей вхід повертається до 0. В час дії тактових імпульсів 9-13 введена в регістр на імпульсі 9 одиниця буде зміщуватись на індикаторі вправо. Рядок 15 в табл. 7.2.1 показує, на імпульсі 13 ця одиниця покидає крайній правий розряд регістру зсуву і втрачається.

Табл.7.2.1. Робота 4-розрядного регістру зсуву

| Входи | Виходи | ||||||

|

Номер рядка |

Очищення | Дані | Номер тактового імпульсу | TА | TB | TC | TD |

| А | B | C | D | ||||

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 2 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

| 3 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| 4 | 1 | 1 | 2 | 1 | 1 | 0 | 0 |

| 5 | 1 | 1 | 3 | 1 | 1 | 1 | 0 |

| 6 | 1 | 0 | 4 | 0 | 1 | 1 | 1 |

| 7 | 1 | 0 | 5 | 0 | 0 | 1 | 1 |

| 8 | 1 | 0 | 6 | 0 | 0 | 0 | 1 |

| 9 | 1 | 0 | 7 | 0 | 0 | 0 | 0 |

| 10 | 1 | 0 | 8 | 0 | 0 | 0 | 0 |

| 11 | 1 | 1 | 9 | 1 | 0 | 0 | 0 |

| 12 | 1 | 0 | 10 | 0 | 1 | 0 | 0 |

| 13 | 1 | 0 | 11 | 0 | 0 | 1 | 0 |

| 14 | 1 | 0 | 12 | 0 | 0 | 0 | 1 |

| 15 | 1 | 0 | 13 | 0 | 0 | 0 | 0 |

Нагадаємо, що D-тригер називають також тригером з затримкою. Він просто передає інформаційний сигнал з входу D на вихід Q з затримкою на один такт.

Прилад, схема якого приведена на рис. 7.2.1 має назву послідовного регістру зсуву. Термін “послідовний” відображає той факт, що в цей регістр дані вводяться порозрядно. Наприклад, щоб ввести в регістр двійкову комбінацію 0111 треба пройти всю послідовність станів від рядка 1 до рядка 6 в табл. 7.2.1. Послідовне завантаження 4-бітової комбінації 0111 в послідовний регістр відбувається за 5 тактів (рядок 2 можливо виключити).

Інший спосіб завантаження регістру – паралельне (або розширене) завантаження, при якому всі інформаційні біти вводяться в регістр одночасно “за командою” одного тактового імпульсу.

Регістр зсуву на рис. 7.2.1 можливо трансформувати в 5-розрядний, додав до схеми ще один D-тригер. Регістри зсуву частіше бувають 4-, 5- або 8-розрядними. В них можливо використання не тільки D-тригеру, але й тригерів іншого типу (наприклад, JK-тригера, або синхронних RS-тригерів).

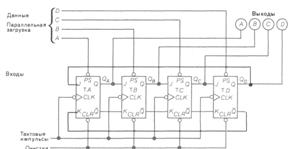

7.2.2 Паралельні регістри зсуву

Послідовний регістр зсуву, робота якого описана вище має два суттєві недоліки: він дозволяє вводити тільки по одному біту інформації на кожному тактовому імпульсі і, крім того, кожний раз при зсуві вправо втрачається крайній правий біт.

На рис. 7.2.2 показана схема 4-розрядного паралельного кільцевого регістру. Входи A, B, C, D вданому приладі є інформаційними.

Рис. 7.2.2. 4-розрядний паралельний кільцевий регістр зсуву

Цю систему можливо спорядити ще однією корисною характеристикою – можливістю кільцевого переміщення інформації, коли дані з входу приладу повертаються на його вхід і не втрачаються.

В даному регістрі зсуву використовуються чотири JK-тригери. Треба звернути увагу на зворотній зв’язок виходу тригера TD та входів J і K тригера ТА. Завдяки цьому ланцюгу зворотного зв’язку введена в регістр інформація, яка звично втрачається на виході тригеру TD, буде циркулювати по регістру зсуву. Сигналом очищення регістру (встановлення його виходів в стан 0000) є рівень логічного нуля на вході CLR.

Входи паралельного завантаження A, B, C, D пов’язані з входами попереднього встановлення тригерів PRN, що дозволяє встановлювати рівень логічної одиниці на будь-якому виході (A, B, C, D). Якщо на один з цих входів подати логічний 0, то на відповідному виході буде логічна 1. Подача тактових імпульсів на входи CLK всіх JK-тригерів призводить до зсуву інформації в регістрі вправо. З тригеру TD дані передаються в тригер ТА (кільцеве переміщення інформації).

Табл. 7.2.2. Робота 4-розрядного паралельного кільцевого регістру зсуву

| Входи | Виходи | |||||||||||

| Номер рядка | Очищення | Паралельне завантаження даних | Номер тактового імпульсу | TА | TB | TC | TD | |||||

| A | B | C | D | А | B | C | D | |||||

| 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | ||

| 2 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | ||

| 3 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | ||

| 4 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | ||

| 5 | 1 | 1 | 1 | 1 | 1 | 2 | 0 | 0 | 0 | 1 | ||

| 6 | 1 | 1 | 1 | 1 | 1 | 3 | 1 | 0 | 0 | 0 | ||

| 7 | 1 | 1 | 1 | 1 | 1 | 4 | 0 | 1 | 0 | 0 | ||

| 8 | 1 | 1 | 1 | 1 | 1 | 5 | 0 | 0 | 1 | 0 | ||

| 9 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | |||

| 10 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | |||

| 11 | 1 | 1 | 1 | 1 | 1 | 6 | 0 | 0 | 1 | 1 | ||

| 12 | 1 | 1 | 1 | 1 | 1 | 7 | 1 | 0 | 0 | 1 | ||

| 13 | 1 | 1 | 1 | 1 | 1 | 8 | 1 | 1 | 0 | 0 | ||

| 14 | 1 | 1 | 1 | 1 | 1 | 9 | 0 | 1 | 1 | 0 | ||

| 15 | 1 | 1 | 1 | 1 | 1 | 10 | 0 | 0 | 1 | 1 | ||

Табл. 7.2.2 допомагає зрозуміти принцип роботи паралельного регістру зсуву. При включенні живлення на виходах регістру встановлюється будь-яка двійкова комбінація, така, наприклад як в рядку 1 таблиці 7.2.2. Подача логічного 0 на входи CLR тригерів ініціює очищення регістру (рядок 2). Далі (рядок 3) відбувається завантаження в регістр двійкової комбінації 0100. Послідовні тактові імпульси викликають зсув введеної інформації вправо (рядки 4-8). Треба звернути увагу на рядки 5 і 6: одиниця з крайнього правого тригеру TD переноситься в крайній лівий тригер ТА. В даному випадку можливо говорити про кільцеве переміщення одиниці в регістрі.

Далі (рядок 9) заново ініціюється очищення регістру за допомогою входу CLR. Завантажується нова двійкова комбінація 0110 (рядок 10). Подача 5 тактових імпульсів (рядки 11-15) призводить до кільцевого зсуву інформації на 5 позицій вправо. Треба звернути увагу, що для повернення даних в початковий стан потрібно 4 тактових імпульси. Якщо в регістрі зсуву на рис. 2.2 розірвати ланцюг зворотного зв’язку, то ми отримаємо звичайний паралельний регістр зсуву; можливість кільцевого переміщення даних буде виключена.

7.2.3 Програма реалізації регістрів в інтегрованому середовищі MAX+PLUS II

Програма для реалізації 4-розрядного послідовного регістру зсуву за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд:

Title "register1";

Parameters

(WIDTH = 4); - встановлення розрядності регістру

Assert (WIDTH > 0) - перевірка розрядності регістру на відмінність від 0

Report "Value of WIDTH parameter must be greater then %" WIDTH

Severity Error;

Subdesign register1

(

D_INPUT, SET, RESET : input = GND; - вхідні сигнали

CLK : input; - вхід синхронізації

ENABLE : input = VCC; - вхід дозволу роботи

Q_OUTPUT : output; - вихідні сигнали

)

Variable

FF[WIDTH..1] : DFFE; - об'ява змінної FF, що належить до класу DFFE

Begin

FF[].clk = CLK;

FF[].prn = !SET;

FF[].clrn = !RESET;

FF[].ena = ENABLE;

FF[].d = (FF[WIDTH-1..1].q, D_INPUT);

Q_OUTPUT = FF[WIDTH].q;

End;

- Примітка: на часовій діаграммі:

- FF - двійкове число на виході регістру

Програма для реалізації 4-розрядного паралельного кільцевого регістру зсуву за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд:

Subdesign register2

Parameters

(WIDTH = 4); - встановлення розрядності регістру

Assert (WIDTH > 0) - перевірка розрядності тригера (більша від нуля)

Report "Value of WIDTH parameter must be greater then %" WIDTH

Severity Error;

(

I[WIDTH..1] : input = VCC; - вхідні сигнали (дані)

CLK : input;

RESET : input;

O[WIDTH..1] : output; - вихідні сигнали (дані)

)

Variable

FF[WIDTH..1] : JKFF; - об'ява змінної FF, що належить до класу JKFF

Begin

FF[WIDTH..1].j = (FF[WIDTH-1..1].q, FF[WIDTH].q);

FF[WIDTH..1].k = (!FF[WIDTH-1..1].q, !FF[WIDTH].q);

FF[WIDTH..1].clk = CLK;

FF[WIDTH..1].clrn = !RESET;

FF[WIDTH..1].prn = I[WIDTH..1];

O[WIDTH..1] = FF[WIDTH..1].q;

End;

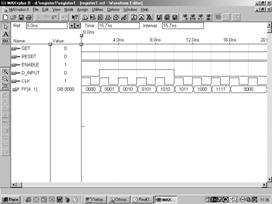

7.2.4 Результати програмної реалізації регістрів

На рис. 7.2.3 зображено вікно сигнального редактору проекту “register1”.

Рис. 7.2.3. Результати тестування 4-розрядного послідовного регістру зсуву

На рис. 7.2.4 зображено вікно сигнального редактору проекту “register2”.

Рис. 7.2.3. Результати тестування 4-розрядного паралельного кільцевого регістру зсуву

7.3 Теоретичні відомості про лічильники

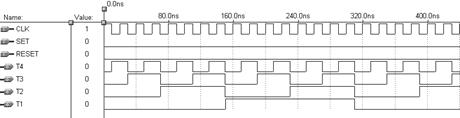

7.3.1 Лічильник з крізним переносом

Процедури двійкової і десяткової лічби ілюстровано в табл. 7.3.1. Використовуючи лише чотири двійкових розряди (T4, T3, T2, T1), ми можемо рахувати від 0000 до 1111 (від 0 до 15 в десятеричній системі відліку). Стовпчик T1 таблиці відповідає двійковому розряду одиниці або самій молодшій значимій цифрі. Зазвичай використовується термін “самий молодший розряд”. Стовпець T4 відповідає двійковому розряду вісімок або старшій значимій цифрі. Зазвичай використовується термін “самий старший розряд”. Зверніть увагу, що в стовпці одиниць цифри змінюються найчастіше. Якщо вам потрібний лічильник, що рахує від 0000 до 1111 в двійковій системі, у нього повинно бути 16 різних вихідних станів. Такий лічильник має назву лічильник за модулем 16. Модуль лічильника – це число різних станів, через які проходить лічильник в процесі одного повного циклу відліку.

Табл. 7.3.1. Відлікова послідовність для лічильника за модулем 16

| Двійкова лічба | Десяткова лічба | |||

| T4 | T3 | T2 | T1 | |

| 8 | 4 | 2 | 1 | |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 2 |

| 0 | 0 | 1 | 1 | 3 |

| 0 | 1 | 0 | 0 | 4 |

| 0 | 1 | 0 | 1 | 5 |

| 0 | 1 | 1 | 0 | 6 |

| 0 | 1 | 1 | 1 | 7 |

| 1 | 0 | 0 | 0 | 8 |

| 1 | 0 | 0 | 1 | 9 |

| 1 | 0 | 1 | 0 | 10 |

| 1 | 0 | 1 | 1 | 11 |

| 1 | 1 | 0 | 0 | 12 |

| 1 | 1 | 0 | 1 | 13 |

| 1 | 1 | 1 | 0 | 14 |

| 1 | 1 | 1 | 1 | 15 |

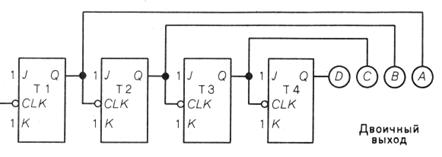

Функціональна схема лічильника за модулем 16, зібраного з чотирьох JK-тригерів, показана на рис 7.3.1. Кожний JK-тригер працює в режимі переключення (J = K = 1). Нехай в початковий момент часу стан виходів лічильника відповідає двійковому числу 0000 - лічильник очищений. При надходженні тактового імпульсу 1 на синхронізуючий вхід CLK тригера Т1 цей тригер переключається, при проходженні зрізу імпульсу, і на індикаторі з’являється число 0001. Лічба продовжується: зріз сигналу на виході кожного тригеру запускає наступний тригер. Повертаючись до табл. 7.3.1. ми бачимо, що цифри (1 або 0) в стовпці T1 (одиниць) змінюються на кожному етапі лічби. Іншими словами тригер Т1 переключається з приходом кожного нового тактового імпульсу. Як бачимо з стовпця T2, тригер Т2 переключається в два рази рідше від тригера Т1. Взагалі кожний старший розряд в табл. 7.3.1 переключається в два рази рідше попереднього.

Рис. 7.3.1. Логічна схема лічильника за модулем 16

Роботу лічильника за модулем 16 ілюструють часові діаграми на рис. 7.3.2. Синхронізуючому входу відповідає верхня діаграма. Діаграми для виходів Q регістрів Т4, Т3, Т2, Т1 наведено нижче.

Оскільки кожний тригер впливає тільки на один наступний за ним тригер, то для переключення всіх тригерів необхідний деякий час.

Ми бачимо, що зміна станів послідовно проходить по ланцюжку тригерів. Тому лічильник, що ми розглядаємо має назву лічильника з крізним переносом.

Рис. 7.3.2. Часова діаграма лічильника за модулем 16

Лічильник, функціональна схема якого показана на рис. 7.3.1, можливо назвати не тільки лічильником з крізним переносом, але й лічильником за модулем 16, 4-розрядним лічильником або асинхронним лічильником. Кожна з назв характеризує розглядувану схему з якогось одного боку.

Визначення “з крізним переносом” і “асинхронний” говорять про те, що запуск тригерів відбувається не в один і той же час. Назва “лічильник за модулем 16” віддзеркалює число різних станів, що “проходяться” лічильником за один повний цикл лічби. Визначення “4-розрядний” вказує на число двійкових розрядів на виході лічильника.

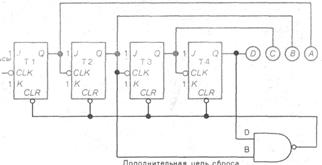

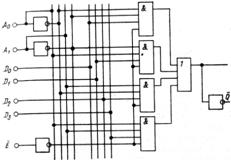

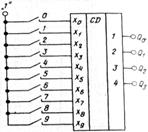

7.3.2 Асинхронний лічильник з модулем 10

Лічильник за модулем 10 рахує від 0000 до 1001 (від 0 до 9 в десятковій системі), тобто перші 10 комбінацій в табл. 7.3.1. Ми бачимо, що для цього потрібно чотири двійкових розряди: розряд одиниць, розряд двійок, розряд четвірок і розряд вісімок.

![]()

Рис. 7.3.3. Логічна схема лічильника за модулем 10

Такий лічильник можливо реалізувати на чотирьох тригерах, з’єднаних по схемі описаного вище асинхронного лічильника. В схему потрібно додатково ввести логічний елемент І-НЕ (рис. 7.3.3) для встановлення всіх тригерів в нульовий стан, очищення лічильника, з приходом десятого імпульсу (тобто з приходом першого імпульсу після того, як лічильник нарахував до 1001 – 9 в десятковій системі).

Принцип використання такого логічного елемента стає зрозумілим якщо розглянути яке двійкове число настає за 1001. З табл. 7.3.1 видно, що цим числом є 1010 (10 в десятковій системі). При поданні логічної 1 , що міститься в розрядах двійок і вісімок двійкового числа 1010, на входи логічного елемента І-НЕ (як показано на рис. 7.3.3), цей елемент встановить всі тригери в стан 0. Лічильник почне рахувати від 0000 до 1001. Таким чином, логічний елемент І-НЕ забезпечує встановлення лічильника в стан 0000. Подібне використання логічного елемента І-НЕ дозволяє створити лічильники з деякими іншими значеннями модуля. На рис. 7.3.3 показано функціональну схему асинхронного лічильника за модулем 10. Цей лічильник можливо також назвати декадним (десятковим) лічильником.

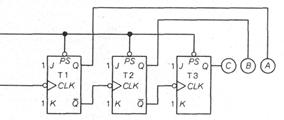

7.3.3 Лічильник віднімання

Вище було описано лічильники, що рахують в прямому напрямку (0, 1, 2,...). Однак в деяких цифрових системах з’являється необхідність рахування в зворотному напрямку (9, 8, 7, 6,...). Лічильники, які рахують від більших чисел до менших називають лічильниками віднімання, або лічильниками зворотної дії.

Схема асинхронного лічильника віднімання за модулем 8 показано на рис. 7.3.4, відповідна відлікова послідовність чисел наведена в табл. 7.3.2.

Рис. 7.3.4. Логічна схема асинхронного 3-розрядного лічильника віднімання

Табл. 7.3.2. Відлікова послідовність для 3-розрядного лічильника віднімання

|

Номер тактового імпульсу |

Двійкова відлікова послідовність | Десяткові числа | ||

| Т3 | Т2 | Т1 | ||

| 0 | 1 | 1 | 1 | 7 |

| 1 | 1 | 1 | 0 | 6 |

| 2 | 1 | 0 | 1 | 5 |

| 3 | 1 | 0 | 0 | 4 |

| 4 | 0 | 1 | 1 | 3 |

| 5 | 0 | 1 | 0 | 2 |

| 6 | 0 | 0 | 1 | 1 |

| 7 | 0 | 0 | 0 | 0 |

| 8 | 1 | 1 | 1 | 7 |

| 9 | 1 | 1 | 0 | 6 |

Треба звернути увагу на те, що схема лічильника віднімання нагадує схему лічильника прямої дії на рис. 7.3.1. Єдиною відмінністю є спосіб переносу від тригера Т1 до тригера Т2 і від тригера Т2 до тригера Т3. В лічильнику прямої дії синхронізуючий вхід кожного тригера пов’язаний з інверсним виходом Q попереднього тригера. Зауважимо, що в лічильнику відліку перед початком відліку в зворотному напрямку передбачене його попереднє встановлення в стан 111 (деcяткове число 7) за допомогою входу предвстановлення (PRN). Тригер Т3 – двійковий лічильник розряду одиниць (стовпець T1). Тригер Т2 – лічильник розряду двійок (стовпець T2). Тригер Т3 – лічильник розряду четвірок (стовпець T3).

7.3.4 Програми реалізації лічильників в інтегрованому середовищі MAX+PLUS II

Програма для реалізації 4-розрядного асинхронного лічильника з крізним переносом за модулем 16 за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд:

title "counter1";

parameters

(WIDTH = 4); - встановлення розрядності лічильника

assert (WIDTH > 0) - перевірка розрядності лічильника

report "Value of WIDTH parameter must be greater then %" WIDTH

severity error;

subdesign counter1

(

CLK : input; - імпульси синхронізації (CLK) лічильника

RESET : input; - імпульси зкидання (CLRN) тригерів лічильника

SET : input; - імпульси предвстановлеення (PRN) тригерів лічильника

O [WIDTH..1] : output; - вихід лічильника

)

variable

TRIGGER [WIDTH..1] : JKFF;

begin

TRIGGER [WIDTH..1].j = vcc;

TRIGGER [WIDTH..1].k = vcc;

TRIGGER [WIDTH..1].clrn = !RESET;

TRIGGER [WIDTH..1].prn = !SET;

TRIGGER [WIDTH].clk = !CLK;

TRIGGER [WIDTH-1..1].clk = !TRIGGER [WIDTH..2].q;

O [WIDTH..1] = TRIGGER [1..WIDTH].q;

end;

Програма для реалізації асинхронного лічильника за модулем 10 за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд:

title "counter2";

parameters

(WIDTH = 4); - встановлення розрядності лічильника

assert (WIDTH > 0) - перевірка розрядності лічильника

report "Value of WIDTH parameter must be greater then %" WIDTH

severity error;

subdesign counter2

(

CLK : input; - імпульси синхронізації (CLK) лічильника

SET : input; - імпульси предвстановлення (PRN) тригерів лічильника

O [WIDTH..1] : output; - вихід лічильника

)

variable

TRIGGER [WIDTH..1] : JKFF;

begin

TRIGGER [WIDTH..1].j = vcc;

TRIGGER [WIDTH..1].k = vcc;

TRIGGER [WIDTH..1].prn = !SET;

TRIGGER [WIDTH].clk = !CLK;

TRIGGER [WIDTH-1..1].clk = !TRIGGER [WIDTH..2].q;

TRIGGER [WIDTH..1].clrn = (TRIGGER [3].q !& TRIGGER [1].q);

O [WIDTH..1] = TRIGGER [1..WIDTH].q;

end;

Програма для реалізації 3-розрядного лічильника віднімання за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд:

title "counter3";

parameters

(WIDTH = 3); - встановлення розрядності лічильника

assert (WIDTH > 0) - перевірка розрядності лічильника

report "Value of WIDTH parameter must be greater then %" WIDTH

severity Error;

subdesign counter3

(

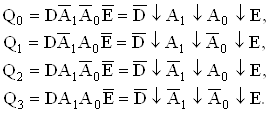

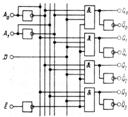

CLK : input; - імпульси синхронізації (CLK) лічильника