Курсовая работа: Розробка і оформлення конструкторської документації гібридних інтегральних мікросхем

Міністерство освіти і науки України

Вінницький національний технічний університет

Інститут автоматики, електроніки та комп’ютерних систем управління

Факультет ФЕЛТ

Кафедра ЛОТ

КУРСОВИЙ ПРОЕКТ

з дисципліни: “Радіокомпоненти та мікроелектронна технологія”

Розробка і оформлення конструкторської документації гібридних інтегральних мікросхем

Вінниця 2010

Зміст

Вступ

Розділ 1. Теоретичний аналіз існуючих технологій ГІМС

1.1 Особливості конструювання інтегральних мікросхем

1.2 Позначення параметрів інтегральних мікросхем

1.3 Вибір матеріалу підкладки

1.4 Вибір корпуса інтегральної мікросхеми

1.5 Переваги і недоліки гібридних інтегральних мікросхем

1.6 Технології виробництва ГІМС

Розділ 2. Розробка КД ГІМС

2.1 Розробка комутаційної схеми

2.2 Розрахунок плівкових та навісних елементів

2.3 Розрахунок орієнтовної площі плати та вибір її типорозміру

2.4 Розробка топології плати ГІМС

2.5 Топологічне креслення окремих шарів

2.6 Розробка складального креслення плати ГІМС

2.7 Розробка складального креслення ГІМС в корпусі

Висновки

Список використаних джерел

Додатки

Вступ

Інтегральні мікросхеми перетворюють і обробляють сигнал, а також мають високу щільність розміщення електрично з’єднаних елементів і компонентів. У напівпровідникових мікросхемах всі елементи і міжелементні з’єднання виконані в об’ємі і на поверхні напівпровідника [1].

Гібридними називаються ті мікросхеми, які складаються з елементів, компонентів і кристалів. Зараз гібридні інтегральні мікросхеми набули широкого застосування в електроніці і мікроелектроніці.

Особливістю конструювання ІМС є тісний зв’язок конструктивних рішень з технологією виготовлення елементів мікросхем. Для розробки ГІМС використовують метод плівкової технології, тобто радіоелементи одержують на підкладці у вигляді плівок напівпровідників, діелектриків, різних металів та їх оксидів, які послідовно наносять одна на одну. При розробці ГІМС враховується також геометрична форма плівкових елементів, бо чим простіша форма елемента, тим легше їх виробництво, більша точність виготовлення і надійність. Використання плівкових елементів у мікросхемі підвищує якість та зменшує економічні витрати на неї, а велика щільність розташування елементів і компонентів робить її економічно вигідною в виробництві і простою в застосуванні до приладу, а також сприяє збільшенню попит на неї [1].

Використання засобів мікроелектроніки – основа сучасного етапу розвитку усіх галузей радіо – та електронного приладобудування.

Застосування інтегральних схем в радіоелектронних системах дозволяє якісно покращити параметри апаратури та відкрило довгочасну перспективу її поетапного вдосконалення [1].

Основними конструктивними елементами ГІМС є:

- підкладка, на якій розміщуються пасивні і активні елементи;

- плівкові резистори, конденсатори, провідники, контактні площадки;

- навісні без корпусні напівпровідникові прилади;

- навісні мініатюрні пасивні елементи (конденсатори з ємностями великих номіналів), дроселі, трансформатори;

- корпус для герметизації мікросхем і закріплення її виводів.

Оптимальна конструкція ГІМС визначається факторами й суцільністю упаковки елементів, потужністю розсіювання, номіналами елементів і допускали на них, відсотком виходу придатних виробів, ціною та інше.

В даному курсовому проекті представлено розробку даної схеми, зокрема здійснено її розведення, топологію, вибір оптимальних розмірів за всіма відповідними правилами.

Розділ 1. Теоретичний аналіз існуючих технологій ГІМС

1.1 Особливості конструювання інтегральних мікросхем

Інтегральна мікросхема (ІМС) – електронний виріб, який виконує певні функції перетворення і обробки сигналу, який має високу густину розташування елементів, електрично з’єднаних, виготовлених в єдиному технологічному циклі [2].

Гібридна мікросхема – це електротехнічний виріб, який представляє елементи, електрично з’єднаних, виготовлених в єдиному технологічному циклі [2].

Гібридна мікросхема – це електротехнічний виріб, який представляє собою герметично закритий корпус з виводами, в середині якого міститься підкладка з розміщеними на ній плівковими та навісними елементами.

Особливістю конструювання ІМС є тісний зв’язок конструктивних рішень з технологією виготовлення елементів мікросхем.

Технологія виготовлення напівпровідникових інтегральних схем забезпечує одночасну групову обробку відразу великої кількості схем. Це визначає в значній мірі ідентичність схем по характеристиках. Напівпровідникові інтегральні схеми мають високу надійність за рахунок використання планарного процесу виготовлення й значного скорочення числа мікросполук елементів у процесі створення схем [2].

Напівпровідникові інтегральні схеми розвиваються в напрямку все більшої концентрації елементів у тому самому об'ємі напівпровідникового кристала, тобто в напрямку підвищення ступеня інтеграції інтегральної схеми. Розроблені інтегральні схеми, що містять в одному кристалі сотні й тисячі елементів. У цьому випадку інтегральна схема перетворюється в більшу інтегральну систему (БІС), що неможливо розробляти й виготовляти без використання електронних обчислювальних машин високої продуктивності [2].

В процесі розробки топологічної структури ІС розв’язують такі задачі: визначення геометричних розмірів елементів, які отримують методом плівкової технології; розробка схеми взаємного розміщення і з’єднання елементів на підкладці, визначення метода виготовлення плівкових елементів і способів під’єднання виводів плівкових і навісних елементів до контактних площадок і зовнішніх виводів; вибір кінцевої форми і розміщення плівкових елементів; оформлення креслень; оцінка якості топології мікросхеми і внесення коректив [2].

Інтегральна мікросхема (ІС) – електронний виріб, який виконує певні функції перетворення і обробки сигналу, який має високу густину пакування елементів, електрично з’єднаних, виготовлених в єдиному технологічному циклі [2].

Гібридна мікросхема – це електротехнічний виріб, який представляє собою герметично закритий корпус з виводами, в середині якого міститься підкладка з розміщеними на ній плівковими та навісними елементами.

Особливістю конструювання ІМС є тісний зв’язок конструктивних рішень з технологією виготовлення елементів мікросхем [2].

Технологія виготовлення напівпровідникових інтегральних схем забезпечує одночасну групову обробку відразу великої кількості схем. Це визначає в значній мірі ідентичність схем по характеристиках. Напівпровідникові інтегральні схеми мають високу надійність за рахунок використання планарного процесу виготовлення й значного скорочення числа мікросполук елементів у процесі створення схем.

Напівпровідникові інтегральні схеми розвиваються в напрямку все більшої концентрації елементів у тому самому об'ємі напівпровідникового кристала, тобто в напрямку підвищення ступеня інтеграції інтегральної схеми. Розроблені інтегральні схеми, що містять в одному кристалі сотні й тисячі елементів. У цьому випадку інтегральна схема перетворюється в більшу інтегральну систему (БІС), що неможливо розробляти й виготовляти без використання електронних обчислювальних машин високої продуктивності [2].

В процесі розробки топологічної структури ІС розв’язують такі задачі: визначення геометричних розмірів елементів, які отримують методом плівкової технології; розробка схеми взаємного розміщення і з’єднання елементів на підкладка, визначення метода виготовлення плівкових елементів і способів під’єднання виводів плівкових і навісних елементів до контактних площадок і зовнішніх виводів; вибір кінцевої форми і розміщення плівкових елементів; оформлення креслень; оцінка якості топології мікросхеми і внесення коректив [2].

Створення інтегральних схем розвивається по декількох напрямках: гібридні інтегральні схеми з дискретними активними елементами; напівпровідникові інтегральні схеми, виконані в монолітному блоці напівпровідникового матеріалу; сполучені інтегральні схеми, у яких активні елементи виконані в монолітному блоці напівпровідникового матеріалу, а пасивні елементи нанесені у вигляді тонких плівок; плівкові інтегральні схеми, у яких активні й пасивні елементи нанесені на підладку у вигляді тонких плівок [3].

Широке поширення одержали гібридні ІС, у яких пасивні елементи — плівкові, а активні елементи (діоди, транзистори) — навісні. Навісними елементами в мікроелектроніці називають мініатюрні, звичайно безкорпусні діоди і транзистори, що представляють собою самостійні елементи, що приклеюються («навішуються») у відповідних місцях до підкладки і з'єднуються тонкими провідниками з плівковими елементами схеми. Іноді в гібридних ІМС навісними можуть бути і деякі пасивні елементи, наприклад мініатюрні конденсатори з такою великою ємністю або котушки з такою індуктивністю, що їхній неможливо зробити у вигляді плівок. Це можуть бути і мініатюрні трансформатори. У деяких випадках у гібридних ІМС навісними є цілі напівпровідникові ІМС [3].

Плівкові ІМС мають підкладку (плату) з діелектрика (скло, кераміка й ін.). Пасивні елементи, тобто резистори, конденсатори, котушки і сполуки між елементами, виконуються у виді різних плівок, нанесених на підкладку. Активні елементи (діоди, транзистори) не робляться плівковими, тому що не вдається досягти їх кращої якості. Таким чином, плівкові ІМС містять тільки пасивні елементи і являють собою Кс-цепи (наприклад, Кс-фільтри) або які-небудь інші схеми [3].

Прийнято розрізняти ІМС тонкоплівкові, у яких товщина плівок не більш 2 мкм, і товстоплівкові товщина плівок яких значно більша. Різниця між цими ІМС полягає не стільки в товщині плівок, скільки в різній технології їхнього нанесення. Тонкоплівкові резистори по точності і стабільності краще товстоплівкових, але виробництво їх складніше і дорожче.

В основі виготовлення тонкоплівкових мікросхем лежить процес одержання тонких плівок (не більш як 1 мкм) методами термічного осадження (випари з наступним осадженням) у високому вакуумі або катодного розпилення іонним бомбардуванням у середовищі розрідженого інертного газу. Рисунок тонко-плівкової інтегральної мікросхеми одержують нанесенням плівки на певні ділянки підкладки за допомогою маски або видаленням за допомогою фотолітографії плівки, що покриває всю поверхню підкладки, яка являє собою платівку зі скла, ситалу, поликору та іншого діелектричного матеріалу, виготовленого з високим класом чистоти робочої поверхні [3].

1.2 Позначення параметрів інтегральних мікросхем

Максимальна вхідна напруга – найбільша вхідна напруга інтегральної мікросхеми, при якій вихідна напруга відповідає заданій. Мінімальна вхідна напруга – найменша вхідна напруга інтегральної мікросхеми, при якій вихідна напруга відповідає заданій. Чутливість – найменша вхідна напруга, при якій електричні параметри інтегральної мікросхеми відповідають заданим [4].

Діапазон вхідних напруг – інтервал напруг від мінімальної вхідної напруги до максимальної. Вхідна напруга спокою – напруга на вході інтегральної мікросхеми при відсутності вхідного сигналу. Вихідна напруга спокою – напруга на виході інтегральної мікросхеми при відсутності вхідного сигналу. Вхідна напруга обмеження – найменша вхідна напруга інтегральної мікросхеми, при якій наступає обмеження вихідної напруги. Вхідна напруга – напруга на вході інтегральної мікросхеми в заданому режимі. Напруга зсуву – напруга постійного струму на вході інтегральної мікросхеми, при якій вихідна напруга дорівнює нулю. Синфазні вхідні напруги – напруги між кожним із входів інтегральної мікросхеми й спільним виводом, амплітуди й фази яких збігаються. Максимальні синфазні вхідні напруги – синфазні вхідні напруги, при яких параметри інтегральної мікросхеми змінюються на задане значення. Максимальна вихідна напруга – найбільша вихідна напруга, при якій зміни параметрів інтегральної мікросхеми відповідають заданим. Мінімальна вихідна напруга – найменша вихідна напруга, при якій зміни параметрів інтегральної мікросхеми відповідають заданим. Вихідна напруга балансу – напруга постійного струму на кожному виході інтегральної мікросхеми щодо спільного виводу при напрузі між виводами, рівній нулю. Приведена до входу напруга шумів – відношення напруги власних шумів на виході інтегральної мікросхеми при закороченому вході до коефіцієнта підсилення напруги [4].

Нижня гранична частота смуги пропускання – найменша частота, на якій коефіцієнт підсилення інтегральної мікросхеми зменшується на 3 дБ щодо заданої. Верхня гранична частота смуги пропускання – найбільша частота, на якій коефіцієнт підсилення інтегральної мікросхеми зменшується на 3 дБ щодо заданої частоти. Смуга пропускання – діапазон частот між верхньою й нижньою граничними частотами смуги пропускання.

Вхідний струм – струм, що протікає у вхідному ланцюзі інтегральної мікросхеми в заданому режимі. Різниця вхідних струмів – різниця струмів, що протікають через входи інтегральної мікросхеми в заданому режимі. Вихідний струм – струм, що протікає в ланцюзі навантаження інтегральної мікросхеми в заданому режимі. Максимальний вихідний струм – найбільший вихідний струм, при якому забезпечуються задані параметри інтегральної мікросхеми. Мінімальний вихідний струм – найменший вихідний струм, при якому забезпечуються задані параметри інтегральної мікросхеми. Струм споживання – струм, споживаний інтегральною мікросхемою від джерел живлення в заданому режимі. Струм холостого ходу – струм, споживаний інтегральною мікросхемою при відключеному навантаженні [4].

Коефіцієнт підсилення напруги – відношення вихідної напруги мікросхеми до вхідної. Коефіцієнт підсилення струму – відношення вихідного струму до вхідного. Коефіцієнт підсилення потужності – відношення вихідної потужності інтегральної мікросхеми до вхідної. Коефіцієнт нелінійності амплітудної характеристики – найбільше відхилення крутості амплітудної характеристики щодо крутості амплітудної характеристики, що змінюється за лінійним законом. Коефіцієнт прямокутності амплітудно-частотної характеристики – відношення смуги частот на рівні 0,01 або 0,001 до смуги пропускання на рівні 0,7. Коефіцієнт нерівномірності амплітудно-частотної характеристики – відношення максимального виходу напруги до мінімального в заданому діапазоні частот смуги пропускання, виражене в децибелах [4].

Вхідна ємність – відношення ємнісного реактивного складового вхідного струму до добутку кругової частоти на синусоїдальну вхідну напругу мікросхеми при заданій частоті сигналу. Вихідна ємність – відношення ємнісного реактивного складового вихідного струму до добутку кругової частоти на викликану ним вихідну напругу при заданій частоті сигналу.

Вхідний опір – відношення приросту вхідної напруги до приросту активної складової вхідного струму при заданій частоті сигналу. Вихідний опір – відношення приросту вихідної напруги до активного складового вихідного постійного або синусоїдального струму при заданій частоті сигналу [4].

1.3 Вибір матеріалу підкладки

Важливим складовим елементом гібридної мікросхеми є підкладка, яка одночасно виконує декілька функцій:

- відводить тепло, яке виділилось на елементах і компонентах;

- служить основою для кріплення всіх елементів і компонентів;

- ізолює елементи один від одного.

Тому до матеріалу, з якого виготовляється підкладка, незалежно від конструкції та призначення мікросхеми ставлять слідуючи вимоги:

- матеріал, з якого виготовляють підкладки повинен мати чисту, гладку поверхню, яка дозволяє отримати чіткий малюнок, та відтвореність електричних параметрів;

- матеріал повинен мати високу механічну міцність, при відносно малій товщині;

- мати мінімум дефектів, які впливають на якість отриманої мікросхеми;

- повинен мати високу теплопровідність, для ефективного відводу тепла від елементів і активних компонентів;

- стійкість до хімічних речовин, які використовують в усіх технологічних процесах, при виготовленні мікросхеми;

- матеріал повинен мати високий питомий опір;

- повинен мати близькі коефіцієнти термічного розширення підладки і нанесених плівок;

1.4 Вибір корпуса інтегральної мікросхеми

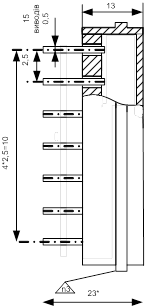

Для гібридних мікросхем найчастіше використовують три види корпусів – металоскляний квадратний чи прямокутний, металоскляний циліндричний [4].

В залежності від конструкції і матеріалу корпуси мікросхем герметизують різними методами. Так, наприклад, металосклянні і металокерамічні герметизують сваркою або пайкою, керамічні – пайкою, а пластмасові – вакуумною заливкою, листовим пресуванням або склеюванням.

Головна перевага металоскляного корпусу це забезпечення надійної роботи мікросхеми в умовах підвищеної вологості і в широкому температурному інтервалі.

В металоскляних корпусах кришка і частково дно формуються з металу. На дні знаходиться скляна пластина, в яку впаяно виводи. Кришка і дно з’єднуються по периметру за допомогою сварки.

Температурні коефіцієнти лінійного розширення скляної пластини (основи) і виводів повинні бути найближчими, інакше при нагрівані корпусу це може призвести до порушення герметичності між виводами і скляною пластиною і навіть до руйнування скла. Тому при проектуванні і виготовленні металоскляних корпусів на підбір цих коефіцієнтів приділяють велику увагу [4].

Найчастіше для виготовлення корпусів використовують сплави ТКР-29НК, 29НК-В4; сталь Х18Н10Т; скло С48-2, С52-1

1.5 Переваги і недоліки гібридних інтегральних мікросхем

Переваги:

1. Гібридна технологія дозволяє відносно швидко створювати електронні прилади, які виконують достатньо складні функції.

2. Обладнання для виготовлення гібридної інтегральної мікросхеми значно дешевше ніж для виготовлення напівпровідникових інтегральних мікросхем.

3. Перевагою гібридних технологій є більший відсоток виходу працездатних мікросхем 60-80%, порівняно з 5-30% для напівпровідникових інтегральних мікросхем. Брак, який виникає при виготовленні гібридних інтегральних мікросхем часто можна усунути.

4. Підладка гібридної інтегральної мікросхеми виготовлена з високоякісного діелектричного матеріалу, тому через малі паразитні ємності і гарну взаємну ізоляцію елементів і компонентів, гібридні інтегральні мікросхеми мають кращі високочастотні і імпульсні електричні властивості, тому у високочастотному і надвисокочастотному діапазоні переважно використовуються гібридні інтегральні мікросхеми [5].

Гібридні інтегральні мікросхеми мають вищу радіаційну стійкість.

Недоліки:

1. Мала надійність, через те, що використовується навісний монтаж.

2. Більші габарити і вага.

Неможливість отримання активних елементів в єдиному технологічному циклі з пасивними [5].

1.6. Технології виробництва ГІМС

Напівпровідникова мікросхема — це така мікросхема, де всі елементи і між елементні з'єднання виконані на одному напівпровідниковому кристалі (наприклад, кремнію, германія, арсеніду галію).

- Товсто-плівкова інтегральна схема;

- Тонко-плівкова інтегральна схема.

Гібридна мікросхема — крім напівпровідникового кристалу містить деяку кількість безкорпусних діодів, транзисторів й інших електронних компонентів, поміщених в один корпус.

Вид оброблюваного сигналу:

- Аналогові

- Цифрові

- Аналого-цифрові

Аналогові мікросхеми — вхідні і вихідні сигнали змінюються за законом безупинної функції в діапазоні від позитивного до негативної напруги живлення [5].

Цифрові мікросхеми — вхідні і вихідні сигнали можуть мати два значення: логічний чи нуль логічна одиниця, кожному з який відповідає визначений діапазон напруги. Наприклад, для мікросхем ТТЛ-логіки при живленні +5 В діапазон напруги від 0 до 0,8 В відповідає логічному нулю, а діапазон від 2,4 до 5 В відповідає логічній одиниці. Для мікросхем ЕСЛ-логіки при живленні 5,2 В: логічна одиниця — це 0,8 - 1,03 В, а логічний нуль — це 1,6 - 1,75 В.

Аналого-цифрові мікросхеми сполучають у собі форми цифрової й аналогової обробки сигналів. В міру розвитку технологій одержують усе більше поширення.

Основним елементом аналогових мікросхем є транзистори (біполярні чи польові). Різниця в технології виготовлення транзисторів істотно впливає на характеристики мікросхем. Тому нерідко в описі мікросхеми вказують технологію виготовлення, щоб підкреслити тим самим загальну характеристику властивостей і можливостей мікросхеми. У сучасних технологіях поєднують технології біполярних і польових транзисторів, щоб досягти поліпшення характеристик мікросхем [5].

- Мікросхеми на уніполярних (польових) транзисторах — найбільш економічні (по споживанню струму):

- КМОП-логіка (комплементарна МОП-логіка) — кожен логічний елемент мікросхеми складається з пари взаємодоповнюючих (комплементарних) польових транзисторів (n-МОП і p-МОП).

Мікросхеми на біполярних транзисторах:

- РТЛ — резисторно-транзисторна логіка (застаріла, замінена на ТТЛ);

- ДТЛ — діод-транзисторна логіка (застаріла, замінена на ТТЛ);

- ТТЛ — транзисторно-транзисторна логіка — мікросхеми зроблені з біполярних транзисторів із багато-емітерними транзисторами на вході;

- ТТЛШ — транзисторно-транзисторна логіка з діодами Шотки — удосконалена ТТЛ, у якій використовуються біполярні транзистори з ефектом Шотки.

- ЕСЛ — еміттерно-звязана логіка — на біполярних транзисторах, режим роботи яких підібраний так, щоб вони не входили в режим насичення, — що істотно підвищує швидкодію.

КМОП і ТТЛ (ТТЛШ) технології є найбільш поширеними логіками мікросхем. Де небхідно заощаджувати споживання струму, застосовують КМОП-технологію, де важливіше швидкість і не потрібно економія споживаної потужності застосовують ТТЛ-технологію. Слабким місцем КМОП-мікросхем є уразливість від статичної електрики — досить торкнутися рукою висновку мікросхеми і її цілісність уже не гарантується. З розвитком технологій ТТЛ і КМОП мікросхеми по параметрах зближаються і як наслідок, наприклад, серія мікросхем 1564 — зроблена за технологією КМОП, а функціональність і розміщення в корпусі як у ТТЛ технології [5].

Мікросхеми, виготовлені по ЕСЛ-технології є найшвидшими, але найбільш енергоспоживаючими і застосовувалася при виробництві обчислювальної техніки, коли найважливішим параметром була швидкість обчислення. У СРСР самі продуктивні ЕОМ типу ЄС106х виготовлялися на

ЕСЛ-мікросхемах. Зараз ця технологія використовується рідко [5].

Очищення підкладок перед напилюванням виконують для видалення механічних і жирових забруднень. Очищення проводять на двох взаємопов'язаних напівавтоматах вібраційного хімічного очищення, камери яких заповнюють розчином перекису водню. Підкладки поміщають у касету і завантажують у центрифугу, де вони очищуються від механічних домішок. Потім підкладки перекладають в робочу камеру напівавтомата для промивання. На другому напівавтоматі відбувається очищення підкладок у перекисно-аміачному розчині та їх промивання після очищення.

Напилювання резистивного шару виконують іоноплазмовим методом, який має такі переваги у порівнянні з методом термічного випаровування у вакуумі: можливість автоматизації процесу напилювання; відсутність наважок; тривалий термін служби мішені; високе відтворення тонкоплівкових резисторів, а також високі електрофізичні властивості напилених шарів; підвищена адгезія напиленого шару з підкладкою [5].

Сутність процесу напилювання електропровідних шарів (ванадій-мідь і ванадій-алюміній) полягає в осадженні на підкладку атомів вихідного матеріалу, що випаровуються в результаті впливу високої температури й електричного поля. Напилювання ведеться на установці "УВН-2-М2" у два етапи: на першому етапі проводиться напилювання шару з ванадію; на другому - напилювання провідного шару з міді чи алюмінію.

Виготовлення й очищення наважок, застосовуваних для напилювання провідних шарів, проводиться на спеціально обладнаному робочому місці. Розчини для очищення наважок (для ванадія, міді і алюмінію, обробленого в лузі, - розчин азотної кислоти в деіонізованій воді, для алюмінію - розчин гідрату окису калію в деіонізованій воді) готують оператори. Саме очищення ведеться у витяжній шафі занурюванням у ванну з фторопласта, армованого титановою сіткою [5].

Завдяки простоті, гнучкості і постійному удосконаленню технологія

Товсто-плівкових мікросхем усе ширше застосовується у виробництві. Із застосуванням електронно-обчислювальних машин і створенням гнучких автоматизованих систем виробництва, переходом до безлюдного виробництва досягається вивільнення значної кількості робочих місць, поліпшення умов праці і підвищення культури виробництва.

У вітчизняній практиці використовуються автоматизовані комплекси, побудовані на агрегатно-модульному принципі. Кожний автоматизований модуль оснащений завантажувально-розвантажувальними пристроями. Устаткування, об'єднане в комплекс, дозволяє виготовляти 600 мікрозборок за 1 годину. Технологічне устаткування, що легко вбудовується в автомати-чні лінії: автомати трафаретного друку, лазерної підгонки і контролю, роботизовані робочі місця для укладання електрорадіоелементів на підкладки, автоматичні завантажувально-розвантажувальні пристрої, успішно застосовується при виготовленні гібридних інтегральних мікросхем невеликими партіями, а за необхідності його легко перебудувати на випуск нових виробів. Тому технологію товсто-плівкових мікросхем і мікрозборок застосовують для дрібносерійних і дослідних партій [5].

Розділ 2. Розробка конструкторської документації ГІМС

2.1 Розробка комутаційної схеми

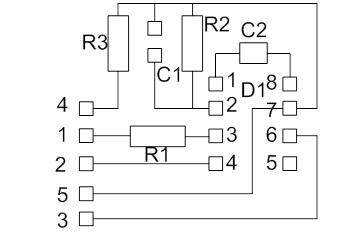

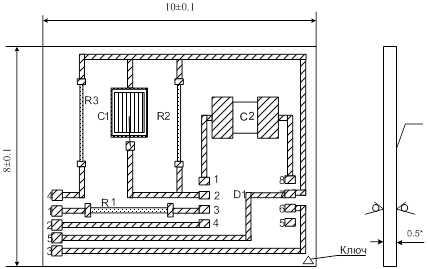

Розробка комутаційної схеми з’єднань включає в себе перетворення даної електричної схеми з метою складання схематичного плану розміщення елементів і з’єднань між ними на платі мікросхеми.

При проектуванні топології ГІМС необхідно зважити на те, що:

-розмір підкладки вибирають відповідно до табл.2; В даній роботі він 12*8.

-периферійні контактні площадки розташовують по чотирьох чи двох протилежних боках підкладки (для лінійних ГІМС допускається розміщення з одного боку).

-кожна гібридна ІМС повинна мати ключ-збільшену контактну площадку чи спеціальний знак, розміщений в нижньому лівому куту на більшому боці підкладки; ключ креслять в процесі проектування топології. В роботі ключ поставлений у верхньому лівому куті.

Мінімальна ширина провідника-50мкм.

Провідники розводяться таким чином, щоб вони не перетиналися в одній площі. Якщо це неможливо, тоді ставляться перемички. В даній схемі перемичок немає, виводи не перетинаються.

Мінімальна ширина плівкових провідників 0.05 мм.

Мінімальна відстань від дротяного провідника чи виводу до краю контактної площини, чи до краю плівкового провідника, не захищеного ізоляцією 0.2 мм.

Відстань від кристала до контактної площадки не менше 0.4 мм. Розміри контактної площадки min 0.4*0.4. Форма прямокутна.

Відстань. Мінімальна відстань між контактними площадками, доріжками і резисторами-0.2 мм.

Мінімально допустима відстань від плівкових елементів до краю плати 200 мкм (резистори, доріжки).

Відстань від кристала до контактної площадки не менше 0.4 мм.

Контактні площадки розташовують на відстані не менше 500 мкм від краю підкладки.

Рисунок 2. Комутаційна схема

2.2 Розрахунок плівкових та навісних елементів

Для розробки ГІМС нам дана схема електрично-принципова. Схема електрично принципова – це документ, який визначає повний склад електричних елементів і електричного зв’язку між ними. Вона дає детальну уяву про принципи роботи нашого виробу. По схемі розроблюють конструкцію, а також використовують її при виготовленні і експлуатації виробу.

За електричною схемою розробляється мікросхема. Мікросхема-пристрій розміром порядку 1мм2 і менше; зазвичай виконує яку-небудь самостійну функцію, наприклад складання поданих на неї електричних імпульсів, і називається інтегральною. Окремі елементи мікросхеми, наприклад провідники, резистори, можуть бути утворені шляхом нанесення плівок на діелектричну пластинку-підкладку (плівкові елементи). Це плівкова технологія виготовлення. Інші елементи, які називаються навісними, наприклад напівпровідникові діоди і транзистори, приклеюють і припаюють до підкладки. При поєднанні тих і інших елементів утворюється мікросхема, яка називається гібридною. В даній роботі на ГІМС будуть такі елементи: два конденсатори, три резистора і навісна мікросхема 740 УД5-1.

Електрична принципова схема по вказаному завданню на форматі А4-схема і перелік елементів схеми. Відстань таблиці переліку від верхньої рамки не регламентовано, тому можна витягнути схему на всю довжину листа, якщо треба, а таблицю змістити вниз.

Відстань між умовними позначеннями не потрібно занадто збільшувати, розміщення елементів повинно визначатись зручністю читання схеми, їх можна креслити з поворотом на кути кратні 900. Електричні зв’язки між елементами зображують найкоротшими лініями мінімальною кількістю перетинів, на відстані не менше 3 мм одне від одного. Входи, виходи та контакти розташовують справа і зліва. Порядок запису в перелік елементів схеми, спочатку резистори, потім інші елементи в алфавітному порядку умовних позначень.

В межах кожної групи елементів, ті які входять в неї записують під загальним заголовком, по зростанню порядкових номерів. В кінці групи рекомендується пусту стрічку для доповнень.

Далі розрахуємо компоненти ГІМС, розведемо схему. Компонентами ГІМС є діоди та діодні матриці, транзистори, конденсатори, трансформатори та ін. Компоненти можуть мати жорсткі та гнучкі виводи і спосіб монтажу компонентів на плату повинен забезпечити фіксацію положення компонента і виводів, збереження його цілісності, параметрів і якостей, стійкість до вібрацій та ударів. Перейдемо до розрахунку конкретної схеми.

Користуючись заданими параметрами (U=5 В, табл. 1), розрахуємо площі плівкових резисторів.

Почнемо розрахунки з визначення потужності P і сили струму I, за формулами [4]:

;

; ![]() ; (2.1)

; (2.1)

Напруга U для схеми дорівнює 9 В

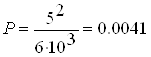

Для R1

(Вт)

(Вт)

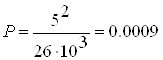

Для R2, R3:

(Вт)

(Вт)

Таблиця 2-Параметри елементів схеми

| Поз.позначення | Тип елементу і його номінал | Кількість | Примітки |

| С2 | Конденсатор К10-17-ІВ...0,01 мкФ (навісний елемент) | 1 |

В=1,4 мм; L=1,9 мм Рис.6 |

| С1 | 220 пФ 15%(плівковий елемент) | 1 | |

| D1 | Мікросхема 740 УД-5-І (навісний елемент) | 1 | Рис.5 |

| Резистори (плівкові елементи) | |||

| R1 | 6кОм 10% | 1 | |

| R2, R3 | 26кОм 10% | 2 |

![]() (mА)

(mА)

Розрахуємо геометричні розміри резисторів:

R1: (плівковий)

Кількість квадратів

![]()

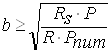

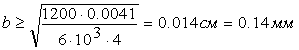

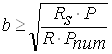

a) Розрахуємо ширину b резистора за формулою [4]:

, (2.2)

, (2.2)

![]() і

і ![]() беремо з таблички (оскільки схема

не потребує високої точності і `не розсіює багато тепла, то беремо кермет).

беремо з таблички (оскільки схема

не потребує високої точності і `не розсіює багато тепла, то беремо кермет).

Тому ![]() Вт/см2,

Вт/см2, ![]() Ом/мм2.

Ом/мм2.

б) Розрахуємо довжину ![]() резистора R1 знаходимо за

формулою [4]:

резистора R1 знаходимо за

формулою [4]:

, (2.3)

, (2.3)

![]()

в) Тепер за формулою ![]() визначимо площу резистора R1

визначимо площу резистора R1

![]()

R2, R3 (плівковий).

Кількість квадратів

![]()

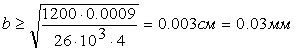

a) Розрахуємо ширину b резисторів за формулою [4]:

, (2.4)

, (2.4)

;

;

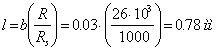

б) Визначимо довжину резисторів за формулою [3]:

, (2.5)

, (2.5)

в) Тепер розрахуємо площу резисторів [2]:

![]() .

.

Розрахуємо геометричні розміри конденсаторів C1, С2

Розрахуємо площу конденсатора С1, він буде плівковим

![]() (2.6)

(2.6)

де С0 питома ємність

Для того щоб знайти питому ємність С0 підберемо

матеріал діелектрика. Виберемо моноокис кремнію в таблиці основних електричних

і експлуатаційних властивостей плівкових конденсаторів [5]. Випишемо його

параметри ε=5 (діелектрична проникність діелектрика), tgδ=0,03

(тангенс кута втрат), Eпр= 2* ![]() В/см (напруженість електричноо

поля)

В/см (напруженість електричноо

поля)

З формули пробивної напруги знайдемо товщину конденсатора

Епр= ![]() => d=

=> d= ![]() (2.7)

(2.7)

d= ![]() =7.5

=7.5 ![]()

![]()

Далі знайдемо питому ємність конденсатора

С0=0.0885 ![]() (ε/d) (2.8)

(ε/d) (2.8)

C0=0.0885![]() (5/7.5

(5/7.5![]() )=59 (пФ/

)=59 (пФ/![]() )

)

Підставимо знайдену питому ємність у формулу (1.6) та знайдемо його площу

S=  =3.7

=3.7![]()

Розрахуємо площу навісного конденсатора С2

![]() .

.

Розрахуємо площу мікросхеми D1

![]()

2.3 Розрахунок орієнтовної площі плати та вибір її типорозміру

Розрахуємо орієнтовану площу плати.

Для визначення мінімально допустимої площі плати ГІМС, необхідно провести площі під кожний вид плівкових і навісних елементів: резисторів, конденсаторів, контактних площадок, дискретних компонентів. Площу плати визначають по формулі:

![]() (2.9)

(2.9)

Для цього:

1) Розрахуємо площу резистивного шару [5]:

![]()

2) Розрахуємо площу кон тактних площадок:

![]()

![]()

Отже, ![]()

2.4 Розробка топології плати ГІМС

Основною особливістю конструювання напівпровідникових інтегральних схем являється необхідність врахування взаємозв’язку між параметрами елементів, що створюються тим чи іншим способом, з яких створюються елементи, фізичними процесами в них і технологією виготовлення. Розміри і форму кожного елементу мікросхеми задають фотошаблоном і режимом локальної дифузії, тобто підбираючи розміри фотошаблону, концентрацію домішок, режими дифузії і т.п., можна створювати елементи параметрами, що вимагаються.

Розробка топології – основний етап в проектуванні напівпровідникових інтегральних схем, на якому вирішуються питання компоновки елементів мікросхеми і з’єднань між ними. Для цього попередньо аналізується принципова електрична схема, вибрана для інтегрального виконання.

Розробку топології проводимо від третьої особи в такій послідовності: складання комутаційної схеми з’єднання елементів на платі; розрахунок конструкцій плівкових елементів; визначення необхідної площі плати і узгодження з типорозміром корпуса, вибраного для ГІМС; розробка ескізу топології; оцінка якості розробленої топології і при необхідності її коректування.

Для складання схеми з’єднань на принциповій електричній схемі плівкові елементи і навісні компоненти, послідовність їх розташування і проводить спрощення схеми з’єднань з метою зменшення кількості перетинів провідників і зменшення їх довжини.

Далі приступають до розробки ескізу топології. На цьому етапі розв’язують задачу оптимального розміщення на платі плівкових елементів, навісних компонентів і з’єднань між ними, а також між зовнішніми контактними площадками на платі і виводами корпуса.

Для розробки ескізних топологічних креслень необхідно знати: схему електричну принципову і схему з’єднань елементів; форму і геометричні розміри плівкових елементів і навісних компонентів; орієнтовні розміри і матеріал плати, попередньо вибраний метод індивідуальної герметизації, вид і розміри корпуса чи метод встановлення плати в блоці при груповій герметизації.

Загальними принципами проектування топологічної структури є:

-мінімізація площі, яку займають елементи і схема в цілому;

-мінімізація кількості перетинів міжелементних з’єднань;

-рівномірне розміщення елементів по площі підкладки;

-мінімізація кількості матеріалів, які застосовуються для реалізації плівкових елементів;

-підвищення ступеня інтеграції елементів і технологічних процесів.

Початковий етап розробки топології полягає в виготовленні ескізних креслень, виконаних на міліметровому папері в масштабі 10:1 чи 20:1.

Обравши масштаб 10:1, розрахувала своє креслення на міліметровці.

Далі необхідно усунути недоліки цього варіанту, тобто креслить топологічне креслення з урахуванням всіх стандартних умов, вказую матеріали виготовлення, оформляю таблиці та пишу технічні вимоги. В якості резистивного шару обирає кермет, оскільки схема не потребує високої точності і не розсіює багато тепла; в якості провідників та приєднань конденсаторів обираю мідь, а контактні площадки припайки ніжок мікросхеми з алюмінію

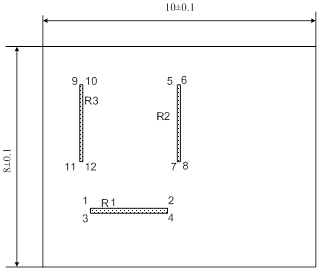

2.5 Топологічне креслення окремих шарів

При переробці першого варіанту топології звичайно не вдається отримати досконалу конфігурацію шарів, тому робота над наступними варіантами топології зводиться до усунення недоліків першого варіанту для того, щоб креслення відповідало всім конструктивно-технологічним вимогам і обмеженням.

Після того, як остаточно вибраний варіант топології, приступають до виконання креслень шарів мікросхеми по елементам (резистори, провідники, контактні площадки і т.д.).Наприклад, для резистивного шару виконується таблиця координат, в якій приводяться координати всіх вершин кожного із резисторів. Відповідно цим координатам виконуються всі плівкові резистори. Окрім резистивного шару більше нічого не зображується. Також приведені розміри для довідок.

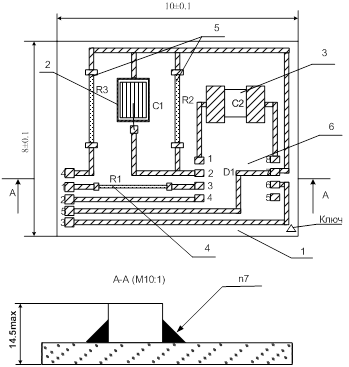

2.6 Розробка складального креслення плати ГІМС

Розробку складального креслення починаємо з розмітки, місць для виводів основного надпису і специфікації. Складальне креслення поєднує в собі плату, плівкові елементи, навісні елементи, які клеяться та припаюються з дротяними виводами, тобто це плата на якій вже повністю установлені, припаяні та приклеєні всі елементи схеми. Подальша робота включає елементи конструювання: розміщуємо плівкові елементи у відповідності з завданням, надаючи їм належні форми та розміри, а також - навісні елементи. Навісні елементи підбирає по типу, вказаному в таблиці завдання. Плівкові елементи - резистори.

При встановленні резисторів і діодних матриць дотримуємось послідовності розташування виводів. Ці елементи можна повертати в одній площині на 90, 180 і 270°.

Провідники і контактні площадки умовно виділені штриховкою під 45° не позначуючи розріз. Виводи мікросхеми необхідно пронумерувати і написати позиційні позначення елементів. В якості матеріалу моїх елементів, таких як конденсатор обираємо мідь, у якості резестивного шару - ніхром. Після цього креслення оформлюємо специфікацію.

Специфікацію (перелік складових частин виробу) виконуємо на окремих аркушах з особливими формами основних надписів для першого і слідуючих аркушів.

Специфікація складається з наступних складових:

Документація-записують найменування і позначення складального креслення специфіруємого виробу та інших схем. В специфікацію складальної одиниці записують її найменування та позначення.

Складальні одиниці записують позначення і найменування вхідних складальних одиниць, послідовності зростання позначень.

Деталі-записують позначення і найменування деталей, які не ввійшли в складальні одиниці, в порядку зростання їх позначень.

Стандартні вироби-записують вироби, які застосовуються по ГОСТам, в алфавітному порядку.

Матеріали-записують спочатку дроти, потім стрічку поліхлорвінілову, і трубку поліхлорвінілову, також по зростанню розмірів і інших параметрів із вказанням кількості.

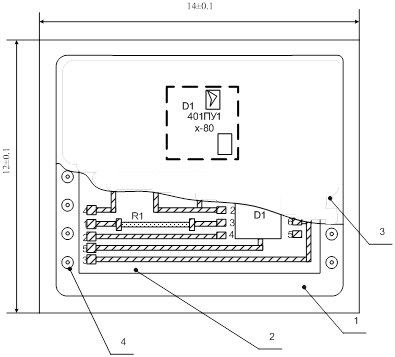

2.7 Розробка складального креслення ГІМС в корпусі

Відповідно принциповій схемі, на плату ГІМС встановлюють навісні елементи і компоненти і оформляють такі плати як складальні креслення. В даному випадку мікросхему 740 УД5-1 приклеюють до плати, а її виводи приварюють. Навісний конденсатор К10-17-1В припаюється до плати мікропаяльником. На складальному кресленні зображені всі шари та їх технічні дані, а також технічні вимоги до виконання креслення, тобто зображення плати після всіх складальних операцій, способи встановлення компонентів на плату, технологічні вимоги, а також додається специфікація.

Корпус необхідний для захисту мікросхеми від механічних, кліматичних та інших впливів. Необхідні вимоги, яким повинна задовольняти конструкція корпусу, зводяться до наступних:

-захист мікросхем від впливу зовнішнього середовища і механічних впливів;

- забезпечення надійного електричного з’єднання контактних площадок мікросхем з виводами корпусу;

- забезпечення надійного кріплення корпусу при монтажі в апаратурі;

-забезпечення надійності монтажу.

Крім того, конструкція повинна мати високу надійність, мати корозійну і радіаційну стійкість, а також бути простою та економічною у виготовлені.

Висновки

В курсовому проекті виконано розробку

конструкторської документації гібридної інтегральної мікросхеми. При цьому

розраховано геометричні розміри елементів, площу плати і вибраний її

типорозмір. Для даного варіанту площа становить 51,381 мм2. отже

розмір плати було взято 15,3![]() 12,9 мм.

12,9 мм.

Також розроблено топологію для якої був обраний варіант з найменшою площею, та мінімальною кількістю перетинів і рівномірним розміщенням елементів по площі плати.

Виконано креслення резистивного шару, під час виконання якого було визначено координати чотирьох кутів кожного з резисторів, розробку складального креслення плати гібридної інтегральної мікросхеми і розробку.

Також для завершення розробки гібридної інтегральної мікросхеми було виконано специфікацію до складального креслення.

Поєднання плівкових та навісних елементів на одній основі явно спрощує розробку мікросхеми, і зменшує її площу. Отже розміщувати елементи на платі необхідно з мінімальними затратами площі цієї плати, тоді це призведе до покращення плати шляхом мінімізації, а складність її збирання не впливає на швидкодію.

ГІМС відрізняються малою площею та високою надійністю, потребують небагато енергії, тому вони набувають широкого використання у сучасних електронних пристроях.

Список використаних джерел

1. Александров, Є.Г. Кузьмина Електротехнічні креслення і схеми – М.: Енерговидавництво. – 1990. – 288с.

2. А.М. Хаскін Креслення – К.: Вища школа. – 1976. – 436с.

3. В.Н. Дулин Электрические приборы – М.: Энэргоиздательство, 1989. – 303с.

4. Методичні вказівки до виконання курсової роботи з курсу „Нарисна геометрія та машинна графіка” на тему: „Розробка та оформлення конструкторської документації ГІМС”. Частина 1. Уклад. Кормановський С.І., Колесницький О.К., Вітюк О.П., Пащенко В.Н.- Вінниця, ВДТУ, 1997. – 32с.

5. Р.М. Терещук, К.М. Терещук, С.А. Сєдов Справочник радиолюбителя – К.: Наукова думка, 1981. – 671с.

6. Г.Д. Дорощенков, О.К. Колесницький, С.Є. Тужанський Радіо компоненти та мікроелектронна технологія: навчальний посібник – В.:ВНТУ, 2006. – 147с.

Додаток А

Таблиця 1

| № |

Умовне позначення |

Найменування шарів |

Позначення матеріалу |

Електричні характеристики |

Метод одержання |

Номер листа Креслення і таблиці |

| 1 |

|

Резистори | Кермет |

R0=1000 Ом/м |

Напилення в вакумі | |

| 2 |

|

Контактні площадки | Алюміній А99 ГОСТ 11069-74 |

R0=0.08Oм |

||

| 3 |

|

Контактні площадки і провідники | Мідь вакуумна МВТУ 11Яе0.021.040-Т2 |

R0=0.06Oм |

||

| 4 |

|

Контактні площадки і з’єднувальні провідники | Боросилікатне скло Е70.035.015ТУ |

С0=10000пФ/Ом2 |

||

| 5 |

|

Верхній слой плівкового конденсатора | Матеріал для напилення обкладок Алюміній А99(ГОСТ 11069-64) |

С0=2 1О4 пФ/см2 |

||

| 6 |

|

Діалектрик |

Боросилікатне скло E70.035.015ТУ |

С0=10000пФ/Ом2 |

Додаток Б

Таблиця 2

| № вимірів | Поз. Означення | Точки вимірів | Провіряючий номінальний допуск | |

| 1 | R1 | 1-3 | 6 кОм±10% | |

| 2 | R2 | 4-2 | 26 кОм±10% | |

| 3 | R3 | 4-2 | 26 кОм±10% | |

| 4 | С1 | 4-2 | 220пФ±15% | |

| 5 | C2 | 1-8 | 0.01мкФ±10% | |

1. * Розміри для довідок.

2. Поверхня А полірована.

3. Конфігурацію плівчастих елементів виконувати по координатам, вказаним в Табл.. 3-7.

4. Елементи шарів виконуються через маску по ОСТ4 ГО.054.238.

5. Опір R і ємність С повинні відповідати значенням Табл..2.

Додаток В

Таблиця 3

| Номери точок | Координати | |

| x | Y | |

| 1 | 16 | 23 |

| 2 | 51 | 23 |

| 3 | 16 | 17 |

| 4 | 51 | 17 |

| 5 | 57 | 63 |

| 6 | 62 | 63 |

| 7 | 57 | 31 |

| 8 | 62 | 31 |

| 9 | 13 | 63 |

| 10 | 18 | 63 |

| 11 | 18 | 31 |

| 12 | 41 | 31 |

1. * Розміри для довідок

Додаток Г

1. *Розміри для довідок

2. Установку без корпусних компонентів виконувати по ОСТу ТО.010,220

3. Компоненти поз. 2,6 клеїти до плати поз.1 клеєм ВК-9ОСТ ГО.029.204 по ОСТу.054.21С.

4. Виводи елементів поз. 2 варити на установці „Контакт-3А” по ОСТу ГО.054.242.

5. Довжина вільних кінців дротяних виводів компонентів в місцях приєднання до контактних доріжок 0,5 мм max в границях контактних доріжок.

6. Позначення без корпусних елементів і контактних доріжок показано умовно.

Додаток Д

1. *Розміри для довідок

2. Плату поз.2 клеїти до деталі поз.1 клеєм ВК-9 по ОСТ4.ГОО54.210. Орієтировку провести по плівкових елементах.

3. Герметизацію схем проводити методом лазерного зварювання по ОСТ4.ГО.054.241

4. Контроль герметичності схем проводити вакумно рідинним методом по ОСТ4.ГО054.241

5. Маркірувати надписи емаллю ЕП-578,чорна ТУ6101559714 шрифтом 1 по НО.010.007. Нанести клеймо ВТК.

6. Після нанесення маркіровки поз.3 покрити лаком УР-231 ТУ6-10-В53-76Ж по ОСТ4.ГО.054.205

7. Загальні вимоги по ОСТ4.ГО.005.21

АНОТАЦІЯ

В даному курсовому проекті розроблено конструкторську документацію гібридної мікросхеми з заданими параметрами, а також розраховано її оптимальні розміри за відповідними правилами. Виконано креслення резистивного шару, розробка складального креслення плати гібридної інтегральної схеми і специфікація до складального креслення.

АННОТАЦИЯ

В данном курсовом проекте разработана конструкторская документация гибридной микросхемы с заданными параметрами, а также рассчитано ее оптимальные размеры по соответствующим правилам. Выполнено чертеж резистивного шара, разработка сборочного чертежа платы гибридной интегральной схемы и спецификация к сборочному чертежу.

ABSTRACT

In the given academic year project the design documentation of a hybrid microcircuit with the set parametres is developed, and also calculation of its optimum sizes by respective rules is executed. It is executed plotting of a resistive sphere, working out of assembly plotting of a payment of a hybrid integrated microcircuit and the specification to assembly plotting.