Контрольная работа: Принцип побудови лінійних кодерів і декодерів

Принцип побудови лінійних кодерів і декодерів

Принцип побудови лінійних кодерів і декодерів

За принципом дії розрізнюють такі методи перетворення аналогових величин у цифрові:

– метод послідовного лічення (часово-імпульсний метод);

– метод безпосереднього лічення (матричний метод);

– метод зваження (порозрядного врівноваження).

Метод

послідовного лічення заснований на врівноваженні вхідної величини, що

перетворюється, сумою квантів (еталонів) мінімальної ваги ![]() . Кількість цих

еталонів, що використовуються для врівноваження, підраховується, момент

урівноваження фіксується і видається результат.

. Кількість цих

еталонів, що використовуються для врівноваження, підраховується, момент

урівноваження фіксується і видається результат.

Метод

безпосереднього лічення передбачає наявність ![]() еталонів, сусідні яких за вагою

відрізняються на 1 квант. Порівняння вхідної величини з кожним еталоном

відбувається одночасно за допомогою

еталонів, сусідні яких за вагою

відрізняються на 1 квант. Порівняння вхідної величини з кожним еталоном

відбувається одночасно за допомогою ![]() схем порівняння.

схем порівняння.

Метод

порозрядного зваження передбачає використання деякої кількості (суми) еталонів,

вага яких пропорційна за двійковою системою лічення числу ![]() .

.

Врівноваження вхідної величини починається еталоном максимальної ваги. У залежності від результату порівняння визначається значення („0” або „1”) старшого розряду коду.

Якщо величина

вхідного сигналу менша за еталон (![]() ), то значення старшого розряду

дорівнює „0”, і далі робиться спроба врівноважити вхідний сигнал еталоном

наступної ваги.

), то значення старшого розряду

дорівнює „0”, і далі робиться спроба врівноважити вхідний сигнал еталоном

наступної ваги.

Якщо ж ![]() , то на позиції

старшого розряду кодової комбінації фіксується „1” і далі здійснюється

врівноваження різниці між величиною вхідного сигналу еталоном

, то на позиції

старшого розряду кодової комбінації фіксується „1” і далі здійснюється

врівноваження різниці між величиною вхідного сигналу еталоном ![]() .

.

Отримана різниця порівнюється (врівноважується) з наступним за вагою еталоном. Процес продовжується до врівноваження останньої із різниць мінімальним за вагою квантом, що дозволяє визначити значення („1” або „0”) молодшого розряду кодової комбінації, яка формується.

Можливим є дещо інший варіант реалізації методу, що розглядається.

Порівняння

величини, що перетворюється за першим варіантом, починається з еталона максимальної

ваги. За результатами порівняння формується значення („1” або „0”) старшого

розряду кодової комбінації. А надалі виконується порівняння не різниці з

черговим еталоном, а усієї величини вхідного сигналу з сумою еталонів, тобто ![]() з

з

,

,

де ![]() – коефіцієнти, що

визначають наявність „1” або „0” у відповідному розряді кодової комбінації.

– коефіцієнти, що

визначають наявність „1” або „0” у відповідному розряді кодової комбінації.

Відповідно до розглянутих методів аналого-цифрового перетворення кодери розподіляються на кодери послідовного лічення, матричні кодери та кодери порозрядного зважування.

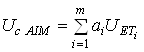

Принцип дії кодера послідовного лічення, структурна схема якого і часова діаграма його роботи наведена на рис. 1, досить простий.

Дискрети АІМ

сигналу (рис. 1,б) перетворюються в імпульси з широтно-імпульсною модуляцією

(рис. 1,в), тобто здійснюється перетворення АІМ у ШІМ. У такому випадку ширина кожного

з імпульсів ![]() пропорційна

амплітуді відповідної дискрети АІМ сигналу.

пропорційна

амплітуді відповідної дискрети АІМ сигналу.

Імпульси з ШІМ

подаються на один вхід схеми збігу (рис. 1,а), а на другий – послідовність

коротких тактових імпульсів (рис. 1,г) з більш високою частотою надходження,

внаслідок чого на виході схеми збігу отримуємо пачки імпульсів (![]() , рис 1,д). Кількість

імпульсів у кожній з пачок

, рис 1,д). Кількість

імпульсів у кожній з пачок ![]() пропорційна ширині імпульсу,

отже, пропорційна амплітуді відповідних дискрет АІМ сигналу.

пропорційна ширині імпульсу,

отже, пропорційна амплітуді відповідних дискрет АІМ сигналу.

Після

підрахування кількості імпульсів у пачці на виході лічильника формується

m-розрядна кодова комбінація паралельного коду, зміст якої відображує у

двійковому коді величину дискрети АІМ сигналу, тобто здійснюється перетворення

АІМ сигналів в ІКМ сигнал (рис. 1,е). Перед надходженням чергової пачки

імпульсів лічильник скидається імпульсом ![]() (рис. 1,ж). Перетворення

паралельного коду у послідовний досить просто здійснюється за допомогою схем

збігу і регістра зсуву (рис. 1,а).

(рис. 1,ж). Перетворення

паралельного коду у послідовний досить просто здійснюється за допомогою схем

збігу і регістра зсуву (рис. 1,а).

Імпульси опитування відчиняють схеми збігу по одному з входів, на другому з них діють вихідні імпульси лічильника, зміст яких передається у чарунки регістра зсуву. Імпульсами зсуву зміст регістра видається у послідовному коді.

Переваги кодера

послідовного рахування – простота, а отже, надійність. До недоліків слід

віднести необхідність суттєвого збільшення тактової частоти, яка полягає в ![]() -канальній ЦСП

з m-розрядними канальними ІКМ сигналами значення

-канальній ЦСП

з m-розрядними канальними ІКМ сигналами значення

![]() .

.

Водночас під час використання кодера зваження

![]() ,

,

тобто суттєво

нижча. Наприклад, якщо ![]() ,

, ![]() ,

, ![]() кГц, то величина тактової частоти

дорівнює 65536 і 2048 кГц відповідно, тобто для реалізації кодера послідовного

лічення необхідна більш швидкодіюча елементна база.

кГц, то величина тактової частоти

дорівнює 65536 і 2048 кГц відповідно, тобто для реалізації кодера послідовного

лічення необхідна більш швидкодіюча елементна база.

аналоговий цифровий кодер декодер

Рисунок 1

Побудова кодера

безпосереднього зчитування (матричного кодера) основана на використанні

кодового поля, на якому відображені усі ![]() можливі кодові групи для заданої

розрядності коду (m). Реалізація матричного кодера можлива з використанням

спеціалізованої електронно-променевої трубки, або набору

можливі кодові групи для заданої

розрядності коду (m). Реалізація матричного кодера можлива з використанням

спеціалізованої електронно-променевої трубки, або набору ![]() компараторів.

компараторів.

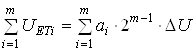

Схема матричного кодера на електронно-променевій трубці зображена на рис 2.

Рисунок 2

Пилоподібна напруга розгортає тонкий електронний промінь по горизонталі, а по вертикалі промінь переміщається АІМ сигналом, що кодується.

Кодування АІМ сигналу відповідного рівня виконується завдяки тому, що відхилений цим сигналом промінь „пробігає” по тому чи іншому рядку маски, попадає через отвори на колектор і відділяється на резисторі навантаження.

Наявність отворів відповідає кодовій таблиці, кожний рядок якої відображує рівень сигналу у двійковій системі лічення. Перевагою такого кодера є швидкодія, недоліком – необхідність використовувати для роботи високі напруги, невисока стабільність, висока вартість.

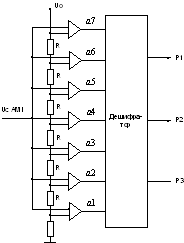

Схема кодера на компараторах для m=3 наведена на рис. 3.

|

Рисунок 3

Напруга ![]() є рівнем

обмеження, яка подається на подільник з

є рівнем

обмеження, яка подається на подільник з ![]() однакових резисторів, тому на

входах компараторів діє відповідна опорна напруга. Значення

однакових резисторів, тому на

входах компараторів діє відповідна опорна напруга. Значення ![]() відображують і-й рівень

сигналу (

відображують і-й рівень

сигналу (![]() )

причому різниця між

)

причому різниця між ![]() та

та ![]() дорівнює кроку квантування

дорівнює кроку квантування ![]() , значення

, значення ![]() і відповідне

значення розрядів сформованого паралельного коду Грея (P1,P2,P3) наведені в

табл. 1

і відповідне

значення розрядів сформованого паралельного коду Грея (P1,P2,P3) наведені в

табл. 1

Таблиця 1

| Рівні АІМ сигналу |

Значення коефіцієнтів |

Вихідний код Грея | ||||||||

|

|

|

|

|

|

|

|

Р1 | Р2 | Р3 | |

|

|

1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

|

|

0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

|

|

0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

|

|

0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

|

|

0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 0 |

|

|

0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 |

|

|

0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Досить легко визначити, що структура дешифратора визначається з використанням булевих функцій:

![]() ;

;

![]() ;

;

![]() .

.

У сучасних ЦСП використовують переважно кодери порозрядного зваження.

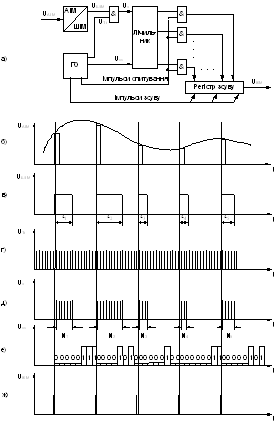

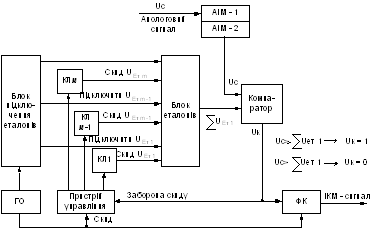

Структурна схема кодера порозрядного зваження наведена на рис. 4.

Аналоговий сигнал дискретизується і перетворюється в АІМ сигнал. На вхід компаратора (схеми порівняння) подається дискретний АІМ-сигнал, рівень якого за допомогою перетворювача АІМ-1 в АІМ-2 запам’ятовується на час кодування.

На другий вхід

компаратора подається сума еталонних сигналів з блоку еталонів. Еталонні

сигнали підключаються почергово, починаючи з максимального ![]() , управляючими сигналами з блоку

підключення еталонів.

, управляючими сигналами з блоку

підключення еталонів.

Якщо ![]() , то на виході компаратора

формується сигнал, що призводить у свою чергу формування „1” на виході

формувача коду (ФК). Підключений

, то на виході компаратора

формується сигнал, що призводить у свою чергу формування „1” на виході

формувача коду (ФК). Підключений ![]() не скидається, бо вихідний сигнал

компаратора „Заборона скиду” забороняє скид.

не скидається, бо вихідний сигнал

компаратора „Заборона скиду” забороняє скид.

На черговому

такті кодування підключений ![]() сумується з еталонним сигналом

сумується з еталонним сигналом ![]() , після чого

процес порівняння і формування значення чергового розряду кодової комбінації

повторюється аналогічно розглянутому.

, після чого

процес порівняння і формування значення чергового розряду кодової комбінації

повторюється аналогічно розглянутому.

Рисунок 4

Якщо ж ![]() , то на виході

компаратора сигнал відсутній, тому на виході ФК значення відповідного розряду

дорівнює „0”. Сигналом „Скид” з генераторного обладнання еталон

, то на виході

компаратора сигнал відсутній, тому на виході ФК значення відповідного розряду

дорівнює „0”. Сигналом „Скид” з генераторного обладнання еталон ![]() відключається.

відключається.

Таким чином, сутність роботи кодеру полягає у тому, що:

– підбір суми еталонних сигналів, що приблизно дорівнює рівню вхідного сигналу, виконується за m кроків;

– еталони

підключаються по черзі послідовно, починаючи із старшого ![]() ;

;

– на кожному і-му

такті підключається черговий і-й еталон, а компаратор здійснює порівняння

величини сигналу ![]() з сумою еталонів

з сумою еталонів  .

.

Якщо ![]() , то вихідний

сигнал компаратора

, то вихідний

сигнал компаратора ![]() , еталон

, еталон ![]() залишається підключеним, у

відповідному розряді кодової групи на виході ФК формується „1”. Якщо ж

залишається підключеним, у

відповідному розряді кодової групи на виході ФК формується „1”. Якщо ж ![]() , то вихідний

сигнал компаратора

, то вихідний

сигнал компаратора ![]() , еталон

, еталон ![]() відключається, на виході

формувача коду (ФК) у відповідному розряді кодової групи формується пауза

(„0”).

відключається, на виході

формувача коду (ФК) у відповідному розряді кодової групи формується пауза

(„0”).

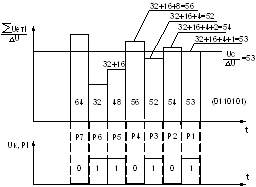

Розглянемо процес кодування на конкретному прикладі. Припустимо,

![]() , mі = 7

, mі = 7

У такому випадку

![]() ,

, ![]() , ...

, ... ![]()

На першому етапі

кодування підключається ![]() . Оскільки

. Оскільки

![]() ,

, ![]() ,

,

у результаті на

виході ФК старший розряд ![]() має значення „0”,

має значення „0”, ![]() скидається. На другому

такті підключається

скидається. На другому

такті підключається ![]() .

.

Оскільки

![]() ,

, ![]() ,

,

ФК формує у

черговому розряді кодової комбінації ![]() , скид

, скид ![]() заборонений. На третьому такті

підключається

заборонений. На третьому такті

підключається

![]() ,

,

він складається з

![]() , тому

сигнал порівнюється з сумою еталонів

, тому

сигнал порівнюється з сумою еталонів ![]() , результати порівняння

, результати порівняння

![]() .

.

За результатами

порівняння ![]() ,

розряд кодової комбінації

,

розряд кодової комбінації ![]() , еталонний сигнал

, еталонний сигнал ![]() залишається

підключеним. В результаті сформована кодова комбінація 0110101. Аналогічно

виконуються послідовні операції кодування. На рис.5 наведені часова діаграма

процесу кодування і структура кодової комбінації (Uk), що сформована на виході ФК.

залишається

підключеним. В результаті сформована кодова комбінація 0110101. Аналогічно

виконуються послідовні операції кодування. На рис.5 наведені часова діаграма

процесу кодування і структура кодової комбінації (Uk), що сформована на виході ФК.

Рисунок 5

Слід зазначити, що для кодування двополярних сигналів у складі кодера необхідно мати дві схеми формування еталонів для кодування позитивних та негативних відліків АІМ сигналу відповідно.

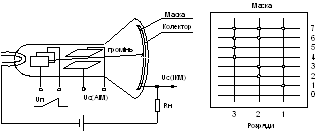

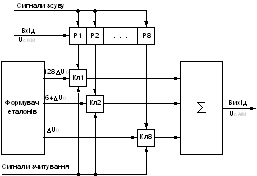

Функцією лінійних декодерів є перетворення кодових комбінацій цифрового (ІКМ) сигналу у послідовність дискрет АІМ сигналу. Найчастіше використовуються декодери зваження. Структурна схема 8-розрядного лінійного декодера порозрядного зваження наведена на рис. 1.17.

Рисунок 6

ІКМ сигнал, що підлягає декодуванню, порозрядно записується у чарунки регістра зсуву. Сигнали зсуву надходять з генераторного обладнання (ГО). Після заповнення регістра черговою 8-розрядною кодовою групою сигналами зчитування (із ГО) відмикаються ті ключі (Кл1, Кл2,...,Кл8), що відповідають розрядам, які мають значення 1. В результаті на суматор надходять відповідні еталонні сигнали і на виході суматора формуються дискрети АІМ сигналу відповідної амплітуди.