Реферат: ПТЦА - Прикладная теория цифровых автоматов

Методы анализа и синтеза комбинационных схем.

Техническим аналогом булевой функции в вычислительной технике является, так называемая, комбинационная схема, на вход которой поступают и с выхода снимаются электрические сигналы в виде одного из уровней напряжения, соответствующих значениям логического 0 и логической 1.

|

|

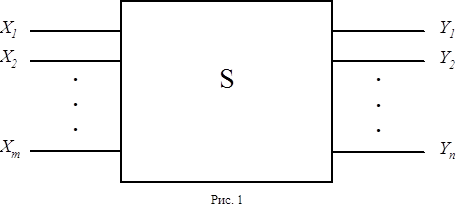

Для выяснения, что же такое

комбинационная схема, рассмотрим схему S, имеющую m входов и n

выходов (рис. 1). На её входы могут быть поданы наборы значений входных

переменных Xi {0,1}, ![]() , а на выходах формируются

выходные переменные YjÎ{0,1},

, а на выходах формируются

выходные переменные YjÎ{0,1}, ![]() .

.

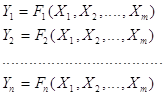

Схема S называется комбинационной, если каждую из n функций её выходов Y1,Y2, ..., Yn можно представить как булеву функцию входных переменных X1, X2, ..., Xm.

Комбинационная схема описывается с помощью системы уравнений (1), где Fi – булева функция.

|

Как следует из определения комбинационной схемы, значения выходных переменных Yj в произвольный момент времени однозначно определяются значениями входных переменных Xi.

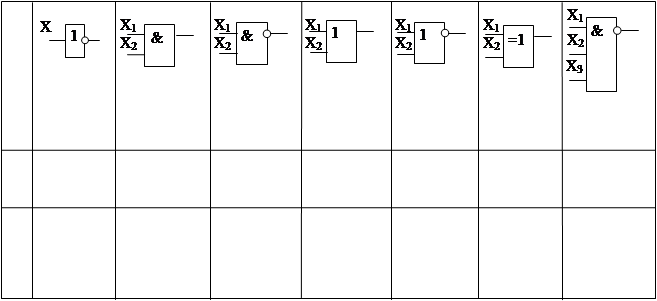

Структурно комбинационная схема может быть представлена как совокупность элементарных логических схем – логических элементов (ЛЭ). ЛЭ выполняют над входными переменными элементарные логические операции типа И-НЕ, И, ИЛИ, ИЛИ-НЕ и т.д. Число входов логического элемента соответствует числу аргументов воспроизводимой им булевой функции. Графическое изображение комбинационной схемы, при котором показаны связи между различными элементами, а сами элементы представлены условными обозначениями, называется функциональной схемой.

В ходе разработки комбинационных схем приходится решать задачи анализа и синтеза.

Задача анализа состоит в определении статических и динамических свойств комбинационной схемы. В статике определяются булевы функции, реализуемые комбинационной схемой по известной ей структуре. В динамике рассматривается способность надёжного функционирования схемы в переходных процессах при смене значений переменных на входах схемы, т.е. определяется наличие на выходах схемы возможных нежелательных импульсных сигналов, которые не следуют непосредственно из выражений для булевых функций, реализуемых схемой.

Задача синтеза заключается в построении из заданного набора логических элементов комбинационной схемы, реализующей заданную систему булевых функций.

Решение задачи синтеза не является однозначным, можно предложить различные варианты комбинационных схем, реализующих одну и ту же систему булевых функций, но отличающихся по тем или иным параметрам. Разработчик комбинационных схем из этого множества вариантов выбирает один, исходя из дополнительных критериев: минимального количества логических элементов, необходимых для реализации схемы, максимального быстродействия и т.д. Существуют различные методы синтеза комбинационных схем, среди которых наиболее разработан канонический метод.

1.1. Канонический метод синтеза комбинационных схем.

Как отмечалось выше, комбинационная схема (КС) может иметь несколько выходов. При каноническом методе предполагается, что каждая выходная функция реализуется своей схемой, совокупность которых и даёт требуемую КС. Поэтому синтез сложной КС с n выходами заменяется синтезом n схем с одним выходом.

Согласно каноническому методу синтез КС включает в себя ряд этапов.

1. Подлежащая реализации булева функция (или её отрицание) представляется в виде СДНФ.

2. С использованием методов минимизации определяется минимальная ДНФ (МДНФ) или минимальная КНФ (МКНФ). Из полученных двух минимальных форм выбирается более простая.

3. Булеву функцию в минимальной форме согласно п.2 представляют в заданном (или выбранном разработчиком) базисе .

4. По представлению функции в заданном базисе строят комбинационную схему.

Необходимо отметить, что подлежащая реализации булева функция F(X1,X2,...,Xm) может быть задана не на всех возможных наборах аргументов X1, X2, ..., Xm. На тех наборах, где функция неопределенна, её доопределяют так, чтобы в результате минимизации получить более простую МДНФ или МКНФ. При этом упростится и сама КС. Кроме того, довольно часто с целью получения ещё более простого представления функции МДНФ, полученная в п.2, представляется в так называемой скобочной форме, т.е. выносятся за скобки общие части импликант МДНФ.

Рассмотрим канонический метод синтеза на примере построения схемы полного одноразрядного двоичного сумматора.

Как известно из курса машинной арифметики, полный одноразрядный сумматор - это устройство, которое осуществляет сложение по mod 2 соответствующих разрядов (X1,X2) двоичных чисел с учётом переноса (Рm) в данный разряд из соседнего младшего разряда суммы. Сумматор вырабатывает цифру результата (S) в данном разряде и перенос (Рс) в соседний старший разряд суммы. Таблица истинности такого сумматора (т.е. представление булевой функции, которую он реализует, в виде СДНФ) представлена ниже.

|

X1 |

0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | ||

|

X2 |

0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | ||

|

|

0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | ||

| S | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | ||

|

Pc |

0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 |

|

|

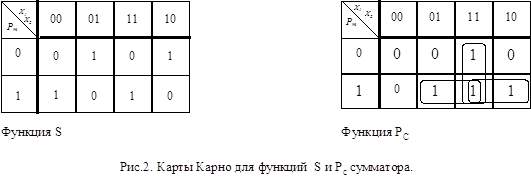

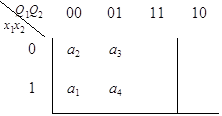

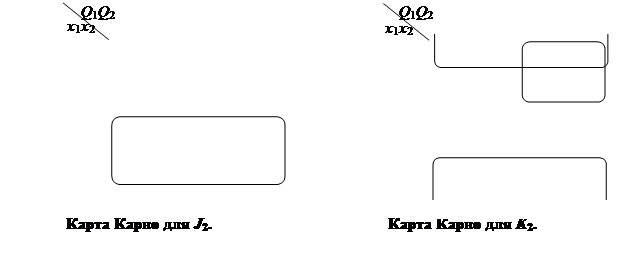

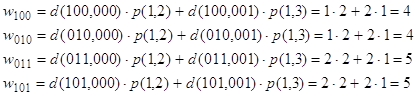

Необходимо получить булевы функции S=F1(X1,X2,Рm) и Рс=F2(X1,X2,Рm). Карты Карно для этих функций приведены ниже (рис.2).

Как следует из приведённых карт, МДНФ соответствующих функций имеет вид:

|

Pc= X1 X2+X1 Pm+X2 Pm

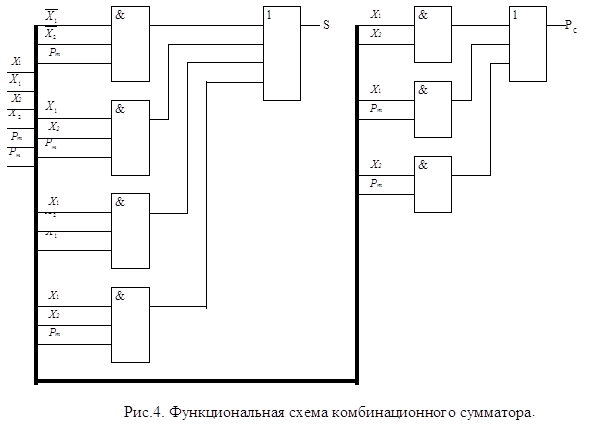

Полученная система булевых функций представлена в базисе И, ИЛИ, НЕ. Соответствующая ей КС приведена на рисунке 4.

Полученную комбинационную схему можно упростить, вынеся за скобки общие части в выражениях для S и Рc, однако существенного результата это не даст (желательно самостоятельно в этом убедиться).

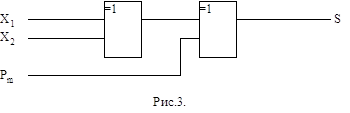

Значительно упростить схему можно, если воспользоваться другим базисом, например логическим элементом "ИСКЛЮЧАЮЩЕЕ ИЛИ". В этом случае выражение для S можно записать S = (X1+X2+ Рm)mod2= X1Å X2Å Рm. Тогда схема для S будет иметь вид (рис.3).

|

|

Иногда для синтеза КС с несколькими выходами может использоваться следующий приём. Будем считать, что при синтезе схемы сумматора функция S является функцией четырёх переменных: S=f(X1,X2,Рm,Рс). Таблица истинности для этого случая принимает вид изображенный в таблице 2.

|

|

|

X1 |

0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

|

X2 |

0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

|

Pm |

0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

|

Pc |

0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| S | 0 | X | 1 | X | 1 | X | X | 0 | 1 | X | X | 0 | X | 0 | X | 1 |

|

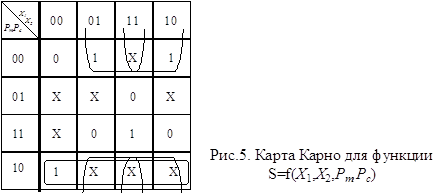

Неопределённые значения для S соответствуют наборам, которые никогда не могут быть в реальной схеме. Карта Карно для функции S=f(X1,X2,Pm,Pc) представлена на рис.5.

|

|

В результате минимизации, получается :

|

Сравнивая выражения (2) и (3), отмечаем, что функция S=f(X1,X2,Pm,Pc) проще, чем функция S=f1(X1,X2,Pm). Схему, соответствующую (3), предлагается построить самостоятельно.

Т.о. задача синтеза имеет обычно несколько решений. Для сравнения различных вариантов комбинационных схем используют их основные характеристики: сложность и быстродействие.

1.2. Характеристики комбинационных схем.

Сложность схемы оценивается количеством оборудования, составляющего схему. При разработке схем на основе конкретной элементной базы количество оборудования обычно измеряется числом корпусов (модулей) интегральных микросхем, используемых в схеме. В теоретических разработках ориентируются на произвольную элементную базу и поэтому для оценки затрат оборудования используется оценка сложности схем по Квайну.

Сложность (цена) по Квайну определяется суммарным числом входов логических элементов в составе схемы.

При такой оценке единица сложности – один вход логического элемента. Цена инверсного входа обычно принимается равной двум. Такой подход к оценке сложности оправдан по следующим причинам:

- сложность схемы легко вычисляется по булевым функциям, на основе которых строится схема: для ДНФ сложность схемы равна сумме количества букв,(букве со знаком отрицания соответствует цена 2), и количества знаков дизъюнкции, увеличенного на 1 для каждого дизъюнктивного выражения.

- все классические методы минимизации булевых функций обеспечивают минимальность схемы именно в смысле цены по Квайну.

Практика показывает, что схема с минимальной ценой по Квайну обычно реализуется наименьшим числом конструктивных элементов – корпусов интегральных микросхем.

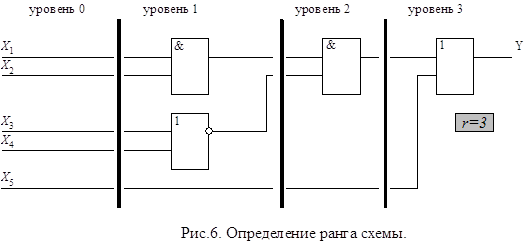

Быстродействие комбинационной схемы оценивается максимальной задержкой сигнала при прохождении его от входа схемы к выходу, т.е. определяется промежутком времени от момента поступления входных сигналов до момента установления соответствующих значений выходных. Задержка сигнала кратна числу элементов, через которые проходит сигнал от входа к выходу схемы. Поэтому быстродействие схемы характеризуется значением rt, где t - задержка сигнала на одном элементе. Значение r определяется количеством уровней комбинационной схемы, которое рассчитывается следующим образом. Входам КС приписывается уровень нулевой. Логические элементы, связанные только со входами схемы относятся к уровню ПЕРВОМУ. Элемент относится к уровню k, если он связан по входам с элементами уровней k-1, k-2, и т.д. Максимальный уровень элементов r определяет количество уровней КС, называемое рангом схемы. Пример определения ранга r схемы приведён на рисунке 6.

|

|

Как известно, любая булева функция может быть представлена в ДНФ, которой соответствует двухуровневая комбинационная схема. Следовательно, быстродействие любой КС в принципе можно довести до 2t.

Минимизация булевой функции с целью уменьшения сложности схем обычно приводит к необходимости представления функций в скобочной форме, которой соответствуют схемы с r>2. Т.е., уменьшение затрат оборудования в общем случае приводит к снижению быстродействия схем.

1.3. Системы (серии) логических элементов и их

основные характеристики.

При построении КС устройств вычислительной техники используются различные логические элементы, которые должны согласоваться по входным и выходным сигналам, напряжению питания и т.д. Для этой цели логические элементы объединяют в серии.

Серией (системой, комплексом) логических элементов ЭВМ называется предназначенный для построения цифровых устройств функционально полный набор логических элементов, объединяемый общими электрическими, конструктивными и технологическими параметрами, использующий одинаковый способ представления информации, одинаковый тип межэлементных связей. Система элементов чаще всего избыточна по своему функциональному составу, что позволяет строить схемы более экономичные по количеству использованных элементов.

В состав серии входят элементы для выполнения логических операций, запоминающие элементы, элементы, реализующие функции узлов ЭВМ, а также специальные элементы для усиления, восстановления и формирования сигналов стандартной формы.

Конструктивно логические элементы представляют собой микроминиатюризованные интегральные электронные схемы (микросхемы), сформированные в кристалле кремния с помощью специальных технологических процессов.

В большинстве современных серий элементов имеются микросхемы малой степени интеграции (ИС до 100 элементов на кристалл), средней степени (СИС – до 1000 элементов на кристалл), большой степени интеграции (БИС – до 10000 элементов на кристалл) и сверхбольшой степени интеграции (СБИС – более 10000 элементов на кристалл). Логические элементы в виде ИС реализуют совокупность простых логических операций: И, ИЛИ, И-ИЛИ, И-НЕ, ИЛИ-НЕ и т.д. Логические элементы на СИС и БИС реализуют узлы ЭВМ, на СБИС – микроЭВМ.

Основными параметрами серии логических элементов являются:

- питающие напряжения и сигналы для представления логического 0 и логической 1;

- коэффициенты объединения по входу;

- нагрузочная способность (коэффициент разветвления по выходу);

- помехоустойчивость;

- рассеиваемая мощность;

- быстродействие.

Серия элементов характеризуется количеством используемых питающих напряжений и их номинальными значениями. Обычно логическому 0 соответствует низкий уровень напряжения, а логической 1 – высокий. Для наиболее часто используемых серий напряжение питания составляет +5В, уровень логической единицы 2,4-5В, уровень логического 0 – 0-0,4В.

Коэффициент объединения по входу (Коб) определяет максимально возможное число входов логического элемента, иными словами, функцию скольких переменных может реализовать этот элемент. Обычно Коб принимает значение от 2 до 4, реже Коб=8. Увеличение числа входов связано с усложнением схемы элементов и приводит к ухудшению других параметров – помехоустойчивости, быстродействия и т.д.

Коэффициент разветвления по выходу (Краз) показывает на сколько логических входов может быть одновременно нагружен выход данного логического элемента. Обычно Краз для наиболее часто используемых серий равен 10. Иногда вместо Краз задается предельно допустимое значение выходного тока логического элемента в состоянии 0 или 1.

Помехоустойчивость – это способность элемента правильно функционировать при наличии помех. Она определяется максимально допустимым напряжением помехи, при котором не происходит сбоя в его работе. Обычно это напряжение порядка 0,6-0,9 В.

Быстродействие логических элементов является одним из важнейших параметров и характеризуется временем задержки распространения сигнала. Этот параметр существенно зависит от технологии изготовления микросхем и лежит в диапазоне от единиц до сотен наносекунд.

Наиболее часто употребляемые типы интегральных микросхем – это потенциальные элементы транзисторно-транзисторной логики (ТТЛ) - серии К155, К555, К531, К1533 и т.д., транзисторной логики с эмиттерными связями (ЭСТЛ) – это серии К500,К1500, элементы на КМОП транзисторах - серии К176, К561,К564 и т.д.

При синтезе КС на реальных логических элементах необходимо обязательно учитывать ограничения на Коб и Краз.

|

|

1.4. СИНТЕЗ КС С УЧЕТОМ ОГРАНИЧЕНИЙ НА ![]() .

.

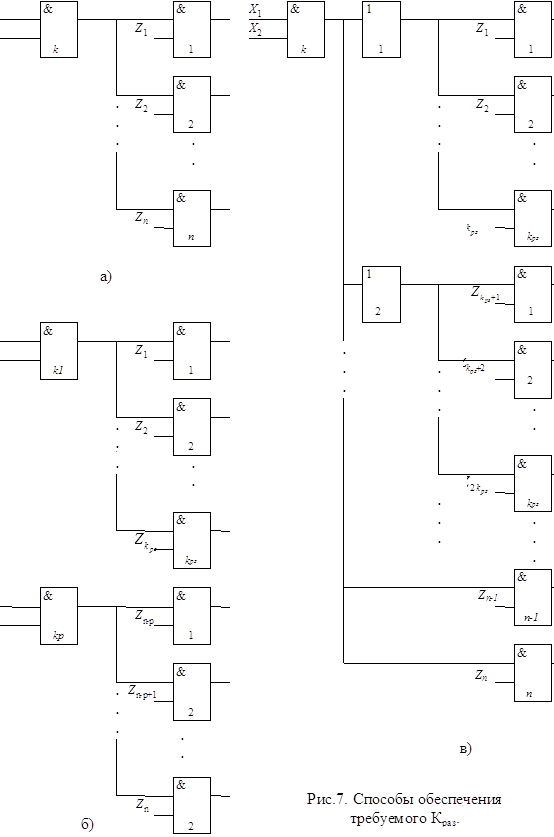

При

построении КС может оказаться, что выход k - го

логического элемента нагружен ![]() входов других ЛЭ (рис.7а). Это означает, что k -

тый логический элемент перегружен и необходимо принять меры,

устраняющие указанное явление. Существуют два способа обеспечения заданного

входов других ЛЭ (рис.7а). Это означает, что k -

тый логический элемент перегружен и необходимо принять меры,

устраняющие указанное явление. Существуют два способа обеспечения заданного![]() :

:

· использование дополнительных развязывающих усилителей;

· дублирование перегруженного элемента.

Схема

с использованием дополнительных развязывающих усилителей представлена на

рис.7.б. Количество p дополнительных усилителей, необходимых для обеспечения

заданного ![]() , определяется по формуле:

, определяется по формуле:

![]()

Недостаток рассматриваемого способа в том, что в цепь распространения сигнала вносится дополнительная задержка, что не всегда допустимо.

Схема с использованием дублирования перегружаемого элемента представлена на рис.7.в. Количество p дополнительных элементов, выполняющих ту же функцию, что и К-тый элемент, определяется по формуле:

![]()

При таком способе обеспечения ![]() дополнительная задержка не

вносится, но увеличивается нагрузка на элементы, формирующие сигналы

дополнительная задержка не

вносится, но увеличивается нагрузка на элементы, формирующие сигналы ![]() и

и ![]() , что может привести к

перегрузке этих элементов и введению дополнительных элементов для обеспечения

заданного Краз.

, что может привести к

перегрузке этих элементов и введению дополнительных элементов для обеспечения

заданного Краз.

1.5. СИНТЕЗ КС С УЧЕТОМ ОГРАНИЧЕНИЯ НА ![]() .

.

Представлению

функции в виде ДНФ соответствует двухуровневая КС (если считать,

что на ее вход могут поступать как прямые так и инверсные входные сигналы),

на первом уровне которой элементы И , а их выходы объединяются на втором

уровне элементом ИЛИ . Такое построение КС обеспечивает ее

максимальное быстродействие, так как ранг схемы минимален. Однако, не

всегда возможно на первом уровне и, особенно, на втором выбрать логические

элементы с требуемым![]() , т.к. может оказаться, что ЛЭ с таким

, т.к. может оказаться, что ЛЭ с таким ![]() не

выпускаются промышленностью. В этом случае необходимо с помощью нескольких

элементов с меньшим

не

выпускаются промышленностью. В этом случае необходимо с помощью нескольких

элементов с меньшим ![]() получить эквивалент с большим

получить эквивалент с большим ![]() либо,

что предпочтительней, преобразовать БФ, перейдя от ДНФ к скобочной форме.

Этот переход сопровождается уменьшением

либо,

что предпочтительней, преобразовать БФ, перейдя от ДНФ к скобочной форме.

Этот переход сопровождается уменьшением ![]() логических элементов, требуемого для построения

схемы. Осуществить такой переход можно с помощью факторного алгоритма,

суть которого рассмотрим на примере.

логических элементов, требуемого для построения

схемы. Осуществить такой переход можно с помощью факторного алгоритма,

суть которого рассмотрим на примере.

Пусть задана некоторая булева функция в виде

![]()

Для реализации этой функции по приведенному выражению необходимо использовать 3 логических элемента 4И, один логический элемент 5И, один логический элемент 4ИЛИ.

С помощью факторного алгоритма получим скобочную форму для заданной функции. Для этого обозначим все конъюнкции буквами:

![]()

![]()

![]()

и будем рассматривать их как некоторые множества. Находим попарные пересечения множеств:

![]() ,

,

![]() ,

, ![]() ,

, ![]() ,

, ![]() ,

, ![]() .

.

Полученные

пересечения показывают общие части отдельных конъюнкций. Выбираем

пересечение, которое имеет наибольшую длину (если такое отсутствует, то

выбирают то, которое чаще всего встречается). В данном случае это ![]() .

Поэтому из конъюнкций А и В выносим общую часть

.

Поэтому из конъюнкций А и В выносим общую часть![]() .

Тогда имеем:

.

Тогда имеем:

![]() .

.

Обозначим F = ![]() и находим пересечения:

и находим пересечения:

![]() ,

, ![]() ,

, ![]() .

.

Следовательно, для исходной функции имеем:

![]() .

.

Обозначим ![]() ,

,

Пересечение![]() .

Следовательно, окончательно имеем:

.

Следовательно, окончательно имеем:

![]()

|

|

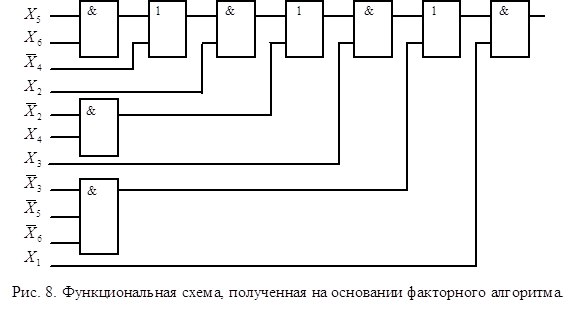

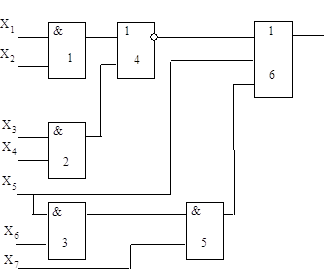

Для реализации функции по последнему выражению необходимо 5 элементов 2И, 1 элемент 3И, 3 элемента 2ИЛИ ( рис.8 ).

Как видно из полученной схемы для ее

реализации необходимы элементы с ![]() = 2 или 3 (в отличие от исходной с

= 2 или 3 (в отличие от исходной с ![]() = 4 или 5).

Однако ранг схемы увеличился до 7, что приводит к увеличению задержки

срабатывания схемы.

= 4 или 5).

Однако ранг схемы увеличился до 7, что приводит к увеличению задержки

срабатывания схемы.

1.6. Анализ комбинационных схем.

Задачи анализа КС возникают при необходимости проверить правильность синтеза (на этапе проектирования) или определить БФ, реализуемую КС (при анализе или ремонте схем). Все существующие методы анализа делятся на прямые и косвенные.

В результате анализа КС прямым методом получается множество наборов входных переменных, обеспечивающих заданное значение на выходе, что позволяет записать в алгебраическом виде БФ, реализуемую схемой. К прямым методам относится метод p- алгоритма.

Применение косвенных методов дает возможность определить реакцию схемы на заданный набор входных переменных в статике или проанализировать переходный процесс смены одного входного набора на другой. Примерами косвенных методов анализа, являются методы синхронного и асинхронного моделирования.

Все упомянутые методы анализа являются машинoориентированными, что позволяет выполнить анализ схемы на ЭВМ.

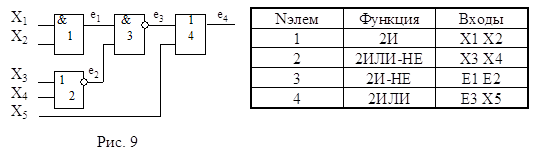

Для всех методов анализа необходимо описать схему в виде схемного списка, в который включается в общем случае следующие данные: номер ЛЭ в схеме; логическая функция, реализуемая ЛЭ; входные переменные для данного ЛЭ. Например, схема представленная на рис.9, может быть описана следующим списком:

|

|

1.7. Анализ комбинационных схем методом p-алгоритма.

При данном методе, как упоминалось

выше, ищутся наборы входных переменных, обеспечивающих заданное значение на

выходе КС. Наборы, обеспечивающие на выходе КС логическую 1, образуют так

называемое единичное покрытие ![]() . Аналогично, входные наборы,

обеспечивающие на выходе КС логический 0, образуют нулевое покрытие

. Аналогично, входные наборы,

обеспечивающие на выходе КС логический 0, образуют нулевое покрытие

![]() . Рассмотрим

покрытия

. Рассмотрим

покрытия![]() и

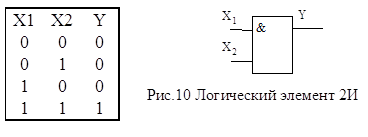

и ![]() для простейшего логического элемента

2И, выполняющего функцию Y=X1X2. Таблица

истинности для этой функции:

для простейшего логического элемента

2И, выполняющего функцию Y=X1X2. Таблица

истинности для этой функции:

Табл.3 Таблица истинности функции Y=X1X2

|

|

Как видно из приведенной таблицы только при

единственном наборе X1=1 и X2=1 на выходе ЛЭ будет 1,

т.е. единичное покрытие включает только один набор ![]() ={1

1}. На выходе ЛЭ будет 0 при трех наборах, образующих нулевое покрытие:

={1

1}. На выходе ЛЭ будет 0 при трех наборах, образующих нулевое покрытие:

Это покрытие можно упростить, заметив, что первый набор склеивается со вторым и третьим, т.е.

![]()

Т.о.

для ЛЭ 2И можно сказать, что 1 на его выходе будет только при обеих единицах

на входах, а для обеспечения 0 на выходе достаточно подать хотя бы на один

вход 0. Рассуждая аналогично, получим таблицу покрытий ![]() и

и![]() для основных ЛЭ, представленных ниже в

табл. 4.

для основных ЛЭ, представленных ниже в

табл. 4.

Таблица 4.

ЛЭ Y Y Y Y Y Y Y

НЕ 2И 2И – НЕ 2ИЛИ 2ИЛИ–НЕ ИСК. ИЛИ 3И – НЕ

X X1 X2 X1 X2 X1 X2 X1 X2 X1 X2 X1 X2 X3

![]() 1 0 X 1 1

0 0 1 X 0 0 1 1

1

1 0 X 1 1

0 0 1 X 0 0 1 1

1

X 0 X 1 1 1

![]() 0 1

1 0 X 1 X 0

0 0 1 0 X X

0 1

1 0 X 1 X 0

0 0 1 0 X X

X 0 X 1 1 0 X 0 X

X X 0

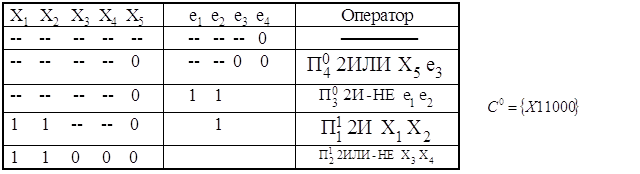

При анализе схемы методом p - алгоритма, задавшись определенным значением на выходе, заменяют его соответствующим покрытием элемента, формирующего выходной сигнал. В результате этого определяется, какие должны быть сигналы на выходах элементов, подключенных к выходному ЛЭ. В свою очередь, сигналы на выходах этих элементов можно заменить соответствующими покрытиями, т.е. определить значения выходных сигналов для других ЛЭ и т.д. Этот процесс продолжается до тех пор, пока не получатся покрытия, состоящие только из входных переменных, называемых опорными. Совокупность таких покрытий и дает соответствующее покрытие схемы.

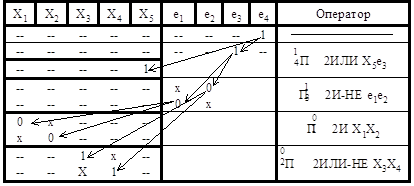

Пример анализа КС (рис 9. ) методом p - алгоритма представлен в табл. 5. В последней колонке этой таблицы приведен оператор подстановки, в результате работы которого сигнал на выходе ЛЭ заменяется соответствующим покрытием. Необходимо обратить внимание, что все значения переменных, записанные в одной строке, должны одновременно быть в наличии для обеспечения заданного значения выходного сигнала. По-

этому, при замене одного из значений в строке соответствующим покрытием, все остальные значения для других переменных в этой строке должны присутствовать совместно с этим покрытием.

На основании полученного единичного покрытия можно записать БФ, реализуемую схемой:

![]()

Таблица 5 Анализ схемы методом p – алгоритма.

а) Получение первого покрытия![]()

|

|

б) Получение нулевого покрытия ![]()

В дальнейшем можно сравнить полученную БФ с той, по которой строилась схема и проверить правильность ее построения. При анализе схемы может оказаться, что некоторая переменная, получившая на одном из предыдущих шагов некоторые значения на данном шаге должна принять противоположное значение. Возникшее противоречие говорит о том, что данный путь является тупиковым и его необходимо исключить из дальнейшего рассмотрения. Если ни при одной комбинации входных переменных не обеспечивается значение 1(0) на выходе, то это означает, что схема реализует константу 0(1) соответственно.

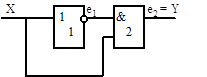

1. 8 Анализ КС методом синхронного моделирования.

При данном методе считается, что все ЛЭ переключаются одновременно, без задержки. В результате применения метода определяется установившееся значение сигнала на выходе схемы.

Рассмотрим метод синхронного моделирования на примере схемы ( рис.9 ).

На первом этапе схему разбиваем на уровни и записываем в порядке возрастания уровня уравнения, описывающие функционирование ЛЭ:

|

Проанализируем схему при подаче на вход набора X1=0, Х2=0, Х3=0, Х4=1, Х5=1. Для этого решаем записанные уравнения в порядке возрастания уравнения. Имеем:

![]() ;

;

![]() ;

;

![]() ;

;

![]() .

.

Следовательно, при подаче на вход набора {00011}, на выходе будет Y=1. Аналогично можно промоделировать работу схемы при подаче на вход любого другого набора.

1.9 Анализ КС методом асинхронного моделирования.

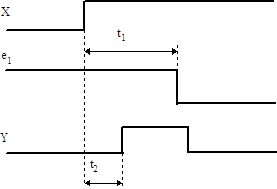

Реальный ЛЭ переключается за какое-то конечное время, зависящее от технологии изготовления, условий эксплуатации, емкостей нагрузки и т.д. Прохождение сигнала последовательно через несколько ЛЭ будет приводить к накоплению времени задержки и возникновению сдвига во времени выходного сигнала по отношению ко входному. Наличие задержки и порождаемого ею временного сдвига сигналов может приводить к появлению на выходе отдельных ЛЭ и всей схемы в целом кратковременных сигналов, не предусмотренных БФ, реализуемой схемой. Как иллюстрацию, рассмотрим схему рис.11, а .

|

|

Рис. 11 а)

|

|

Рис. 11 . Статический риск сбоя.

а)- схема, б)- временные диаграммы.

t1-время задержки инвертора

t2-время задержки элемента 2И

Данная схема реализует функцию ![]() , т.е. константу

0 независимо от входного сигнала X. Однако в переходном процессе в результате

задержки срабатывания ЛЭ возможна ситуация, когда на обоих входах элемента 2И

будут логические единицы, что может привести к появлению на выходе схемы

логической 1 (см. рис.11 б). Рассмотренный случай возможен при задержке

срабатывания второго элемента больше, чем первого. Такое явление называется риском

сбоя. Различают статистический и динамический риски сбоя.

, т.е. константу

0 независимо от входного сигнала X. Однако в переходном процессе в результате

задержки срабатывания ЛЭ возможна ситуация, когда на обоих входах элемента 2И

будут логические единицы, что может привести к появлению на выходе схемы

логической 1 (см. рис.11 б). Рассмотренный случай возможен при задержке

срабатывания второго элемента больше, чем первого. Такое явление называется риском

сбоя. Различают статистический и динамический риски сбоя.

При статическом риске сбоя до и после переходного процесса состояние выходного сигнала одно и то же, а во время переходного процесса возможно кратковременное появление противоположного сигнала.

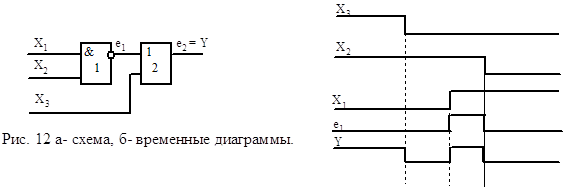

При динамическом риске сбоя до и после переходного процесса состояния выходного сигнала противоположные, но в переходном процессе выходной сигнал несколько раз меняет свое значение. Динамический риск сбоя возможен в схеме (рис.12 а) при смене набора (Х1=0, Х2=1, Х3=1) на набор (Х1=1, Х2=0, Х3=0) и иллюстрируется диаграммами (рис.12 б).

В данном примере динамический риск сбоя на выходе КС сопровождается статическим на выходе элемента 1. Как видно из временных диаграмм риск сбоя имеет место при наличии определенного временного сдвига между сигналами, поступающими на вход ЛЭ. Нежелательные сигналы на выходе могут и отсутствовать при другом соотношении временных сигналов, однако принципиальная возможность их появления является фактором снижающим надежность работы схемы. Поэтому очень важно уметь обнаруживать и устранять такие явления.

|

|

Для анализа процесса переключения КС при смене входных наборов и обнаружения рисков сбоя используется метод асинхронного моделирования. При этом методе считается, что каждый элемент переключается с одинаковой задержкой. Анализ включает такие этапы:

1.Каждому элементу схемы присваивается уровень, причем уровень 1 имеют элементы, все входы которых являются независимыми входами схемы.

2.Записываются уравнения, описывающие каждый ЛЭ в порядке убывания уровня.

3.Для исходного входного набора А(X1, X2, … , Xn ) определяется значение сигналов на выходах всех ЛЭ схемы. Пусть данный набор А заменяется набором В(X1, X2, … , Xn ).

4.Помечаются те уравнения, в правой части которых хотя бы одна из переменных изменила свое значение.

5.Решаются помеченные уравнения в порядке их записи в схеме . После решения уравнение считается непомеченным.

6.Если после решения всех уравнений системы переменные, входящие в левые части уравнений, изменили свои значения, то вновь помечаются те уравнения, в правые части которых входят эти переменные. Затем осуществляется переход к п.5. В противном случае моделирование данного входного набора считается законченным. Выполнение п.5 называется тактом моделирования.

Анализ схемы (рис.13) методом асинхронного моделирования приведен ниже. Для данной схемы входной набор А(1011110) заменяется набором В(1101011).

|

|

Рис. 13. Комбинационная схема для метода асинхронного моделирования.

Уравнения, описывающие ЛЭ:

|

Табл. 6 Таблица моделирования схемы

Выходы Такты моделирования Прим.

0 1 2 3

e6 1 0 1 0 дин.

e5 0 1 0 0 стат.

e4 0 0 0 0

e3 1 0 0 0

e2 1 0 0 0

e1 0 1 0 1

Как следует из результатов моделирования, при смене набора А набором В на выходе элемента 4 имеет место статический риск сбоя, а на выходе схемы - динамический риск сбоя.

Радикальным способом устранения рисков сбоя является введение стробирования для снятия выходного сигнала КС. Стробирующий импульс подается после окончания переходного процесса в КС (т.е. когда на выходе КС уже установилось необходимое значение выходного сигнала), что исключает влияние возможных сбоев на вырабатываемый схемой сигнал.

ОСНОВНЫЕ ПОНЯТИЯ И ОПРЕДЕЛЕНИЯ ТЕОРИИ АБСТРАKТНЫХ АВТОМАТОВ.

Ознакомившись в курсах "Программирование" и "Машинная арифметика" с принципами работы ЭЦВМ, можно указать на две основные особенности таких вычислительных машин: оперирование данными, представленными в цифровой форме и автоматическая работа по заранее составленной программе. Эти особенности показывают, что любая ЭЦВМ является цифровым автоматом (ЦА). Понятие ЦА служит обобщением для всех видов устройств обработки цифровой информации, имеющих программное управление.

Цифровой автомат - устройство, характеризующееся набором внутренних состояний в которое оно попадет под воздействием команд заложенной в него программы. Переход автомата из одного состояния в другое осуществляется в определенный момент времени.

Математической моделью ЦА (а в общем случае любого дискретного устройства) является так называемый абстрактный автомат, определенный как 6-компонентный кортеж: S=(A,Z,W,d,l,а1) у которого:

1. A={a1, a2, ... ,am} - множество состояний (внутренний алфавит)

2. Z={z1, z2, ... ,zf} - множество входных сигналов (входной алфавит)

3. W={w1, w2, ..., wg} - множество выходных сигналов (выходной алфавит)

4. d : A·Z®A - функция переходов, реализующая отображение Dd ÍА·Z в А. Иными словами функция d некоторым парам состояние - входной сигнал (аm, zf) ставит в соответствие состояния автомата аs= d (am, zf), asÎA.

5. l : A·Z®W - функция выходов, реализующая отображение Dl ÍА·Z на W. Функция l некоторым парам состояние - входной сигнал (аm, zf) ставит в соответствие выходные сигналы автомата Wg=l(аm, zf) , WgÎW.

6. ai ÎA - начальное состояние автомата.

Под алфавитом здесь понимается непустое множество попарно различных символов. Элементы алфавита называются буквами, а конечная упорядоченная последовательность букв - словом в данном алфавите.

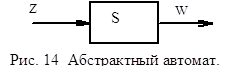

|

|

Абстрактный автомат (рис.14) имеет один вход и один выход. Автомат работает в дискретном времени, принимающем целые неотрицательные значения t = 0,1,2,... В каждый момент t дискретного времени автомат находится в некотором состоянии a(t) из множества состояний автомата, причем в начальный момент t = 0 он всегда находится в начальном состоянии a(0)=a1. В момент t, будучи в состоянии a(t), автомат способен воспринять на входе букву входного алфавита z(t) Î Z. В соответствии с функцией выходов он выдаст в тот же момент времени t букву выходного алфавита W(t)=l(a(t), z(t)) и в соответствии с функцией переходов перейдет в следующее состояние a(t+1)=d[a(t), z(t)], a(t) ÎA, w(t) ÎW.

Смысл понятия абстрактного автомата состоит в том, что он реализует некоторое отображение множества слов входного алфавита Z во множество слов выходного алфавита W. Т.е. если на вход автомата, установленного в начальное состояние a1, подавать буква за буквой некоторую последовательность букв входного алфавита z(0), z(1),... - входное слово, то на выходе автомата будут последовательно появляться буквы выходного алфавита w(0), w(1),... - выходное слово. Т.о. выходное слово = j(входное слово), где j - отображение, осуществляемое абстрактным автоматом.

На уровне абстрактной теории понятие "работа автомата" понимается как преобразование входных слов в выходные. Можно сказать, что в абстрактном автомате отвлекаемся от его структуры - содержимого прямоугольника (рис. 14 ), рассматривая его как "черный ящик", т.е. основное внимание уделяем поведению автомата относительно внешней среды.

Понятие состояния в определении автомата введено в связи с тем, что часто возникает необходимость в описании поведения систем, выходы которых зависят не только от состояния входов в данный момент времени, но и от некоторой предыстории, т.е. от сигналов, которые поступали на входы системы ранее. Состояния как раз и соответствуют некоторой памяти о прошлом, позволяя устранить время как явную переменную и выразить выходной сигнал как функцию состояния и входа в данный момент времени.

На практике наибольшее распространение получили два класса автоматов - автоматы Мили (Mealy) и Мура (Moore).

Закон функционирования автомата Мили задается уравнениями:

a(t+1) = d(a(t), z(t)); w(t) = l(a(t), z(t)), t = 0,1,2,...

Закон функционирования автомата Мура задается уравнениями:

a(t+1)=d(a(t), z(t)); w(t) = l(a(t)), t = 0,1,2,...

Из сравнения законов функционирования видно, что, в отличие от автомата Мили, выходной сигнал в автомате Мура зависит только от текущего состояния автомата и в явном виде не зависит от входного сигнала. Для полного задания автомата Мили или Мура дополнительно к законам функционирования, необходимо указать начальное состояние и определить внутренний, входной и выходной алфавиты.

Кроме автоматов Мили и Мура иногда оказывается удобным пользоваться совмещенной моделью автомата, так называемым С- автоматом.

Под абстрактным С- автоматом будем понимать математическую модель дискретного устройства, определяемую восьмикомпонентным вектором S=( A, Z, W, U, d, l1, l2, а1 ), у которого:

1. A={a1, a2, ... ,am} - множество состояний;

2. Z={z1, z2, ... ,zf} - входной алфавит;

3. W={w1, w2, ..., wg} - выходной алфавит типа 1;

4. U={u1, u2,...,uh} - выходной алфавит типа 2;

5. d : A · Z ® A - функция переходов, реализующая отображение Dd ÍА·Z в А;

6. l1 : A · Z ® W - функция выходов, реализующая отображение Dl1 ÍА·Z в W;

7. l2 : A ® U - функция выходов, реализующая отображение Dl2 Í А в U;

8. а1 Î А - начальное состояние автомата.

Абстрактный С- автомат можно представить в виде устройства с одним входом, на который поступают сигналы из входного алфавита Z, и двумя выходами, на которых появляются сигналы из алфавитов W и U. Отличие С - автомата от моделей Мили и Мура состоит в том, что он одновременно реализует две функции выходов l1 и l2, каждая из которых характерна для этих моделей в отдельности. Закон функционирования С- автомата можно описать следующими уравнениями:

а( t + 1) = d( a( t ), z( t )); w( t ) = l1( a ( t ), z( t )); u( t ) = l2( a( t )); t = 0, 1, 2, ...

Выходной сигнал Uh=l2( am ) выдается все время, пока автомат находится в состоянии am. Выходной сигнал Wg=l1( am, zf ) выдается во время действия входного сигнала Zf при нахождении автомата в состоянии am.

Рассмотренные выше абстрактные автоматы можно разделить на:

1) полностью определенные и частичные;

2) детерминированные и вероятностные;

3) синхронные и асинхронные;

Полностью определенным называется абстрактный цифровой автомат, у которого функция переходов и функция выходов определены для всех пар ( ai, zj ).

Частичным называется абстрактный автомат, у которого функция переходов или функция выходов, или обе эти функции определены не для всех пар ( ai, zj ).

К детерминированным относятся автоматы, у которых выполнено условие однозначности переходов : автомат, находящийся в некотором состоянии ai, под действием любого входного сигнала zj не может перейти более, чем в одно состояние.

В противном случае это будет вероятностный автомат, в котором при заданном состоянии ai и заданном входном сигнале zj возможен переход с заданной вероятностью в различные состояния.

Для определения синхронных и асинхронных автоматов вводится понятие устойчивого состояния. Состояние as автомата называется устойчивым, если для любого состояния ai и входного сигнала zj таких, что d( ai, zj ) = as имеет место d( as, zj ) = as, т.е. состояние устойчиво, если попав в это состояние под действием некоторого сигнала zj, автомат выйдет из него только под действием другого сигнала zk, отличного от zj.

Автомат, у которого все состояния устойчивы - асинхронный.

Автомат называется синхронным, если он не является асинхронным.

Абстрактный автомат называется конечным, если конечны множества А = {a1, a2, ..., am}, Z = {z1, z2, ..., zf}, W = {w1, w2, ..., wg}. Автомат носит название инициального, если в нем выделено начальное состояние a1.

СПОСОБЫ ОПИСАНИЯ И ЗАДАНИЯ АВТОМАТОВ.

Для того, чтобы задать автомат, необходимо описать все компоненты кортежа S=(A, Z, W, d, l, а1 ). Множества А, Z, W описываются и задаются простым перечислением своих элементов. Среди многообразия различных способов заданий функций d и l ( следовательно и всего автомата в целом ) наибольшее распространение получили табличный и графический.

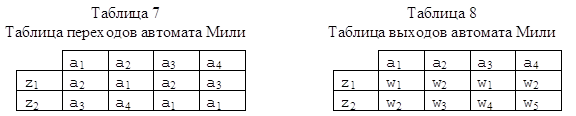

При табличном способе задания автомат Мили описывается с помощью двух таблиц. Одна из них (таблица переходов ) задает функцию d, т.е. a( t +1) = d( a( t ), z( t )) ( табл.7), вторая (таблица выходов ) - функцию l, т.е. W( t )=l( a( t ), z( t )) ( табл. 8 ).

|

|

Каждому столбцу из приведенных таблиц поставлено в соответствие одно состояние из множества А, каждой строке - один входной сигнал из множества Z. На пересечении столбца am и строки zf в табл.7 записывается состояние as, в которое должен перейти автомат из состояния am под действием входного сигнала Zf, т.е. as = d(am, zf). На пересечении столбца am и строки zf в табл.8 записывается выходной сигнал Wg, выдаваемый автоматом в состоянии am при поступлении на вход сигнала zf, т.е. Wg = l( am, zf ).

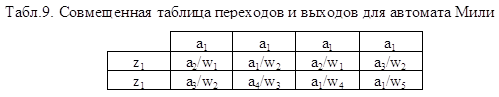

Для приведенных таблиц множества, образующие автомат A={a1, a2, a3,a4}, Z={z1, z2}, W={w1, w2, w3, w4, w5}. Автомат Мили может быть задан одной совмещенной таблицей переходов и выходов (табл.9), в которой каждый элемент as / wg записанный на пересечении столбца am и строки zf, определяется следующим образом:

|

|

as=d(am, zf); wf=l(am, zf).

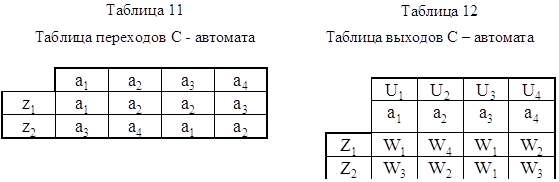

Автомат Мура задается одной отмеченной таблицей переходов (табл.10), в которой каждому столбцу приписаны не только состояние am , но еще и выходной сигнал Wg, соответствующий этому состоянию, где Wg=l(am).

|

|

Для частичных автоматов Мили и Мура в рассмотренных таблицах на месте не определенных состояний и выходных сигналов ставится прочерк. В таких автоматах выходной сигнал на каком-либо переходе всегда не определен, если неопределенным является состояние перехода. Кроме того, выходной сигнал может быть неопределенным и для некоторых существующих переходов.

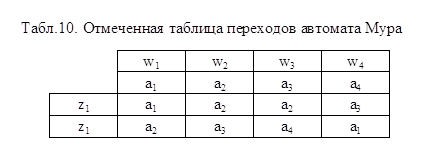

Для задания С - автоматов также используется табличный метод. В этом случае таблица переходов (табл.11) аналогична таблице переходов автомата Мили, а в таблице выходов каждое состояние отмечено соответствующим выходным сигналом ui выходного алфавита типа 2 (табл.12)

|

|

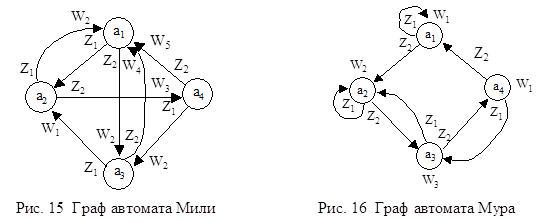

При графическом способе автомат

задается в виде ориентированного графа, вершины которого соответствуют

состояниям, а дуги - переходам между ними. Дуга, направленная из вершины am, задает переход в автомате из состояния am в состояние as. В

начале этой дуги записывается входной сигнал ZfÎZ, вызывающий данный переход

as=d(am,zf). Для графа

автомата Мили выходной сигнал wgÎW, формируемый на переходе,

записывается в конце дуги, а для автомата Мура - рядом с вершиной am, отмеченной состоянием am,

в котором он формируется. Если переход в автомате из состояния am в состояние as

производится под действием нескольких входных сигналов, то дуге графа,

направленной из am в as,

приписываются все эти входные и соответствующие выходные сигналы. Граф С-

автомата содержит выходные сигналы двух типов и они обозначаются на графе как

на графах соответствующих автоматов. Графы автоматов, заданных своими

таблицами переходов и выходов

(табл. 7¸12) представлены на

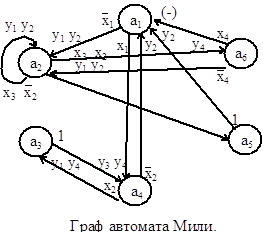

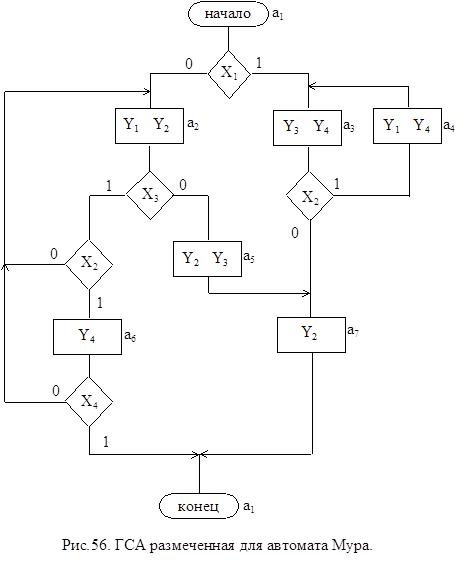

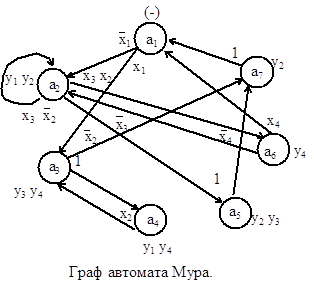

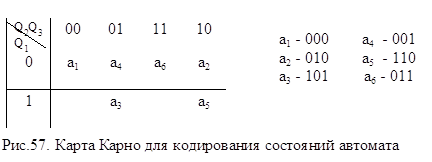

рисунках 15,16,17.

|

|

|

|

СВЯЗЬ МЕЖДУ МОДЕЛЯМИ МИЛИ И МУРА.

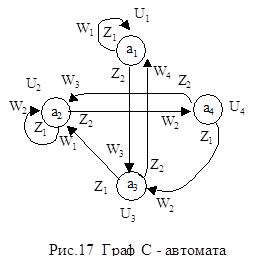

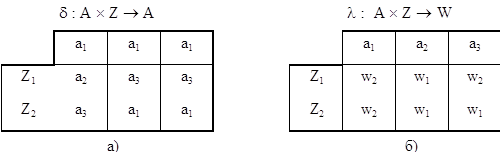

Рассмотрим некоторый автомат Мили, заданный таблицами переходов и выходов. Таблица переходов а) и выходов б) автомата Мили

|

|

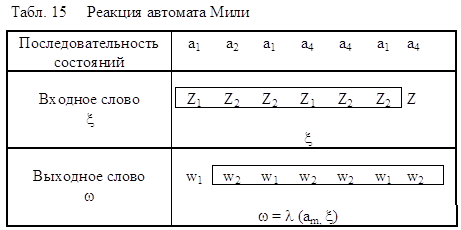

Подадим на вход автомата, установленного в состояние а1, входное слово x=z1 z2 z2 z1 z2 z2. Так как d(а1, z1) = a2, l(a1, z1) = W2, то под воздействием входного сигнала z1 автомат перейдет в состояние а2 и выдаст на переходе выходной сигнал W2. Затем, находясь в состоянии а2 под воздействием сигнала Z2 перейдет в состояние а1=d(а2, z2) и выдаст сигнал W1=l(a2, z2) и т.д. В табл. 13 приведена последовательность состояний, которые автомат проходит, воспринимая входное слово x, и выходные сигналы, вырабатываемые на этих переходах.

|

|

Назовем выходное слово w = l (a1, x) реакцией автомата Мили в состоянии а1 на входное слово x.

В нашем случае w = w2 w1 w2 w2 w1 w2

Как видно, из приведенного примера, в ответ на входное слово длины k автомат Мили выдаст последовательность состояний длины k +1 и выходное слово длины k.

|

|

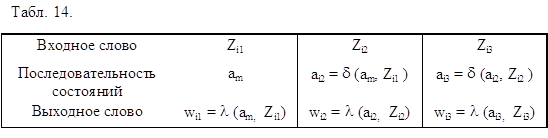

В общем виде поведение автомата Мили, установленного в состояние am, можно описать следующим образом (табл. 14).

Аналогично можно описать поведение автомата Мура, находящегося в состоянии a1, при приходе входного слова

x = Zi1, Zi2, . . . , Zik ,учитывая, что W( t ) = l(a( t )):

|

Очевидно, что для автомата Мура выходной сигнал Wi1= l(am) в момент времени i1 не зависит от входного сигнала Zi1 и определяется только состоянием am. Следовательно, сигнал Wi1 никак не связан с входным словом x.

В связи с этим под реакцией автомата Мура, установленного в состояние am, на входное слово x = Zi1, Zi2, . . . , Zik будем понимать выходное слово той же длины w = l(am, x) = Wi2 Wi3 ...Wik+1, сдвинутое по отношению к x на один такт.

Рассмотрим пример. Пусть задан автомат Мура:

Подадим на вход этого автомата ту же последовательность, что и для автомата Мили: x=z1 z2 z2 z1 z2 z2. Последовательность смены состояний и вырабатываемых выходных сигналов представлена в таблице:

|

|

Сравнивая реакции автомата Мили (табл. 13) и автомата Мура (табл.15), отмечаем, что эти реакции на одно и то же слово x совпадают. Следовательно автоматы Мили и Мура реализуют одно и то же преобразование слов входного алфавита. Такие автоматы называются эквивалентными. Строгое определение эквивалентности следующее:

два автомата с одинаковыми входными и выходными алфавитами называются эквивалентными, если после установки их в начальное состояние их реакции на любое входное слово совпадают.

Для каждого автомата Мили может быть построен эквивалентный ему автомат Мура и наоборот.

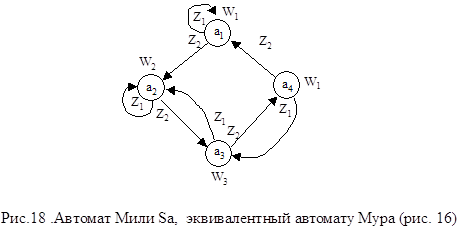

Переход от автомата Мура к эквивалентному ему автомату Мили тривиален и легко осуществляется при графическом способе задания автомата. Для получения графа автомата Мили необходимо выходной сигнал Wg, записанный рядом с вершиной as исходного автомата Мура, перенести на все дуги, входящие в эту вершину. На рис. 18 приведен граф автомата Мили, эквивалентного автомату Мура (рис. 16)

|

|

Легко убедиться, что полученный автомат Мили действительно эквивалентный исходному автомату Мура. Для этого достаточно рассмотреть реакцию обеих автоматов на произвольную входную последовательность, что предлагается выполнить самостоятельно. Необходимо также отметить, что в эквивалентном автомате Мили количество состояний такое же, как и в исходном автомате Мура.

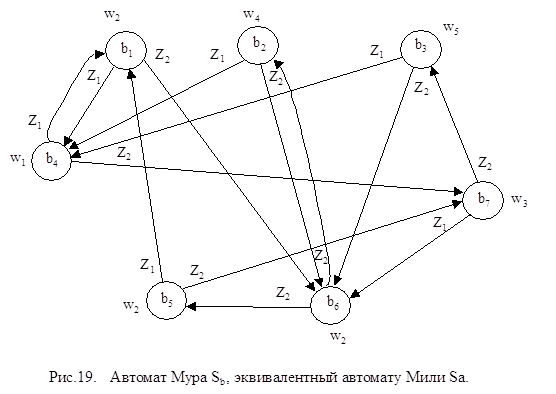

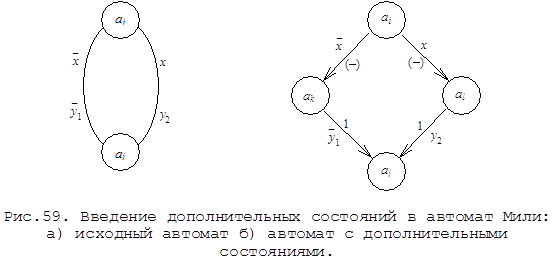

Переход от автомата Мили к эквивалентному ему автомату Мура более сложен. Это связано с тем, что в автомате Мура в каждом состоянии вырабатывается только один выходной сигнал. Как и в предыдущем случае, переход наиболее наглядно делать при графическом способе задания автомата. В этом случае каждое состояние ai исходного автомата Мили порождает столько состояний автомата Мура, сколько различных выходных сигналов вырабатывается в исходном автомате при попадании в состояние ai. Рассмотрим переход от автомата Мили Sa к автомату Мура Sb на примере автомата (рис. 15).

Как следует из рис. 15 для автомата Sa при попадании в состояние а1 вырабатываются выходные сигналы W2, W4, W5, при попадании в а2 – W1, W2, a3 – W2, a4 – W3. Каждой паре состояние ai - выходной сигнал Wj, который вырабатывается при попадании в это состояние, поставим в соответствие состояние bk эквивалентного автомата Мура Sb с тем же выходным сигналом Wj : b1 = (a1, W2), b2 = (a1, W4), b3 = (a1, W5), b4 = (a2, W1), b5 = (a2, W2), b6 = (a3, W2), b7 = (a4, W3), т.е. каждое состояние ai автомата Мили порождает некоторое множество Ai состояний эквивалентного автомата Мура: A1 = { b1, b2, b3 }, A2 = { b4, b5 }, A3 = { b6 }, A4 = { b7 }. Как видно, в эквивалентном автомате Мура количество состояний 7. Для построения графа Sb поступаем следующим образом. Т.к. в автомате Sa есть переход из состояния а1 в состояние а2 под действием сигнала z1 с выдачей W1, то из множества состояний A1 = {b1, b2, b3}, порождаемых состоянием а1 автомата Sa в автомате Sb должен быть переход в состояние (a3, W2) = b6 под действием сигнала Z2 и т.д. Граф эквивалентного автомата Мура представлен на рис.19.

|

|

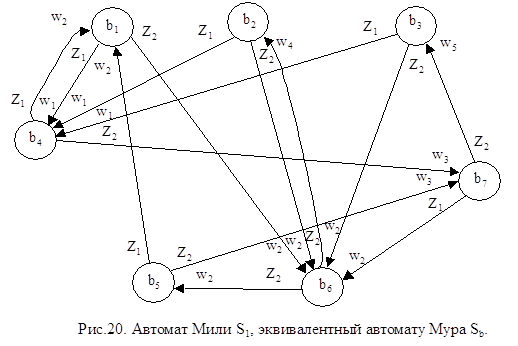

Если от автомата Мура Sb, эквивалентного автомату Мили Sa (рис. 19) вновь перейти к автомату Мили, то получим автомат Мили S1 (рис. 20)

|

|

Вследствие транзитивности отношения эквивалентности два автомата Мили S1 и Sa также будут эквивалентными, но у последнего будут на 3 состояния больше. Т.о., эквивалентные между собой автоматы могут иметь различное число состояний, в связи с чем возникает задача нахождения минимального (т.е. с минимальным числом состояний) автомата в классе эквивалентных между собой автоматов.

МИНИМИЗАЦИЯ ЧИСЛА ВНУТРЕННИХ СОСТОЯНИЙ ПОЛНОСТЬЮ ОПРЕДЕЛЕННЫХ АВТОМАТОВ.

Рассмотрим метод минимизации полностью определенных автоматов, предложенный Ауфенкампом и Хоном.

Основная идея этого метода заключается в разбиении всех состояний исходного абстрактного автомата на попарно непересекающиеся классы эквивалентных состояний и замене каждого класса эквивалентности одним состоянием. Т.о. получающийся в результате минимальный автомат имеет столько состояний, на сколько классов эквивалентности разбиваются состояния исходного автомата.

Для пользования методом введем несколько определений.

Два состояния абстрактного автомата называются 1-эквивалентными в том случае, если реакции автомата в этих состояниях на всевозможные входные слова совпадают.

Объединение всех 1-эквивалентных состояний абстрактного автомата образует 1-класс эквивалентности.

1-эквивалентные состояния автомата называются 2-эквивалентными, если они переводятся любым входным сигналом также в 1-эквивалентные состояния.

Объединение всех 2-эквивалентных состояний образует 2-класс эквивалентности.

По индукции можно распространить определение до i-эквивалентных состояний и i-классов эквивалентности.

Если для некоторого i разбиения состояний автомата на ( i +1) - классы совпадает с разбиением на i-классы, то оно является разбиением и на ¥ - классы эквивалентности.

Разбиение множества внутренних состояний автомата на ¥ - классы и является требуемым разбиением на классы эквивалентности, при этом такое разбиение может быть получено за конечное число шагов.

Все вышеизложенное непосредственно применимо к минимизации автомата Мили. При минимизации полностью определенных автоматов Мура вводится понятие 0-эквивалентности состояний и разбиение множества состояний на 0-эквивалентные классы: к такому классу относятся одинаково отмеченные состояния автомата Мура.

Если два 0-эквивалентных состояния любым входным сигналом переводится в два 0-эквивалентных состояния, то они называются 1-эквивалентными. Все дальнейшие классы эквивалентности состояний для автомата Мура определяются аналогично приведенному для автоматов Мили.

|

|

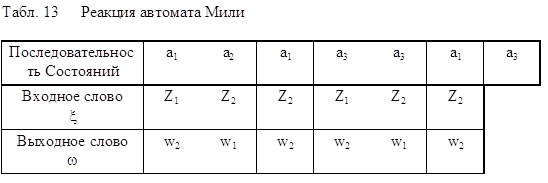

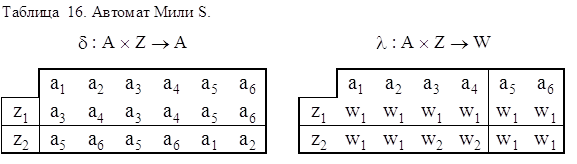

Рассмотрим пример минимизации автомата Мили, заданного таблицами переходов и выходов :

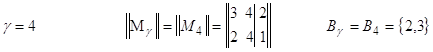

Из таблицы выходов получаем разбиение на 1-классы эквивалентности p1, объединяя в эквивалентные классы Bi состояния с одинаковыми столбцами:

p1 = {B1, B2}; B2 = {a1, a2, a5, a6}; B2 = {a3, a4}

|

|

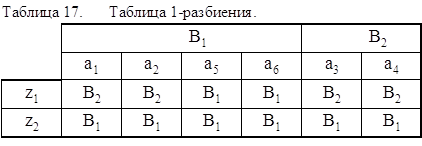

Для получения 2-эквивалентных состояний строим таблицу 1-разбиения (табл.17), заменяя в таблице переходов состояния a1 соответствующими классами эквивалентности B1 или B2.

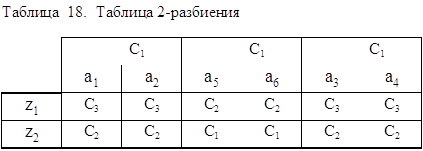

Из полученной таблицы 1-разбиения получаем 2-классы эквивалентности Ci и разбиение p2 = {C1, C2, C3}, где С1 = {a1, a1}, C2 = {a5, a6}, C3 = {a3, a4}. Сравнивая p2 и p1, отмечаем, что эти разбиения отличаются друг от друга. Поэтому аналогично строим таблицу 2-разбиения (табл. 18), опять заменяя в таблице переходов состояния ai соответствующими классами эквивалентности Ci.

|

|

Из полученной таблицы 2-разбиения получаем 3-классы эквивалентности Di и разбиение p3 ={ D1, D2, D3}, где D1 = {a1, a2}, D2 = {a5, a6}, D3 = {a3, a4}.

|

|

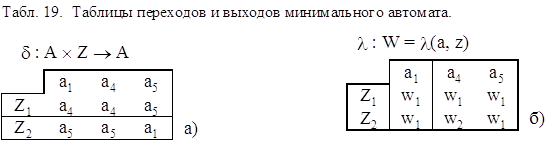

Сравнивая p3 и p2, замечаем, что D1 = C1, D2 = C2, D3 = C3, p3 = p3. Следовательно получили разбиение на ¥- эквивалентные классы. Т.к. всего три таких класса, то минимальный автомат будет содержать всего три состояния. Выбираем из каждого класса Di по одному состоянию и получаем множество состояний A' минимального автомата. Пусть, например, A'={a1, a4, a5}. Для получения минимального автомата из первоначальных таблиц переходов и выходов (табл. 16) вычеркиваем столбцы, соответствующие "лишним состояниям" a2, a3, a6. В результате получается минимальный автомат Мили, эквивалентный исходному автомату (табл. 19).

Минимизацией числа внутренних состояний автомата заканчивается этап абстрактного синтеза.

Структурный синтез ЦА.

Задачи синтеза ЦА.

Канонический метод структурного синтеза ЦА.

Элементарные цифровые автоматы с памятью

(триггерные устройства) и их свойства.

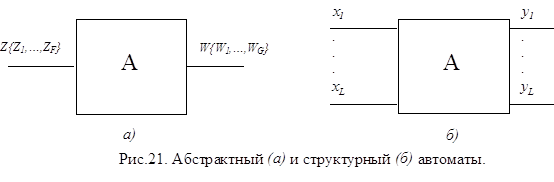

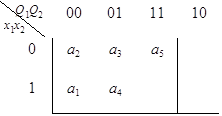

Вслед за этапом абстрактного синтеза автоматов следует этап структурного синтеза, целью которого является построение схемы, реализующей автомат из элементов заданного типа. Если абстрактный автомат был лишь математической моделью, проектируемого устройства, то в структурном автомате учитывается структура входных и выходных сигналов автомата, а также его внутренне устройство на уровне логических схем. Основной задачей структурной теории автоматов является разработка общих методов построения структурных схем автоматов.

В отличие от абстрактного автомата, имеющего один вход и один выход, на которые поступают сигналы во входном и выходят в выходном W={W1,..,WG} алфавитах, структурный автомат имеет L входных каналов х1,х2,..,хL и N выходных y1,y2,…,yN на каждом из которых присутствует сигнал структурного алфавита.

|

|

Обычно в качестве структурного используется двоичный алфавит.

В этом случае каждому входному сигналу ZF абстрактного автомата соответствует некоторый двоичный вектор (lf1,lf2,..,lfL), где lfLÎ{0,1}.

Очевидно, что для представления (кодирования) входных сигналов Z1,..,ZF абстрактного автомата различными двоичными векторами должно быть выполнено условие

L ![]() ] log2F

[,

] log2F

[,

аналогично

N ![]() ] log2G

[

] log2G

[

Например , Z={Z1,Z2,Z3,Z4} W={W1,W2,W3}.

Тогда L

![]() log24=2 N

log24=2 N ![]() log23=2

log23=2

Закодировать входные и выходные сигналы можно ,например, так:

Z1 = 00 W1 = 00

Z2 = 01 W2 = 01

Z3 = 10 W3 = 11

|

|

Z4 = 11

|

Задача синтеза структуры автомата.

На этапе структурного синтеза предварительно выбираются элементарные автоматы, путем композиции которых строят логические схемы полученных на этапе абстрактного синтеза автоматов Мили и Мура. Если решение задачи структурного синтеза существует, говорят, что заданная система автоматов структурно полна.

Рассмотрим канонический метод структурного синтеза при котором используются элементарные автоматы некоторого специального вида – автоматы с памятью, имеющие более одного состояния, и автоматы без памяти – с одним состоянием. Первые автоматы называются элементами памяти, вторые – комбинационные или логические элементы.

Теоретическим обоснованием канонического метода структурного синтеза автоматов служит теорема о структурной полноте:

|

|

Для правильной работы схем сигналы на входе запоминающих элементов не должны непосредственно участвовать в образовании выходных сигналов, которые по цепям обратной связи подавались бы в тот же самый момент времени на эти входы. Поэтому запоминающими элементами должны быть не автоматы Мили, а автоматы Мура. Таким образом, структурно полная система элементарных автоматов должна содержать хотя бы один автомат Мура. В то же время, для синтеза автоматов с минимальным числом элементов памяти, необходимо в качестве таких элементов выбирать автоматы Мура, имеющие полную систему переходов и полную систему выходов – полные автоматы.

Полнота системы переходов означает, что для любой упорядоченной пары состояний автомата найдётся входной сигнал, переводящий первый элемент этой пары во второй, т.е в таком автомате в каждом столбце таблицы переходов должны встречаться все состояния автомата.

Полнота системы выходов автомата Мура состоит в том, что каждому состоянию автомата поставлен в соответствие свой особый выходной сигнал, отличный от выходных сигналов других состояний. Т.о. в таком автомате число выходных сигналов равно числу состояний автомата. В связи с этим, в автоматах памяти будем использовать одни и те же обозначения и для состояний, и для выходных сигналов.

|

|

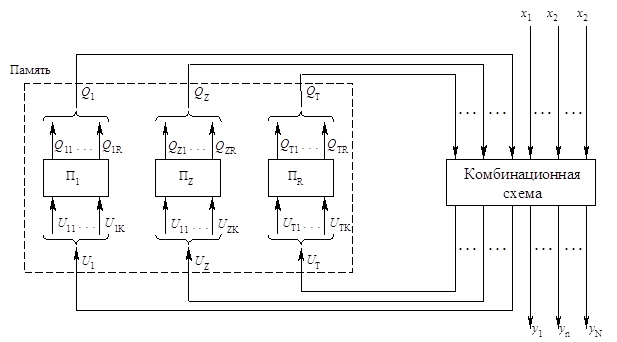

Канонический метод структурного синтеза предполагает представление структурной схемы автомата в виде двух частей: памяти и комбинационной схемы.

Память состоит из элементарных автоматов Мура П1,....,ПZ,....,ПR. После выбора элементов памяти каждое состояние синтезируемого автомата А кодируется набором их состояний. Если все автоматы П1...,ПR одинаковы, что в общем случае необязательно, то их число

![]()

где

M – число состояний синтезируемого автомата А, а b – число

состояний элементарного автомата памяти. Обычно для элементарного автомата b=2,

тогда ![]() .

.

Например, переход автомата А, имеющего 5 элементов памяти, алфавит состояний которых – двоичный, из одного состояния (Am)=01011 в другое (A3)= 11000, заключается в изменении состояний соответствующих автоматов памяти: первый элемент памяти переходит из 0 в 1, второй – из 1 в 1, третий из 0 в 0, четвёртый – из 1 в 0, пятый - из 1 в 0.

Переходы автоматов памяти, соответствующие переходам в автомате А, происходят под действием сигналов возбуждения памяти, поступающих с выхода комбинационной схемы на вход памяти автомата. Так на рисунке X=(X1,X2,..,XL) и Y=(Y1,Y2,...,YN) – векторные структурные входной и выходной сигналы автомата, U=(U1,U2,...,UT) – векторная функция возбуждения памяти и Q=(Q1,...,QT) – вектор выходного сигнала обратной связи от элементов памяти автомата.

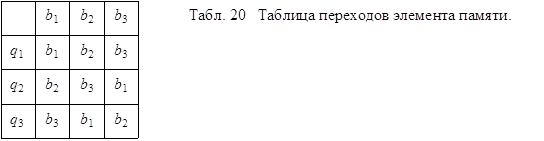

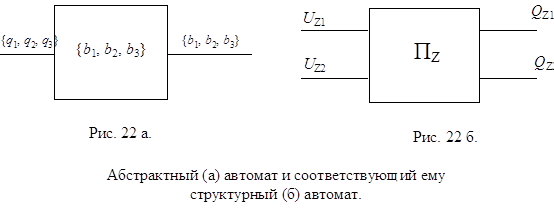

Рассмотрим отдельно элемент памяти Пz, таблица переходов которого дана в таблице. Множество выходных сигналов элементов памяти совпадает с множеством внутренних состояний.

|

|

Полнота переходов очевидна из таблицы (в каждом столбце все состояния встречаются). При рассмотрении автомата на абстрактном уровне его можно представить в виде рис.22 а.

|

|

При переходе от абстрактного автомата к

структурному, входные и выходные сигналы должны быть закодированы наборами

сигналов структурного алфавита (входного или выходного соответственно). При

двоичном структурном алфавите автомат Пz будет иметь два входных ![]() и два выходных

и два выходных ![]() канала.

канала.

Итак, сами компоненты Uz и Qz при Z = 1,...,R векторов сигналов возбуждения памяти U и сигналов обратной связи от памяти Q также могут быть представлены в виде векторов:

Uz = (UZ1,UZ2,...,UZK) и QZ = (QZ1,QZ2,...,QZR).

Если не оговорено особо, то используется двоичный структурный алфавит как для входных и выходных каналов синтезируемого автомата, так и для входных и выходных каналов автоматов памяти. Алфавит состояний автоматов памяти также обычно двоичный.

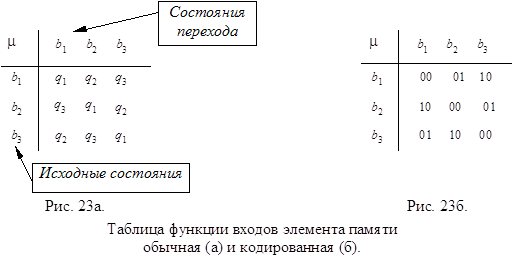

При построении функций возбуждения памяти автомата используют функцию входов элемента памяти m(bi,bj), ставящую в соответствие каждой паре состояний (bi,bj) сигнал, который должен быть подан на вход этого автомата для перевода его из состояния bi в состояние bj. Функцию входов удобно задавать в виде таблицы. Для элемента памяти (функция переходов которого приведена ранее) функция входов имеет вид:

|

|

Если входные сигналы элемента памяти q1,...,qp закодированы наборами (UZ1,...,UZK) сигналов на его входных каналах, то элементами таблицы, задающей функцию входов вместо qi будут соответствующие наборы. Так, если q1 = 00, q2 = 01, q3 = 10, то соответствующая f входов будет иметь вид рис.23a.

Элементарные цифровые автоматы – элементы памяти.

В качестве элементов памяти структурного автомата обычно используются триггеры.

Триггер – это устройство, имеющее два устойчивых состояния, в которые он переходит под действием определённых входных сигналов.

Обычно в триггерах выделяют два вида входных сигналов (и соответственно входов): информационные и синхросигналы.

Информационные сигналы определяют новое состояние триггера и присутствуют в любых триггерах. По типу информационных сигналов осуществляется классификация триггеров: D, T, RS, JK, RST, DV и т.д.

Синхросигнал не является обязательным и вводится в триггерах с целью фиксации момента перехода триггера в новое состояние, задаваемое информационными входами. Обычно, при синтезе ЦА используются триггеры с синхровходом, поэтому в дальнейшем будем рассматривать только такие триггеры.

На синхровход триггера поступают тактирующие импульсы задающего генератора, синхронизирующего работу ЦА. Период следования импульсов соответствует одному такту автоматного времени ЦА.

Рассмотрим основные типы триггеров, используемые для синтеза ЦА: D, T, RS, JK.

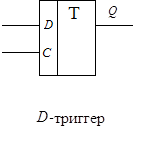

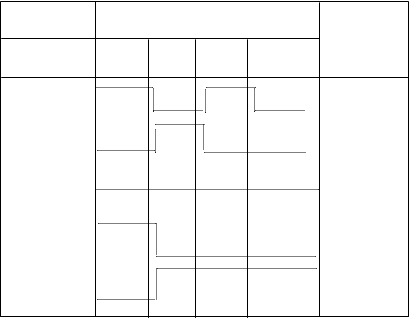

D-триггер – элемент задержки – имеет один информационный вход D и один выход Q и осуществляет задержку поступившего на его вход сигнала на один такт.

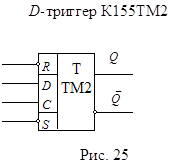

Условное обозначение и таблица переходов D-триггера представлена на рис. .

|

|

|

D |

Q t |

Q t+1 |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Из приведенной таблицы переходов для данного триггера Qt+1 = f(Qt,Dt) можно получить таблицу функций его входов Dt = j(Qt, Qt+1).

|

Q t |

Q t+1 |

D t |

||

| 0 | 0 | 0 | ||

| 0 | 1 | 1 | ||

|

|

0 | 0 | ||

| 1 | 1 | 1 |

Как видно из таблицы, состояние, в которое переходит триггер (средний столбец), совпадает с поступившим на его вход сигналом D(t) (правый столбец). В связи с этим таблица функций возбуждения памяти синтезируемого автомата с использованием D-триггеров будет полностью совпадать с кодированной таблицей переходов этого автомата. Промышленность выпускает D-триггера в интегральном исполнении. Например,

|

|

K155TM2

(рис. 25).Таких триггеров два в одном корпусе. Вход С –вход синхронизации, Q,`Q – выходы, Q – прямой, ![]() – инверсный. R, S – входы установки

в 0 и 1 соответственно. При подаче на вход R и S логического нуля

триггер устанавливается в соответствующие состояния независимо от сигнала на

входах D и C.

– инверсный. R, S – входы установки

в 0 и 1 соответственно. При подаче на вход R и S логического нуля

триггер устанавливается в соответствующие состояния независимо от сигнала на

входах D и C.

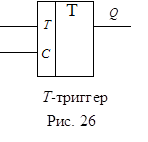

T-триггер – триггер со счетным входом – имеет один информационный вход Т и один выход Q и осуществляет суммирование по модулю два значений сигнала T и состояния Q в заданный момент времени.

Условное обозначение и таблица переходов T-триггера представлена на рис 26.

|

|

|

T |

Q t |

Q t+1 |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

|

Таблица функций входов триггера Tt = f(Qt, Qt+1) представлена в таблице.

|

Q t |

Q t+1 |

T t |

||

| 0 | 0 | 0 | ||

| 0 | 1 | 1 | ||

|

|

0 | 1 | ||

| 1 | 1 | 0 |

На основании этой таблицы можно получать функцию возбуждения элементов памяти при синтезе автомата на базе T-триггера. Например, если автомат перешел из состояния ai = 010 в состояние aj = 110, то для обеспечения этого перехода функции возбуждения должны быть:

для первого триггера при переходе из 0 в 1 T1 = 1,

для второго триггера при переходе из 1 в 1 T2 = 0,

для третьего триггера при переходе из 0 в 0 T3 =0 и т.д.

В чистом виде промышленность не выпускает T-триггера.

RS-триггер – триггер с раздельными входами.

Данный триггер имеет два входных канала R и S и один выходной Q. Вход S (set) называется входом установки в единицу, вход R (reset) – входом установки в нуль. Условное обозначение и таблица переходов RS-триггера представлена на рис. 27.

В таблице переходов при подаче комбинации S = R = 1 состояние перехода Qt+1 не определено и эта комбинация сигналов является запрещенной для RS-триггера.

Таблицу переходов можно более компактно изобразить в виде (см. табл. 21б) Анализируя табл.21 б,в отмечаем что, например, переход триггера из 0 в 0требует подачи комбинации R=0, S=0 или R=1,S=0, т.е. можно сказать что этот переход будет при R=X (безразличное состояние) , S=0.

Аналогично рассуждая по отношению к другим переходам получим следующую таблицу функций входов.

|

R |

S |

Q t |

Q t+1 |

|

|

R |

S |

Q t+1 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| 0 | 0 | 1 | 1 | 0 | 1 | 1 | ||

| 0 | 1 | 0 | 1 | 1 | 0 | 0 | ||

| 0 | 1 | 1 | 1 | 1 | 1 | – | ||

| 1 | 0 | 0 | 0 | б) | ||||

| 1 | 0 | 1 | 0 | |||||

| 1 | 1 | 0 | – | |||||

| 1 | 1 | 1 | – | а) |

|

Q t |

Q t+1 |

Rt |

S |

| 0 | 0 | X | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | X |

На основании таблицы можно получить функцию возбуждения памяти автомата при синтезе на базе RS-триггеров. Например, если автомат переходит из состояния ai= 010 в состояние aj=110, то для обеспечения такого перехода функции возбуждения должны быть:

для первого триггера при переходе из 0 в 1 R1 =0, S1 = 1;

для второго триггера при переходе из 1 в 1 R2 =0, S2 = X;

для третьего триггера при переходе из 0 в 0 R3 =X, S3= 0.

Аналогично для любого другого перехода автомата.

В чистом виде синхронный RS - триггер, используемый для синтеза ЦА, промышленностью не выпускается.

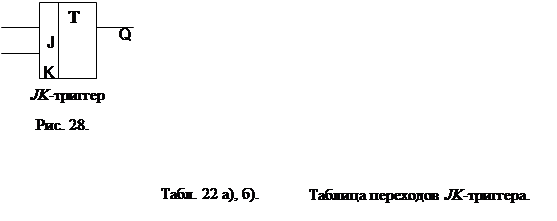

JK- триггер – имеет два информационных входа J и K и один выход Q. Вход J – вход установки в 1, вход K – вход установки в 0, т.е. эти входы аналогичны соответствующим входам RS-триггера: J – соответствует S, K – соответствует R. Однако, в отличие от RS-триггера, входная комбинация J = 1, K= 1 не является запрещённой. Условное обозначение и таблица переходов JK-триггера представлены на рис.28. и в табл. 22.

|

J |

K |

Q t |

Q t+1 |

|

|

J |

K |

Q t+1 |

| 0 | 0 | 0 | 0 | 0 | 0 |

Q t |

||

| 0 | 0 | 1 | 1 | 0 | 1 | 0 | ||

| 0 | 1 | 0 | 0 | 1 | 0 | 1 | ||

| 0 | 1 | 1 | 0 | 1 | 1 |

Q t |

||

| 1 | 0 | 0 | 1 | б) | ||||

| 1 | 0 | 1 | 1 | |||||

| 1 | 1 | 0 | 1 | |||||

| 1 | 1 | 1 | 0 | а) |

Как следует из таблиц переходов, для комбинаций входных сигналов JK = 00¸10 триггер ведет себя как RS-триггер, а при комбинации JK = 11 – как T-триггер.

Анализируя таблицу переходов ( табл. 22 а), отмечаем, что переход триггера, например, из 0 в 1 требует подачи входных сигналов J=1, K=0 или J=1, K=1, т.е. J=1, K=Х (безразличное значение). Аналогично рассуждая по отношению к другим переходам, получим следующую таблицу функций входов JK-триггера.

|

Q t |

Q t+1 |

J |

K |

| 0 | 0 | X | 0 |

| 0 | 1 | 1 | X |

| 1 | 0 | X | 1 |

| 1 | 1 | 0 | X |

|

На основании последней таблицы можно получить функцию возбуждения элементов памяти при синтезе автомата на JK-триггерах. Например, при переходе автомата из состояния ai=010 в состояние aj=110, функции возбуждения должны быть:

для первого триггера при переходе из 0 в 1 J1 = 1, K1 = X;

для второго триггера при переходе из 1 в 1 J2 = X, K2 = 0;

для третьего триггера при переходе из 0 в 0 J3 = 0, K3 = X.

Пример канонического метода структурного синтеза автомата.

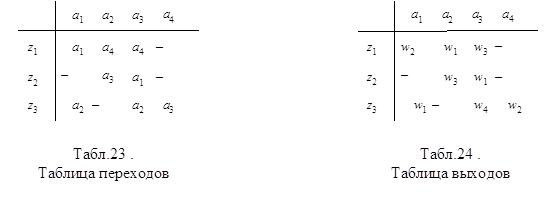

Выполним структурный синтез частичного автомата А, заданного своими таблицами переходов и выходов (табл. 23 и 24.).

|

|

Синтез будем выполнять в следующем порядке:

1. Выберем в качестве элементов памяти D-триггер, функция входов которого представлена в таблице стр. 33.

2. Закодируем входные, выходные сигналы и внутренние состояния автомата. Количество входных абстрактных сигналов F = 3, следовательно количество входных структурных сигналов L= ]log2F [ = ]log23[ = 2, т.е. х1, х2.

Количество выходных абстрактных сигналов G = 4, следовательно количество выходных структурных сигналов N =]log2G[ = ]log24[ = 2, т.е. у1, у2. Количество внутренних состояний абстрактного автомата M = 4, следовательно количество двоичных элементов памяти (триггеров) R = ] log2M [ = ]log24[ = 2.

|

|

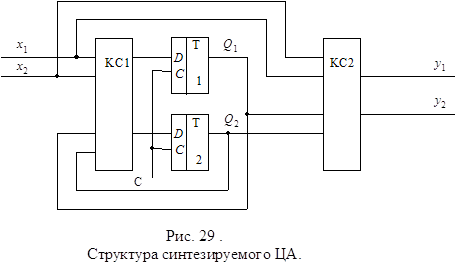

Следовательно, структура ЦА с учетом того, что исходный автомат является автоматом Мили, в качестве элементов памяти используется D-триггер, может быть представлена в виде(рис. 29):

Кодирование входных, выходных сигналов и внутренних состояний представлена в таблицах:

|

x1 |

x2 |

y1 |

y2 |

Q1 |

Q2 |

|||||||

|

z1 |

0 | 0 |

w1 |

0 | 0 |

a1 |

0 | 0 | ||||

|

z2 |

0 | 1 |

w2 |

0 | 1 |

a2 |

0 | 1 | ||||

|

z3 |

1 | 1 |

w3 |

1 | 1 |

a3 |

1 | 1 | ||||

|

w4 |

1 | 0 |

a4 |

1 | 0 |

Кодирование, в общем случае, осуществляется произвольно. Поэтому, например, каждому из сигналов Zi можно поставить в соответствие любую двухразрядную комбинацию х1, х2. Необходимо только, чтобы разные выходные сигналы Zi кодировались разными комбинациями х1, х2. Аналогично для Wi и ai.

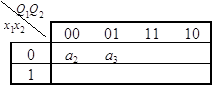

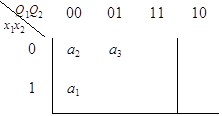

3. Получим кодированные таблицы переходов и выходов структурного автомата. Для этого в таблицах переходов и выходов исходного абстрактного автомата вместо Zi, Wi, ai cтавим соответствующие коды. Получим таблицы:

|

|

a1 |

a2 |

a3 |

a4 |

a1 |

a2 |

a3 |

a4 |

|||||

| 00 | 01 | 11 | 10 | 00 | 01 | 11 | 10 | ||||||

|

Z1 |

00 | 00 | 10 | 10 | – |

Z1 |

00 | 01 | 00 | 11 | – | ||

|

Z2 |

01 | – | 11 | 00 | – |

Z2 |

01 | – | 11 | 00 | – | ||

|

Z3 |

11 | 01 | – | 01 |

Q1Q2 |

Z3 |

11 | 00 | – | 10 |

y1y2 |

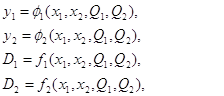

В кодированной таблице переходов заданы

функции ![]()

![]()

В кодированной таблице выходов заданны функции:

![]()

4. При каноническом методе синтез сводится к получению функций:

и последующем построении комбинационных схем, реализующих данную систему булевых функций.

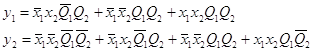

Функции у1 и у2 могут быть непосредственно получены из таблицы выходов, например, в виде :

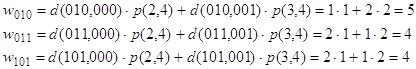

Однако выражения для у1 и у2 можно существенно упростить в результате минимизации, например, с помощью карт Карно:

| 00 | 01 | 11 | 10 | 00 | 01 | 11 |

|

||||

|

|

00 | 0 | 0 | 1 | – | 00 | 1 | 0 | 1 | – | |

| 01 | – | 1 | 0 | – | 01 | – | 1 | 0 | – | ||

|

|

11 | 0 | – | 1 | 0 | 11 | 0 | – | 0 | 1 | |

|

|

10 | – | – | – | – | 10 | – | – | – |

|

В результате минимизации имеем:

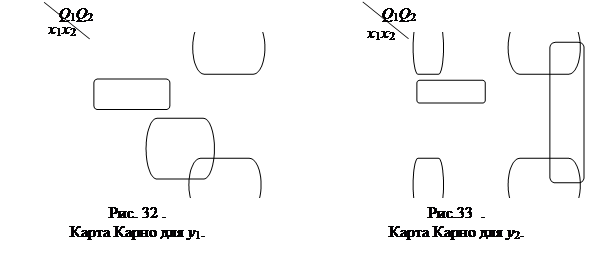

Для получения выражений для D1 и D2 необходимо получить таблицы функций возбуждения. Для чего в общем случае необходимо воспользоваться таблицей переходов и функциями входов элементов памяти. Зная код исходного состояния автомата и код

состояния перехода на основании таблицы входов триггера получаем требуемое значение функции возбуждения, обеспечивающее заданный переход. Однако для D-триггеров, как отмечалось ранее, таблица переходов совпадает с таблицей функции возбуждения. Тогда либо непосредственно из этой таблицы, либо в результате минимизации получаем требуемые значения Di. Обычно используется минимизация с помощью карт Карно:

|

|

00 | 01 | 11 | 10 | 00 | 01 | 11 | 10 | |||

|

|

00 | 0 | 1 | 1 | – | 00 | 0 | 0 | 0 | – | |

| 01 | – | 1 | 0 | – | 01 | – | 1 | 0 | – | ||

|

|

11 | 0 | – | 0 | 1 | 11 | 1 | – | 1 | 1 | |

|

|

10 | – | – | – | – | 10 | – | – | – | – |

В результате минимизации получаем:

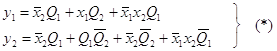

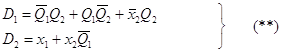

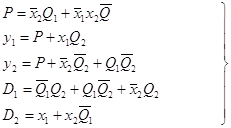

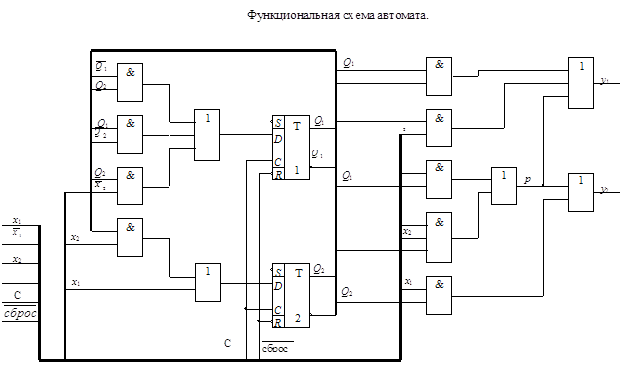

5. На основании полученных в результате синтеза булевых выражений ((*), (**)) ,строим функциональную схему автомата. Для этого уравнения ((*), (**)) представим в виде:

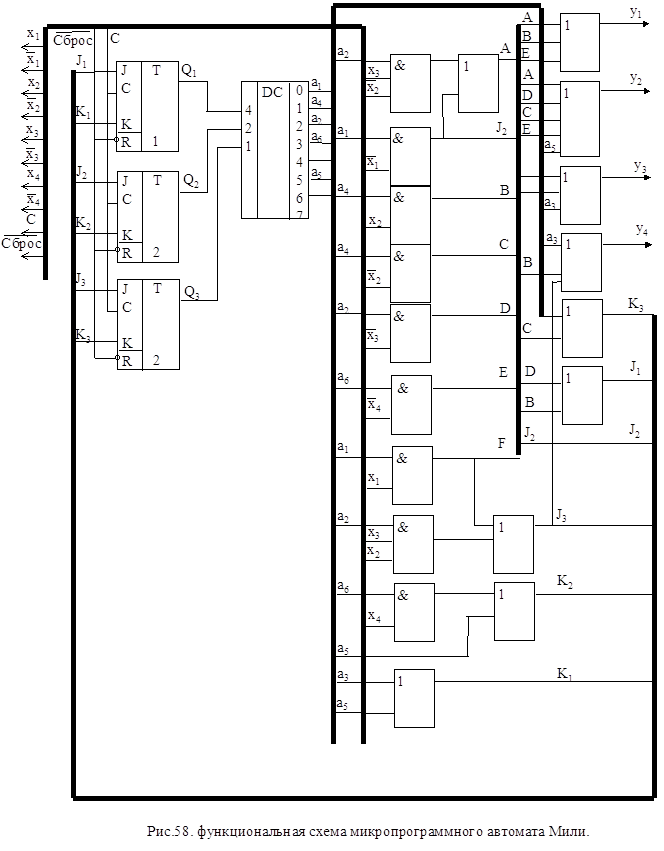

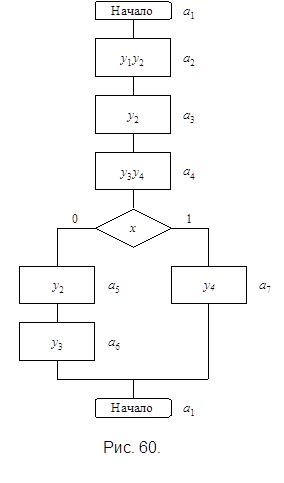

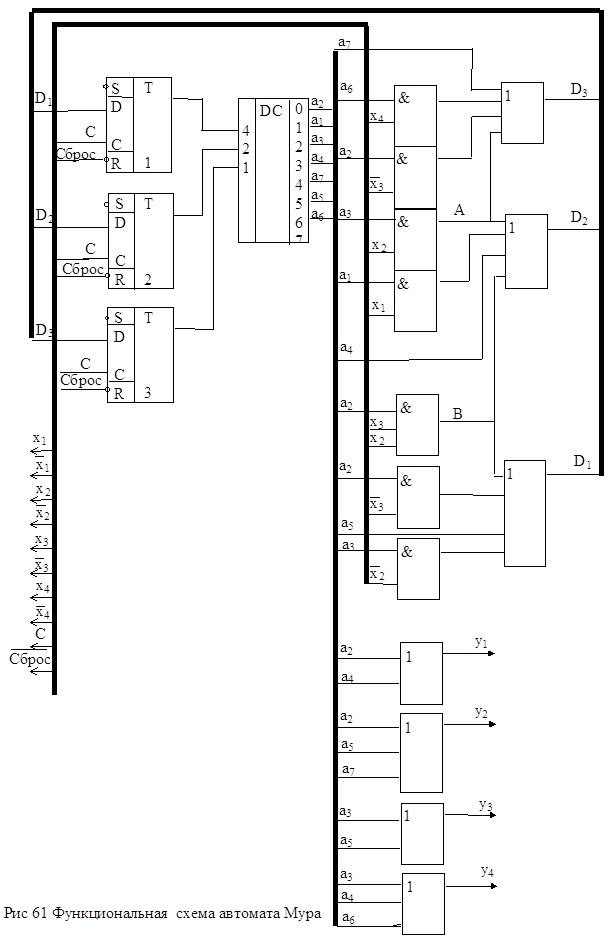

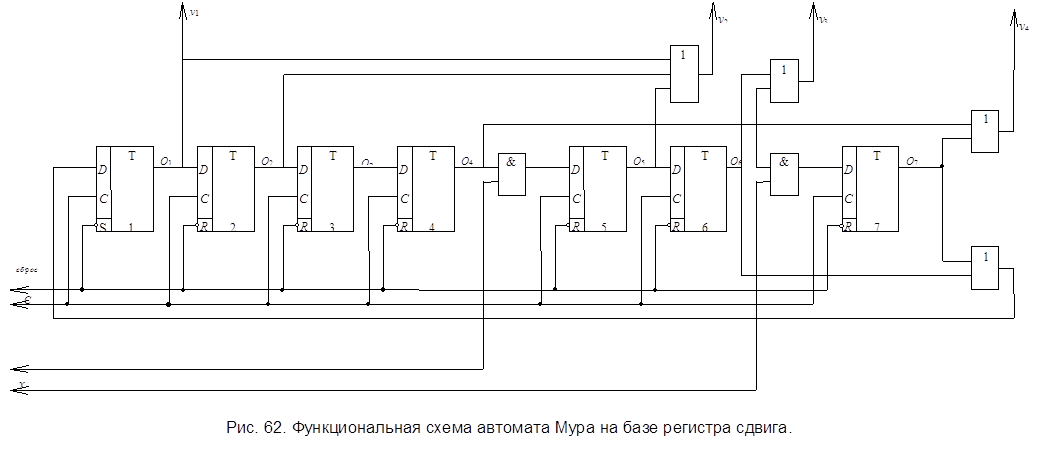

Функциональная схема автомата представлена на странице 41:

Дополнительно на функциональной схеме

показан сигнал ![]() , устанавливающий автомат в начальное

состояние (в данном случае 00).

, устанавливающий автомат в начальное

состояние (в данном случае 00).

Особенности синтеза автоматов на базе T, RS, JK триггеров.

Необходимо отметить, что синтез на базе указанных типов триггеров осуществляется аналогично выполненному синтезу на базе D-триггеров. В частности, п. 1¸3 (см. предыдущий параграф) абсолютно аналогичны. Кроме того, как следует из п.4 (см. предыдущий параграф) выходные сигналы не зависят от типа триггеров, поэтому выражение для yi будут одинаковыми для любого типа триггеров. Однако функции возбуждения будут различны для разных типов триггеров и получаются на основании таблицы переходов исходного автомата и функции входов выбранного триггера. Без особых пояснений ниже приведены таблицы функций входов, функций возбуждений и карты Карно для минимизации функций возбуждения при использовании для синтеза автомата предыдущего параграфа T-, RS-, JK-триггеров.

T-триггер.

|

Q t |

Q t+1 |

T t |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

00 |

01 | 11 | 10 | |

| 00 | 00 | 11 | 01 | – |

| 01 | – | 10 | 11 | – |

| 11 | 01 | – | 10 | 01 |

| 00 | 01 | 11 | 10 | 00 | 01 | 11 | 10 | ||||

|

|

00 | 0 | 1 | 0 | – | 00 | 0 | 1 | 1 | – | |

| 01 | – | 1 | 1 | – | 01 | – | 0 | 1 | – | ||

|

|

11 | 0 | – | 1 | 0 | 11 | 1 | – | 0 | 1 | |

|

|

10 | – | – | – | – | 10 | – | – | – | 0 |

RS-триггер.

|

Q t |

Q t+1 |

R |

S |

| 0 | 0 | X | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | X |

| 00 | 01 | 11 | 10 | |||||||||||||

|

|

R1 |

S1 |

R2 |

S2 |

R1 |

S1 |

R2 |

S2 |

R1 |

S1 |

R2 |

S2 |

R1 |

S1 |

R2 |

S2 |

| 00 | X | 0 | X | 0 | 0 | 1 | 1 | 0 | 0 | X | 1 | 0 | – | – | ||

| 01 | – | – | 0 | 1 | 0 | X | 1 | 0 | 1 | 0 | – | – | ||||

| 11 | X | 0 | 0 | 1 | – | – | 1 | 0 | 0 | X | 0 | X | 0 | 1 |

|

|

00 | 01 | 11 | 10 | 00 | 01 | 11 | 10 | |||

|

|

00 | X | 0 | 0 | – | 00 | 0 | 1 | X | – | |

| 01 | – | 0 | 1 | – | 01 | – | 1 | 0 | – | ||

|

|

11 | X | – | 1 | 0 | 11 | 0 | – | 0 | X | |

|

|

10 | – | – | – | – | 10 | – | – | – | – |

| 00 | 01 | 11 | 10 | 00 | 01 | 11 | 10 | ||||

|

|

00 | X | 1 | 1 | – | 00 | 0 | 0 | 0 | – | |

| 01 | – | 0 | 1 | – | 01 | – | X | 0 | – | ||

|

|

11 | 0 | – | 0 | 0 | 11 | 1 | – | X | 1 | |

|

|

10 | – | – | – | – | 10 | – | – | – | – |

JK-триггер.

|

Q t |

Q t+1 |

J |

K |

| 0 | 0 | 0 | X |

| 0 | 1 | 1 | X |

| 1 | 0 | X | 1 |

| 1 | 1 | X | 0 |

| 00 | 01 | 11 | 10 | |||||||||||||

|

|

J1 |

K1 |

J2 |

K2 |

J1 |

K1 |

J2 |

K2 |

J1 |

K1 |

J2 |

K2 |

J1 |

K1 |

J2 |

K2 |

| 00 | 0 | X | 0 | X | 1 | X | X | 1 | X | 0 | X | 1 | – | – | ||

| 01 | – | – | 1 | X | X | 0 | X | 1 | X | 1 | – | – | ||||

| 11 | 0 | X | 1 | X | – | – | X | 1 | X | 0 | X | 0 | 1 | X |

| 00 | 01 | 11 | 10 | 00 | 01 | 11 | 10 | ||||

|

|

00 | 0 | 1 | X | – | 00 | X | X | 0 | – | |

| 01 | – | 1 | X | – | 01 | – | X | 1 | – | ||

|

|

11 | 0 | – | X | X | 11 | X | – | 1 | 0 | |

|

|

10 | – | – | – | – | 10 | – | – | – | – |

| 00 | 01 | 11 | 10 | 00 | 01 | 11 | 10 | ||||

|

|

00 | 0 | X | X | – | 00 | X | 1 | 1 | – | |

| 01 | – | X | X | – | 01 | – | 0 | 1 | – | ||

|

|

11 | X | – | 1 | 0 | 11 | 0 | – | 0 | X | |

|

|

10 | – | – | – | – | 10 | – | – | – | – |

Функциональные схемы автоматов с различными типами триггеров предлагается построить самостоятельно.

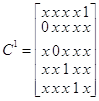

Кодирование внутренних состояний ЦА.

Гонки в автомате.

Кодирование заключается в

сопоставлении каждому состоянию автомата набора (кода) состояний элементов

памяти. При этом наборы для всех состояний должны иметь одинаковую

длину, а разным состояниям автомата должны соответствовать разные наборы. Если

элементы памяти двоичные, то их число ![]() .

.

![]() Переход автомата из

одного состояния в другое осуществляется за счет изменения состояний элементов

памяти. Если автомат переходит из состояния с кодом 010 в состояние с кодом

100, то это означает, что триггер V1 переходит из состояния 0

в состояние 1, V2 – из 1 в 0, V3 –

сохраняет свое состояние.

Переход автомата из

одного состояния в другое осуществляется за счет изменения состояний элементов

памяти. Если автомат переходит из состояния с кодом 010 в состояние с кодом

100, то это означает, что триггер V1 переходит из состояния 0

в состояние 1, V2 – из 1 в 0, V3 –

сохраняет свое состояние.

![]() При функционировании

автомата могут появиться так называемые состязания. Это явление возникает

вследствие того, что элементы памяти имеют различные, хотя и достаточно

близкие, времена срабатывания. Различны также задержки сигналов возбуждения,

поступающих на входные каналы элементарных автоматов по логическим цепям неодинаковой

длины.

При функционировании

автомата могут появиться так называемые состязания. Это явление возникает

вследствие того, что элементы памяти имеют различные, хотя и достаточно

близкие, времена срабатывания. Различны также задержки сигналов возбуждения,

поступающих на входные каналы элементарных автоматов по логическим цепям неодинаковой

длины.

|

|

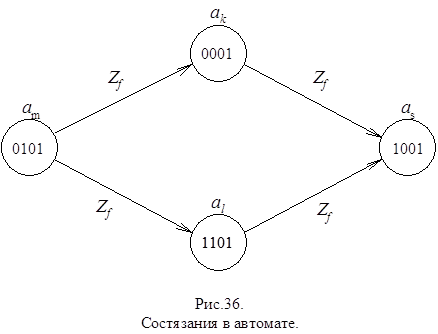

Если при переходе автомата из одного состояния в другое должны изменить свои состояния сразу несколько запоминающих элементов, то между ними начинаются состязания. Тот элемент, который выиграет эти состязания, т.е. изменит свое состояние ранее, чем другие элементы, может через цепь обратной связи изменить сигналы на входах некоторых запоминающих элементов до того, как другие, участвующие в состязаниях элементы, изменят свои состояния. Это может привести к переходу автомата в состояние, не предусмотренное его графом. Поэтому в процессе перехода из состояния am в состояние as под действием входного сигнала Zf автомат может оказаться в состоянии ak или al: (рис.36.).

Если затем при том же входном сигнале Zf автомат из аk и аl перейдет в аs, то такие состязания являются допустимыми или некритическими.

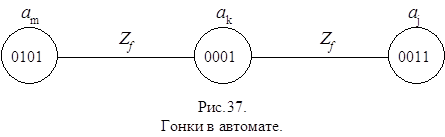

Если же в этом автомате есть переход, например, из аk в аj ¹ аs под действием того же сигнала Zf, то автомат может перейти в аj, а не в аs и правильность его работы будет нарушена (рис.37.).

|

|

Такие состязания называются критическими состязаниями или гонками и необходимо принимать меры для их устранения.