Реферат: Анализатор телефонных каналов

Омский государственный университет путей сообщений

Реферат на тему

Анализатор телефонных каналов

Омск 2001г.

Назначение и основные параметры анализатора телефонных каналов.............. 3

Затухание эхо-сигнала................................................................................................................................................................ 3

Нелинейные искажения............................................................................................................................................................... 3

Относительная амплитудно-частотная характеристика затухания.............................................................................. 3

Относительная характеристика группового времени прохождения.............................................................................. 3

Затухание продуктов паразитной модуляции сигнала..................................................................................................... 3

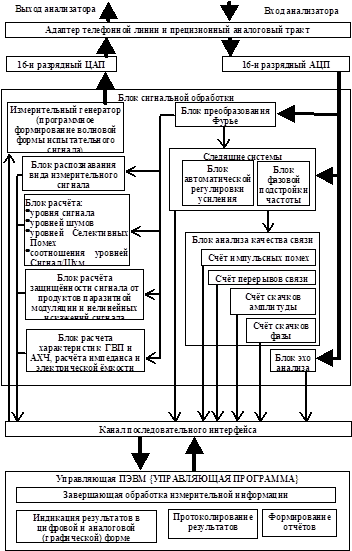

Структурная схема анализатора............................................................................................................................................. 4

Описание Процессора ADSP-21msp58................................................................................. 6

Системный интерфейс и интерфейс памяти........................................................................................................................... 7

Система команд............................................................................................................................................................................. 7

Эффективность сигнального процессора............................................................................................................................... 7

Вычислительные модули........................................................................................................................................................... 7

структурная схема процессора семейства ADSP-2100...................................................................................................... 7

Генераторы адресов данных и программа sequencer......................................................................................................... 8

Шины................................................................................................................................................................................................ 9

Внутренние переферийные устройства................................................................................................................................ 9

Последовательные порты........................................................................................................................................................... 9

Таймер............................................................................................................................................................................................ 10

Главный интерфейсный порт (HIP)....................................................................................................................................... 10

Аналоговый интерфейс............................................................................................................................................................. 10

Литература.................................................................................................................................... 11

Назначение и основные параметры анализатора телефонных каналов.

Анализатор телефонных каналов предназначен для проведения измерений параметров каналов тональной частоты (ТЧ) первичных сетей связи, ведомственных телефонных сетей и коммутируемой телефонной сети общего пользования (ТфОП). Анализатор должен обеспечиваеть создание нормированных электрических испытательных сигналов для тестирования каналов связи, а также позволяеть определить количественные показатели состояния связи для тестируемых каналов в автоматическом и автоматизированном режимах.

Обработка, накопление, выдача и представление измерительной информации может обеспечивается внешним универсальным управляющим компьютером и специализированной управляющей компьютерной программой.

Каналы тональной частоты характеризуют следющие основные параметры

Затухание эхо-сигнала

Измерение затухания уровня эхо-сигнала относительно уровня передаваемого сигнала производится в диапазоне от 10 до 60 дБ

Нелинейные искажения

производятся измерения коэффициентов 2‑й и 3‑й гармоник для гармонического испытательного сигнала с частотой 1020 Гц и коэффициентов продуктов нелинейных искажений 2‑го и 3‑го порядков для четырехчастотного испытательного O.42‑сигнала

Относительная амплитудно-частотная характеристика затухания

Измерение относительной АЧХ производится в диапазоне от 100 до 3700 Гц при неравномерности относительной АЧХ не более 35 дБ и номинальном уровне мощности испытательного сигнала на входе анализатора -6 дБм.

Относительная характеристика группового времени прохождения

измерение относительной частотной характеристики группового времени прохождения (ГВП) при номинальном уровне мощности испытательного сигнала на входе измерителя ‑6 дБм в диапазонах:

по интервалу частот ГВП и опорной частоте - от 300 до 3400 Гц;

Затухание продуктов паразитной модуляции сигнала

измерение затухания продуктов паразитной модуляции испытательного сигнала с частотой 1020 Гц токами питания частотой 50 Гц и гармониками относительно уровня испытательного сигнала в линии связи.

Структурная схема анализатора.

Анализатор объединяет в себе измерительно-анализирующее устройство и генератор нормированных электрических испытательных воздействий. По характеру представления измерительной информации анализатор является регистрирующим измерительным прибором и показывающим измерительным прибором с представлением на экране компьютерного дисплея измерительной информации в цифровой и аналоговой (графической) форме.

Основными составными частями анализатора являются генераторный и измерительно‑анализирующий блоки.

Генераторный блок при анализе каналов связи задает волновую форму сигнала программным путем и обеспечивает следующие режимы генерации:

· режим генерации постоянного по частоте гармонического сигнала с постоянным или изменяющимся по линейному закону уровнем мощности - для измерений амплитудных характеристик канала связи, затухания сигнала, отношения уровней сигнала и шума (Сигнал/Шум), в том числе по Рекомендации МСЭ‑Т О.132, коэффициентов нелинейных искажений, измерения частоты и изменения частоты в канале связи, дрожания фазы, дрожания амплитуды, затухания продуктов паразитной модуляции, подсчета числа перерывов связи, подсчета числа импульсных помех, подсчета числа скачков фазы и подсчета числа скачков амплитуды;

· режим генерации гармонического сигнала с изменяющейся по линейному закону частотой - для почастотного измерения АЧХ;

· режим генерации многочастотного сигнала - МЧС‑генератор - для измерений относительного группового времени прохождения (ГВП), относительной амплитудно-частотной характеристики (АЧХ) и импеданса канала связи;

· режим генерации псевдослучайного сигнала для измерений соотношения уровней Сигнал/Шум (шумы квантования)

· режим генерации четырехчастотного сигнала для измерений нелинейных искажений

· режим генерации радиоимпульсов для измерения эхо-сигнала;

· режим генерации двухчастотного сигнала измерительной и эталонной частот для определения амплитудно‑частотной характеристики и частотной характеристики группового времени прохождения.

В каждом режиме генерации номинальные уровни мощности испытательных сигналов и номинальные значения частот гармонических испытательных сигналов задаются дискретно.

Измерительно-анализирующий блок обеспечивает мониторинг (измерение и протоколирование) тестируемых каналов связи с использованием собственного или внешнего генератора испытательных сигналов. При этом в зависимости от автоматически определяемого вида входного сигнала анализатор автоматически включает измерение тех параметров, для измерения которых и предназначен соответствующий измерительный сигнал.

Измерительно-анализирующий блок как средство измерений с нормированными метрологическими характеристиками проводит определение следующих параметров и характеристик:

· уровня мощности сигнала;

· частоты гармонического сигнала;

· уровня не взвешенного шума;

· уровня псофометрического шума;

· отношения уровней мощности псевдослучайного сигнала и не взвешенного шума;

· соотношения уровней гармонического сигнала и псофометрически взвешенного шума, а также соотношения уровней гармонического сигнала и не взвешенного шума;

· дрожания фазы гармонического сигнала;

· дрожания амплитуды гармонического сигнала;

· частотных характеристик ГВП и АЧХ;

· уровня селективных помех, в том числе псофометрических;

· продуктов нелинейных искажений 2‑го и 3‑го порядков для четырехчастотного сигнала;

· коэффициентов гармоник для гармонического сигнала;

· затухания продуктов паразитной модуляции сигнала;

· затухания эхо-сигнала;

· модуля полного сопротивления линии связи (в диапазоне от 300 до 3400 Гц);

· электрической емкости линии связи;

· изменения частот 1020 Гц и 2000 Гц в канале связи путем измерения отклонения частоты гармонического сигнала от значений 1020 и 2000 Гц.

Измерительно-анализирующий блок как средство определения количественных показателей состояния связи обеспечивает подсчет на заданном интервале времени фактов превышения устанавливаемых пороговых значений. Анализатор осуществляет счет:

· импульсных помех,

· перерывов связи,

· скачков амплитуды и

· скачков фазы.

С ненормируемыми метрологическими характеристиками производится тестирование каналов связи по параметрам, приведенным ниже:

· соотношение Сигнал/Шум по сигналу МЧС-генератора;

· соотношение Сигнал/Шум по сигналу О.42-генератора;

· уровень поступающего на вход многочастотного, псевдослучайного, или четырехчастотного сигнала;

· индуктивность линии связи;

· среднеквадратическое отклонение уровня гармонического испытательного сигнала в линии связи (СКО уровня) от среднего значения;

· максимальный из зафиксированных на интервале 1 с скачок фазы гармонического сигнала;

· максимальный из зафиксированных на интервале 1 с скачок амплитуды гармонического сигнала;

· максимальная на интервале 1 с мгновенная мощность измеряемого сигнала;

· минимальная на интервале 1 с мгновенная мощность гармонического сигнала;

· относительное время действия импульсных помех;

· процентная доля секундных интервалов с импульсными помехами на измерительном интервале;

· процентная доля секундных интервалов с перерывами связи на измерительном интервале;

· процентная доля секундных интервалов с импульсными помехами и перерывами связи на временном измерительном интервале;

· относительное время действия перерывов связи;

· относительное время действия импульсных помех и перерывов связи;

· построение эхограммы - зависимости затухания от задержки эхо‑сигнала.

Основную функциональную нагрузку в анализаторе выполняет Процессор ADSP-21msp58. На этом процессоре реализуются функции 16 разрядного ЦАП-АЦП, блока сигнальной обработки и последовательно интерфейса.

Описание Процессора ADSP-21msp58.

Процессор ADSP-21msp58 представляет собой совокупность программируемых микропроцессоров с общей структурой, оптимизированную для обработки аналогового сигнала в цифровой форме, а так же для других прикладных целей. Кроме того, процессор включают аналоговый интерфейс для преобразования сигнала звуковой частоты.

Архитектура семейства ADSP-2100 приспособлена к выполнению задач с помощью цифрового сигнального процессора и построена таким образом, что устройства за один такт могут выполнять следующие действия:

· генерировать следующий адрес программы;

· выбирать следующую команду;

· выполнять один или два шага программы;

· модифицировать один или два указателя адреса данных;

· выполнять вычисление.

В этом же такте процессоры, которые имеют релевантные модули могут:

· принимать и/или передавать данные через последовательный порт;

· принимать и/или передавать данные через главный порт интерфейса;

· принимать и/или передавать данные через DMA порты;

· принимать и/или передавать данные через аналоговый интерфейс.

Системный интерфейс и интерфейс памяти

В каждом процессоре семейства ADSP-2100 четыре внутренних шины соединяют внутреннюю память с другими функциональными модулями:

- шина адреса;

- шина данных;

- шина памяти программ;

- шина памяти данных.

Внешние устройства могут получать контроль над шинами посредством сигналов предоставления (BR,BG). Процессоры ADSP-2100 могут работать в то время когда шины предоставлены другому устройству, пока не требуется операции с внешней памятью.

Схема начальной загрузки дает возможность автоматической загрузки внутренней памяти после того как ее содержимое было стерто. Это можно осуществлять с помощью интерфейса памяти из EPROM, из главного компьютера, посредством главного порта интерфейса. Программы могут загружаться без применения каких-либо дополнительных аппаратных средств.

Система команд

Процессоры семейства ADSP-2100 используют единую систему команд для совместимости с устройствами с более высокой интеграцией. Система команд позволяет выполнять мультифункциональные команды за один такт процессора, с другой стороны каждая команда может быть выполнена отдельно в своем такте. Ассемблер имеет алгебраический синтаксис, для повышения удобочитаемости легкости кодирования.

Эффективность сигнального процессора

Сигнальный процессор должен быть не только очень быстродействующим, но удовлетворять некоторым требованиям в следующих областях:

· Быстрая и гибкая арифметика – архитектура процессоров ADSP позволяет производить такие операции, как умножение, умножение с накоплением, произвольное смещение, а так же ряд стандартных арифметических и логических операций в одном цикле процессора.

· Расширенный динамический диапазон – 40-разрядный аккумулятор имеет восемь резервных бит защиты от переполнения при последовательном суммировании, которые гарантируют, что потери данных быть не может.

· Выборка двух операндов за один цикл – при расширенном суммировании на каждом цикле процессора необходимо два операнда

· Аппаратные циклические буферы – большой класс алгоритмов обработки цифро-аналоговых сигналов, включая цифровые фильтры требуют наличия циклических буферов.

Переход по нулю – повторяющиеся алгоритмы наиболее логично выражать через циклы. Программа Sequenser ADSP-2100 поддерживает работу с циклическим кодом с нулем на верху, в объединении со структурой clearest это повышает эффективность системы. Также нет препятствий для работы с условными переходами.

Вычислительные модули

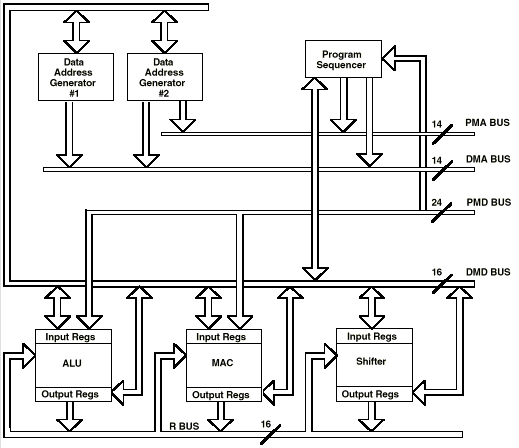

структурная схема процессора семейства ADSP-2100

|

Как уже говорилось выше каждый процессор содержит три независимых вычислительных модуля:

- арифметико-логический (ALU);

- умножение с накоплением (MAC);

- расширитель (shiffter).

Эти устройства работают с 16-разрядными данными и обеспечивают аппаратную поддержку мультиточности.

ALU выполняет ряд стандартных арифметических и логических команд в дополнение к примитивам деления. MAC выполняет одно-цикловые операции умножения, умножения/сложения, умножения/вычитания. Shiffter осуществляет логические и арифметические сдвиги, нормализацию, де нормализацию и операцию получения порядка, атак же управление форматом данных, разрешая работу с плавающей точкой. Вычислительные модули размещаются последовательно друг за другом, таким образом чтобы выход одного мог стать входом другого в следующем цикле. Результаты работы модулей собираются на 16-разрядную R-шину.

Все три модуля содержат входные и выходные регистры, которые доступны через 16-разрядную DMD-шину. Команда, выполняемые в модулях, берут в качестве операндов данные находящиеся в регистрах ввода и после выполнения записывают результат в регистры вывода. Регистры являются как бы промежуточным хранилищем между памятью и вычислительной схемой. R-шина позволяет результату одного вычисления стать операндом к другой операции. Это позволяет сэкономить время обходясь без лишних пересылок модуль-память.

Генераторы адресов данных и программа sequencer

Два специализированных генератора адресов данных (DAGs) и мощная программа sequencer гарантируют эффективное использование вычислительных модулей. DAGs обеспечивают адреса памяти, когда необходимо поместить данные из памяти в регистры ввода вычислительных модулей, либо сохранить в результат из выхоных регистров. Каждый DAG отвечает за четыре указателя адреса. Если указатель используется для косвенной адресации то измениятся значение некоторого регистра. С двумя генераторами процессор может выдавать два адреса одновременно для выборки из памяти двух операндов.

Для автоматической адресации модуля круговых буферов значение длины операнда может быть связано с каждым указателем. (Круговая буферная особенность также используется последовательными портами для автоматической передачи данных).

DAG1 обеспечивает адреса только для данных, DAG2 – для данных и программ. Когда в регистре состояния (MSTAT) установлен соответствующий бит режима, адрес вывода DAG1 прежде чем попасть на шину адреса инвертируется. Эта особенность облегчает работу в двоичной системе.

Программа Sequenсer обеспечивает последовательность команд и адресацию памяти программы. Sequencer управляется регистром команд, который указывает на команду, которая в данный момент выполняется. Выбранные команды записываются в регистр команд за один такт процессора и выполняются в течении следующего. Чтобы уменьшить количество циклов, sequencer поддерживает работу с условными переходами.

Шины

Процессоры семейства имеют пять внутренних шин. Шины адреса программы (PMA) и адреса данных (DMA) связаны с адресами памяти данных и программы. Шина данных программы (PMD) и шина данных (DMD) используются для передачи информации связанной с областями памяти. Шины мультиплексированы в одну внешнюю шину адреса и одну внешнюю шину данных. R-шина предназначена для передачи промежуточных результатов непосредственно между вычислительными модулями.

Адресная шина PMA шириной 14 бит обеспечивает достум к 16Кбайтам смешанной системы команд и данных. 24-разрядная шина PMD предназначена для работы с 24-битными командами.

Адресная шина DMA шириной 14 бит, обеспечивает прямой доступ к 16Кбайтам области данных. 16-разрядная шина DMD предназначена для внутренних пересылок между любыми регистрами процессора и регистров с памятью в одиночном цикле. Адрес памяти данных исходит из двух источников: абсолютное значение, определенное в системе команд (прямая адресация) или вывод данных адресует генератор (косвенная адресация). Воспользоваться данными из области команд можно лишь с помощью косвенной адресации.

Шина данных памяти программы (PMD) предназначена для передачи данных в вычислительные модули и считывания результата вычислений через PMD-DMD модуль обмена. Этот модуль позволяет передавать данные от одной шины к другой. Он имеет аппаратные средства для перехода от 8-разрядной шины к другой.

Внутренние переферийные устройства

Этот раздел описывает дополнительные функциональные модули, которые включены в различные процессоры ADSP-2100 семейства.

Последовательные порты

Процессор имеет два последовательных двунаправленных порта. Порты – синхронные и используют кадровые сигналы для контроля за приемом-передачей данных. Каждый порт имеет внутренний генератор частоты, но в то же время может использовать внешний генератор. Сигналы синхронизации могут вырабатываться как самим портом, так и внешним устройством. Длина кадра обмена может меняться от трех до шести бит. Последовательный порт SPRT0 имеет многоканальные возможности и пзволяет обмен данными произвольной длины от 24 до 32 байт. Второй порт SPORT1 может быть сконфигурирован с помощью внешних прерываний IRQ0 и IRQ1.

Таймер

Регистр счета (16-разрядов) определяет время генерации прерываний, прерывание вырабатывается когда значение регистра равно нулю.

Главный интерфейсный порт (HIP)

Главный интерфейсный порт – параллельный порт ввода-вывода осуществляет прямое соединение с процессором. Через него производится обмен между ADSP и памятью главной ЭВМ. HIP состоит из регистров, через которые ADSP-2100 и главный процессор обмениваются информацией о состоянии и данными. HIP может быть сконфигурирован следующим образом:

- 8-разрядная или 16-разрядная шина;

- мультиплексная шина данных/шина адреса или отдельно шина данных и шина адреса;

- чтение стробирующих сигналов READ/WRITE.

Аналоговый интерфейс

Входной аналоговый интерфейс состоит из входных усилителей и 16-разрядного аналогоцифрового преобразователя (ADC). Аналогично на выходе находится цифроаналоговый преобразователь и выходной дифференциальный усилитель.

Литература.

| Методы позиционирования и сжатия звука | |

|

Современные звуковые карты. Аннотация В данной курсовой работе изучаются различные аспекты применения звуковых карт. Рассматриваются способы получения ... Это приводит к ограничению динамического диапазона, который в идеале (без учета гармонических искажений) был бы равен соотношению сигнал/шум, однако необходимость ограничения этих ... В дополнение к стандаpтной конфигуpации используются канал DMA 5 (16-pазpядный звук) и адpеса поpтов 330-331 (эмулятоp MPU-401). |

Раздел: Рефераты по информатике, программированию Тип: дипломная работа |

| Техническая диагностика средств вычислительной техники | |

|

ГОУ СПО Астраханский колледж вычислительной техники М.В. Васильев преподаватель специальных дисциплин Астраханского колледжа вычислительной техники ... 3. 24-битовая шина расширения адреса Peripherial Bus XA[23/00] формируется буферами адреса 82A303, 82A304 и используется контроллером IPS 82C206 также для доступа к ROM BIOS, а ... Анализатор позволяет осуществлять останов по обращению к любому адресу памяти или порта, устанавливать пошаговый режим работы и индицировать состояние адресной шины, шины данных и ... |

Раздел: Рефераты по информатике, программированию Тип: учебное пособие |

| Проектирование магистральной волоконно-оптической системы передачи с ... | |

|

Аннотация Дипломный проект посвящен вопросу проектирования магистральной волоконно-оптической системы передачи с повышенной пропускной способностью ... Целью экспериментальных исследований является оценка параметров спроектированного бортового приемо-передающего оптического модуля, таких как BER, зависимость скорости передачи ... Генератор последовательности обеспечивает временную синхронизацию сигнала с анализатором ошибок, который осуществляет побитовое сравнение между полученными из тестируемого приемо ... |

Раздел: Рефераты по коммуникации и связи Тип: дипломная работа |

| Ответы к Экзамену по Микропроцессорным Системам (микроконтроллеры ... | |

|

1. История В 1642 Паскаль изобрел механическую счетную машину(+ 30 лет спустя Лейбниц сделал машину , которая могла умножать, делить , плюсовать и ... Процессор, получив этот сигнал, приостанавливает выполнение очередной команды, не дожидаясь ее завершения, выдает на системный интерфейс управляющий сигнал ППДП и отключается от ... Например, в компьютерах с процессором Pentium шина процессора состоит из 64 линий данных, 32 линий адреса и соответствующих линиях управления. |

Раздел: Рефераты по информатике, программированию Тип: реферат |

| Управление звуковой картой компьютера | |

|

Введение Взаимодействие человека с ЭВМ должно быть прежде всего взаимным ( на то оно и общение ) Взаимность, в свою очередь, предуcматривает ... Сигналы, поступающие с клавиатуры, подаются в процессор (Рис.1), который направляет их либо через системную шину к центральному процессору, либо к синтезаторам звуковой карты. Программа имеет набор модулей обработки, которые могут использоваться как посредством интерфейса DirectX, так и непосредственно обрабатывать сигнал, полученный из Wave-файла или ... |

Раздел: Рефераты по информатике, программированию Тип: реферат |