Реферат: Разработка цифрового таймера

стр.

Введение ……………………………………………………………………………………………………

Гл 1. Анализ функций устройств выдержки времени ………………………

Гл 2. Разработка структурной схемы …………………………………………………..

Гл 4. Разработка принципиальной схемы

4.1) Блоки предустановки значения выдержки………………………………………….

4.2) Блоки отсчета выдержки ………………………………………….………………………..

4.3) Блоки управления………………………………………………………….…………………..

4.4) Генераторное оборудование ………………………………………………………………

Список литературы …………………………………………………………………………………

Введение

Электронные таймеры предназначены для установки интервалов времени, сигнализации и окончания отсчета, управления технологическими процессами в различных отраслях промышленности и сельского хозяйства. В данной работе был проведен анализ схемотехнических решений электронных таймеров, разработана структурная и принципиальная схемы цифрового таймера. По полученным в результате разработки схемам был построен макет устройства и проведены его испытания, подтвердившие работоспособность схемы.

Пояснительная записка включает введение, пять тематических глав, заключение и список литературы. В каждой из глав рассмотрен отдельный этап разработки.

В главе 1 - “Анализ функций устройств выдержки времени”, - рассматривается принцип действия цифровых и аналоговых устройств выдержки времени(УВВ).

В главе 2, - “Разработка структурной схемы” - по результатам анализа, была разработана структурная схема УВВ с диапазоном выдержек от 1 до 9999 условных интервалов времени.

В главе 3 - “Характеристика применяемой элементной базы”- рассмотрены основные параметры применяемых элементов.

В главе 4 – “Разработка принципиальной схемы” - для каждого блока структурной схемы был рассмотрен вариант реализации на ИМС серии К555, а также расчет конструктивных параметров печатной платы устройства.

В главе 5 – “Расчет источника питания” - приводится расчет сетевого источника питания, включающий расчет стабилизатора напряжения и сетевого трансформатора.

В заключение приводится список литературы содержащий 11 источников.

К расчетно-пояснительной записке прилагается четыре чертежа:

· “Структурная схема”

· “Принципиальная схема”

· “Печатная плата”

· “Временные диаграммы состояний индикаторов”

Анализ функций устройств выдержки времени.

Если проанализировать схемы различных вариантов устройств выдержки времени (УВВ),то можно сделать вывод, что алгоритм действия устройств во всех случаях одинаковый.

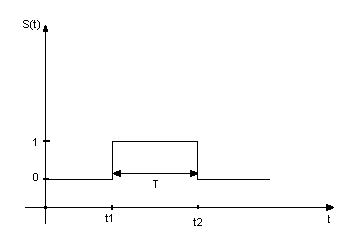

Устройство формирует на выходе функцию, представленную на рис.1. Здесь по оси абсцисс отложено время t, а по оси ординат – функция состояния устройства.

Рис.1

Если не принимать во внимание детали то любое УВВ (в том числе и механическое) можно представить в виде некоторого черного ящика имеющего один вход и один выход. На вход поступает некоторое внешнее воздействие X(t), а на выходе формируется функция S(t).

Рис.

Характер внешнего воздействия зависит от конструкции УВВ и в каждом конкретном случае может быть различным. Что касается выходной функции то она для любой конструкции УВВ имеет одну общую деталь – она принимает только два значения, причем в одном из них она может находиться только в течении строго определенного интервала времени T. Обозначим эти состояния как 0 и 1. Устройство находится в состоянии 0 (пассивное состояние) до тех пор пока на его вход не поступит какое либо внешнее воздействие X(t). После этого оно переходит в состояние 1 (активное состояние). По прошествии времени T устройство возвращается в состояние 0.

В неэлектрических УВВ работающих по такому принципу (например в механическом таймере) активное и пассивное состояния могут проявляться в различных углах поворота управляющих рычагов, воздействующих на исполнительные механизмы. В электрических УВВ функция S(t) как правило, проявляется в изменениях значений напряжения на выходе.

В промышленности первые устройства выдержки времени появились и стали применяться еще в дотранзисторную эпоху как альтернатива механическим. Их преимущества перед последними были очевидны – надежность, многофункциональность, простота и точность. Для формирования функции S(t) был выбран простой (а в то время и единственно приемлемый) принцип. Он заключался в зарядке или разрядке конденсатора определенной емкости через достаточно большое сопротивление.

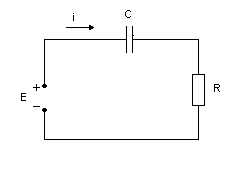

Для пояснения этого принципа рассмотрим цепь , состоящую из последовательно соединенных конденсатора и резистора (рис. ).

При подаче напряжения Е конденсатор начинает заряжаться. Напряжение на нем возрастает по экспоненциальному закону:

Uc(t)=E(1-exp(-t/pt)) (1)

где Uc(t) – напряжение на конденсаторе в момент времени t, а pt=RC – постоянная времени.

Напряжение на резисторе можно найти по формуле:

Рис. 3

Ur(t)=E-Uc(t) (2)

Как видно из формулы (1), для того чтобы напряжение на конденсаторе достигло определенного уровня Uс1 необходимо некоторое время tв, определяемое по формуле:

tв=R*C*ln(E/(E-Uc1)) (3)

Из формулы (3) видно, что tв зависит от емкости конденсатора С, сопротивления резистора R, напряжения Е и собственно от уровня Uc1. Если сделать один из этих параметров переменным, а остальные жестко стабилизировать, то можно получить устройство выдержки времени с переменным значением интервала Т, причем этот интервал будет однозначно зависеть от переменного параметра.

Чтобы получить из данной схемы практически применимое устройство, достаточно подключить параллельно конденсатору какое либо пороговое устройство с двумя устойчивыми состояниями, которое при достижении напряжением Uс значения Uс1 изменяло бы свое состояние.

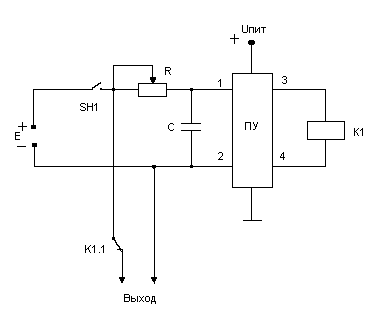

Структурная схема одного из вариантов такого УВВ

приведена на рис.

Для формирования на выходе устройства функции

S(t) с двумя

устойчивыми состояниями используется ключ SH1

и контакты реле К1.1.

Для формирования на выходе устройства функции

S(t) с двумя

устойчивыми состояниями используется ключ SH1

и контакты реле К1.1.

Рассмотрим работу схемы. В исходном состоянии конденсатор С разряжен, ключ SH1 разомкнут, напряжение на выходе равно нулю, движок резистора R устанавливается в определенное, заранее известное положение, соответствующее интервалу времени Т.

Пороговое устройство включает реле К1 в случае если напряжение на выводах 1-2 становится больше некоторого значения Uc1.

При замыкании ключа SH1 (внешнее воздействие) на выходе устройства появляется напряжение Uвых=Е. С этого момента начинает заряжаться конденсатор С – начинается формирование интервала Т. По прошествии времени Т напряжение на конденсаторе достигнет уровня Uс1 и пороговое устройство включит реле К1. Своими контактами К1.1 оно разомкнет выходную цепь и напряжение на выходе снова станет равным нулю (Uвых=0). В данном случае напряжения 0 и Е соответствуют пассивному и активному состоянию.

В качестве порогового устройства можно использовать какую либо ключевую схему. Конкретный вариант этой схемы выбирают исходя из условия получения максимально возможного входного сопротивления, чтобы исключить его влияние на процесс зарядки конденсатора. Во времена господства ламповой техники в качестве порогового устройства использовались тиратроны или газовые стабилитроны, а с развитием полупроводниковой электроники стали применять транзисторные ключи на полевых транзисторах.

Напряжение с выхода устройства можно подать на какую либо нагрузку, например на лампу фотоувеличителя.

При всей очевидной простоте такого УВВ оно имеет ряд недостатков, которые стали особенно сильно проявляться при ужесточении требований к точности задания и воспроизведения интервала Т. Как видно из схемы для задания значения Т используется способ поворота движка переменного резистора на определенный угол F. При этом погрешность установки порядка одного градуса на однооборотном переменном резисторе практически не заметна. Но в тоже время такая погрешность, особенно в высокоомных резисторах, соответствует погрешности установки сопротивления в несколько килоом. При длительных выдержках времени (порядка нескольких часов) это приведет к погрешности порядка одной минуты. К тому же очень трудно будет вновь установить эту же выдержку еще раз, если движок резистора по каким либо причинам окажется в другом положении.

Другой причиной неточности является конденсатор, параметры которого (особенно у электролитического) нестабильны во времени. Эта нестабильность может привести к тому что разница между интервалами выдержек в 1 час при первом и втором запуске УВВ составит порядка 2-3 мин (данные для электролитического конденсатора).

Наконец, изменение напряжения питания также приводит к изменению длительности выдержки.

Для снижения влияния этих причин приходилось использовать прецизионные переменные резисторы, удорожавшие в несколько раз все устройство, применять специальные средства стабилизации напряжения питания и т.п.

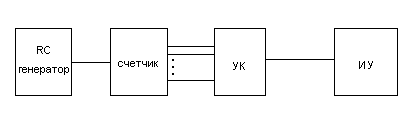

С развитием цифровой техники, и в частности с появлением быстродействующих цифровых счетчиков, появилась возможность существенно улучшить параметры УВВ путем пересмотра самого принципа работы. Согласно новому принципу построения УВВ в качестве интервала Т берется не время зарядки конденсатора а время нескольких его перезарядок. Преимущества такого УВВ очевидны – резистор можно сделать постоянным и следовательно недорогим, а в качестве конденсатора применить неэлектролитический, малой емкости. Недостаток УВВ подобной конструкции – дискретная сетка выдержек времени – легко устраняется путем снижения времени одной перезарядки до значения порядка 10е-3 с и ниже (частота перезарядок >1 КГц). В качестве устройства, которое автоматически производит перезарядку конденсатора вполне естественно использовать RC-генератор. Структурная схема такого УВВ приведена на рис.

Рис.

Импульсы с генератора, период которых соответствует времени одной перезарядки конденсатора, поступают на вход цифрового счетчика импульсов. С выхода счетчика число поступивших импульсов в двоичном коде подается на устройство контроля (УК). Как только число импульсов достигнет заданного значения, УК посылает сигнал на исполнительное устройство ИУ, которое производит какое либо действие. В реальных УВВ подобного типа устройство контроля, помимо этого может осуществлять блокировку счетчика, остановку генератора, включение сигнализации и т.п.

Еще одно преимущество подобных УВВ состоит в том, что для повышения точности выдержки времени можно вообще отказаться от использования в генераторе времязадающей RC-цепи и применить вместо нее более стабильные элементы, например кварцевые резонаторы.

Разработка структурной схемы

_______________________________________________________________

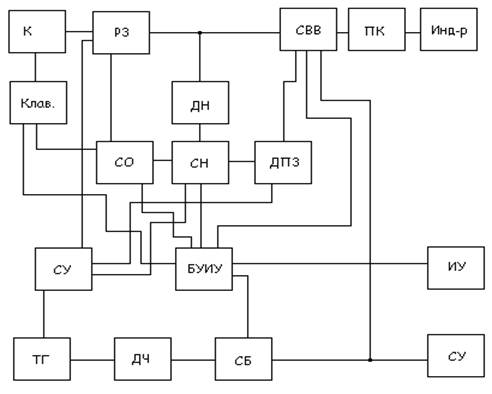

Структурная схема устройства приведена на рис.

Рис.

На схеме введены следующие обозначения:

Клав. – Клавиатура;

К – Кодер клавиатуры;

РЗ – Регистр-защелка;

СВВ – Счетчик выдержки времени;

ПК – Преобразователь кода;

Инд-р. – Семисегментный индикатор;

ДН – Детектор нажатий;

СН – Счетчик нажатий;

ДПЗ – Дешифратор позиций загрузки;

СО – Схема обнуления;

СУ – Схема управления;

БУИУ – Блок управления исполнительным устройством;

ИУ – Исполнительное устройство;

ТГ – Тактовый генератор;

ДЧ – Делитель частоты;

СБ – Схема блокировки;

СУ – Сигнальное устройство.

Рассмотрим работу устройства при начальном вводе значения выдержки. Для ввода выдержки используются клавиши 0…9 клавиатуры. При нажатии на клавишу сигнал от нее поступает на кодер клавиатуры (КК), который преобразует номер клавиши в инверсный двоичный код. С кодера клавиатуры этот номер поступает на вход регистра–защелки (РЗ). Он предназначен для фиксации номера нажатой клавиши на время, необходимое для записи в счетчик выдержки времени (СВВ), а также для исключения влияния “дребезга контактов” клавиатуры на работу устройства.

Регистр-защелка фиксирует предварительно установленные на его входах значения по команде со схемы управления (СУ). Число записей в секунду зависит от частоты тактового генератора. Оптимальное его значение составляет 10-20. Сигнал с РЗ инвертируется и поступает на входы параллельной загрузки СВВ, а также на вход детектора нажатий (ДН).

Детектор представляет собой элемент И с четырьмя входами. Если не нажата ни одна клавиша, то на выходе КК установлен код 0000. Этот код записывается в РЗ, инвертируется и поступает на ДН в виде 1111. В результате на выходе ДН устанавливается логическая единица. При нажатии на какую либо клавишу на выходе кодера клавиатуры установится значение, в котором будут присутствовать и нули и единицы. Это исключает возможность появления на входе ДН четырех единиц, и, следовательно, на выходе ДН при любой нажатой клавише установится логический ноль. Такой способ распознавания нажатых клавиш позволил упростить КК, отказавшись от специальной шины индикации нажатий, и позволил применить РЗ на 4 бита.

С выхода детектора нажатий сигнал поступает на счетчик нажатий (СН) и дешифратор позиций записи (ДПЗ). Счетчик нажатий имеет три разряда. Два из них используются непосредственно для подсчета нажатий, а третий – для блокировки схемы управления после ввода всех цифр. Счетчик переключается из одного состояния в другое только после отпускания клавиши. Это позволяет более рационально использовать его разряды благодаря присвоению первому нажатию номера 00.

Со счетчика нажатий число нажатых клавиш передается в двоичном коде на дешифратор ДПЗ. Он преобразует это число в десятичное и, по сигналу от схемы управления, подает разрешающий сигнал на соответствующий сегмент СВВ. Разрешающий сигнал подается на один из двух стробирующих входов ДПЗ. На второй стробирующий вход подается сигнал с выхода ДН. Это необходимо чтобы при ненажатых клавишах запретить загрузку в СВВ значения 1111.

Записанный в сегмент СВВ двоично-десятичный номер нажатой клавиши поступает на дешифратор, который преобразует его в код семисегментного индикатора. Этот код подается на полупроводниковый индикатор, который высвечивает соответствующее число.

После отпускания клавиши на вход детектора нажатий поступает код 1111, на его выходе соответственно происходит перепад 0 – 1 и счетчик нажатий переводится в следующее состояние. После 4-го отпускания клавиши логическая единица устанавливается в третьем разряде СН. С этого разряда она подается на схему управления, блокируя ее работу и запрещая дальнейшую загрузку значений в СВВ, а также на блок управления исполнительными устройствами (БУИУ), разрешая запуск исполнительных устройств. Цикл ввода на этом заканчивается. При желании можно повторить ввод. Для этого на клавиатуре нажимают клавишу «Сброс». Сигнал от этой клавиши подается на схему обнуления, которая вырабатывает сигнал обнуления для РЗ, СВВ и СН, переводя их в исходные состояния.

Для запуска процесса формирования выдержки необходимо нажать на клавишу «Пуск» на клавиатуре. Сигнал с этой клавиши подается на вход БУИУ, который разрешает прохождение импульсов с делителя частоты на вход СВВ. Первый же перепад 0 – 1 с выхода схемы блокировки прохождения импульсов через БУИУ включает исполнительное устройство. Начинается цикл формирования выдержки. Он продолжается до тех пор пока на вход СВВ не поступит заданное количество импульсов N. При появлении на входе СВВ фонта импульса с номером N+1 на БУИУ подается сигнал окончания выдержки, который отключает исполнительное устройство. На этом интервал выдержки заканчивается. Как видно из приведенных вкладок он может быть рассчитан по формуле:

T= tи + tзсвв – tзн

где

tи – длительность импульса на входе СВВ,

tзсв - задержка распространения в СВВ,

tзн – задержка включение нагрузка, обусловленная задержкой в БУИУ.

Если минимальный интервал выдержки составляет 1с то последними двумя значениями можно пренебречь, т.к. их величины (порядка десятков ns) не будет вносить существенной погрешности .

Помимо БУИУ сигнал окончания выдержки подается также на схему обнуления, которая приводит все устройство в исходное состояние, разрешая тем самым загрузку нового значения в СВВ.

В заключении необходимо отметить, что процесс формирования выдержки времени в любой момент можно прервать путем нажатия на кнопку «Сброс».

Разработка принципиальной схемы

Блоки предустановки значения выдержки

____________________________________________________________

1) Клавиатура

Клавиатура, используемая в данной разработке должна содержать не менее двенадцати клавиш – клавиши для ввода цифр 0…9 и две функциональные клавиши – “сброс” и “пуск”.

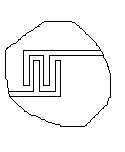

Как показал анализ различных конструктивных вариантов клавиатур, а также обзор промышленно выпускаемых клавиатур, наиболее приемлема конструкция фирмы “TESLA” типа GP-8213.

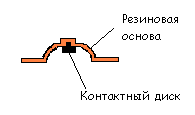

Конструкция представляет собой пластину из диэлектрического материала (стеклотекстолит) на которой методом химического травления выполнены контактные площадки. Пример такой площадки показан на рисунке (рис. ). Для замыкания между собой этих контактов используется резиновый диск, на который напылена тонкая пленка электропроводящего материала.

Диск приклеивается к резиновому основанию, которое исполняет роль пружины (рис. ).

При нажатии на клавишу контактный диск прижимается к металлическим контактным площадкам и замыкает их между собой. Как показали измерения, несмотря на то, что электропроводящий слой достаточно тонкий, сопротивление такого контакта составляет примерно 60 Ом, что вполне приемлемо для управления цифровыми микросхемами ТТЛ (ТТЛШ).

Схема соединения контактных площадок приведена на рис. Н. Одна из сторон каждого контакта клавиш 0…9 а также клавиши “пуск” соединяется с источником питания +5В. Входная сторона клавиши “стоп” соединяется с нулевым проводом.

Сопротивление резистора R зависит от входного сопротивления кодера клавиатуры, и будет определено далее.

Клавиатура укрепляется на передней панели устройства под окном цифрового индикатора.

2) Кодер клавиатуры

Как сказано выше, кодер клавиатуры должен обеспечивать преобразование десятичного кода в инверсный двоичный код. Среди микросхем серии 155 (555) имеются микросхемы выполняющие функцию перекодировки кода “1 из 10” в двоичный код. Однако эти микросхемы имеют один существенный недостаток – у них отсутствуют инверсные выходы. Это не позволяет использовать их в данном кодере без применения дополнительных инверторов. Поэтому было принято решение в качестве кодера использовать составленную соответствующим образом диодную матрицу.

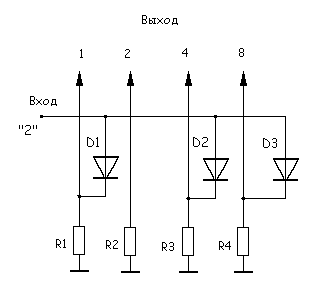

Таблица истинности кодера приведена в табл. , а принципиальная схема кодирования одного из входов (”2”) – на рис.

| Номер входа | Выходной код | |||

| 1 | 2 | 4 | 8 | |

| 1 | 0 | 1 | 1 | 1 |

| 2 | 1 | 0 | 1 | 1 |

| 3 | 0 | 0 | 1 | 1 |

| 4 | 1 | 1 | 0 | 1 |

| 5 | 0 | 1 | 0 | 1 |

| 6 | 1 | 0 | 0 | 1 |

| 7 | 0 | 0 | 0 | 1 |

| 8 | 1 | 1 | 1 | 0 |

| 9 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 1 |

Рис.

При подаче положительного напряжения на вход “2” диоды открываются и на выходе устанавливаются инверсные логические уровни 1101, соответствующие числу два.

Резисторы R1-R4 необходимы для надежного открывания диодов, в случае если входное сопротивление регистра-защелки окажется слишком велико.

Минимальное сопротивление этих резисторов выбирается исходя из максимального допустимого тока через диоды. При этом учитывается то, что их сопротивление должно быть в 5-6 раз больше чем сопротивление ограничительного резистора в блоке клавиатуры.

Максимальное сопротивление резисторов ограничивается минимальным входным током логических элементов ТТЛШ, при котором входной сигнал воспринимается как логический ноль. Это сопротивление рекомендуется не более 3 кОм. Исходя из этого было выбрано сопротивление R1-R4 2,7 кОм, а сопротивление ограничительного резистора в клавиатуре – 470 Ом.

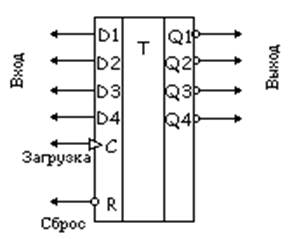

3) Регистр-защелка

Регистр-защелка должен обеспечивать запись входных значений по сигналу от СУ и выдачу этих значений в инверсном коде. Помимо этого он должен иметь вход обнуления. Количество разрядов регистра должно быть не менее четырех. При всем многообразии возможные технических решений наиболее экономичным является использование в качестве РЗ микросхемы К555ТМ8, которая предназначена для построения параллельных регистров данных, запускаемых перепадами тактовых импульсов. Микросхема расположена в 16-контактном корпусе и содержит набор D-триггеров, имеющих общие входы синхронного сброса R и тактового запуска С._В микросхеме ТМ8 число триггеров четыре, у каждого есть прямые и инверсные выходы Q. Цоколевка микросхемы показана на рис. . Режимы работы триггеров микросхемы соответствуют табл. . Сброс всех триггеров в состояние Qн = 0 произойдет, когда на вход асинхронного сброса R будет подано напряжение низкого уровня. Входы C и Dn при этом не действуют, их состояние безразлично.

Информацию от параллельных входов данных D1-D4 можно загрузить в триггеры микросхемы, если на вход R подать напряжение высокого уровня, а на тактовый вход С – положительный перепад импульса. При этом предварительно установленные на каждом входе D напряжения высокого или низкого уровня появятся на выходе Q.

Микросхема К555ТМ8 потребляет ток 18 мА, максимальная тактовая частота составляет 35 МГц, время задержки распространения сигнала сброса – 28 ns.

Рис.

Табл.

|

Режим работы |

вход | Выход | |||

| R | C | Dn | Qn | Qn | |

| Сброс | 0 | Х | Х | 0 | 1 |

| Загрузка 1 | 1 | 0-1 | 1 | 1 | 0 |

| Загрузка 0 | 1 | 0-1 | 0 | 0 | 1 |

4) Детектор нажатий

Как было сказано выше, в качестве детектора нажатий используется логический элемент И с четырьмя входами. Поскольку в серии К555 есть только элементы И–НЕ то придется использовать дополнительный инвертор. Наиболее целесообразно в качестве ДН использовать микросхему К555ЛА1 – два логических элемента 4И–НЕ. Схема ДН, построенная на этой микросхеме приведена на рис.

Один из элементов используется по своему прямому назначению, а второй выступает в качестве детектора.

Рис.

Микросхема потребляет ток 2,2 мА. Максимальная задержка распространения в одном ЛЭ – 15 ns. Цоколевка микросхемы показана на рис.

Рис.

5) Дешифратор позиций загрузки

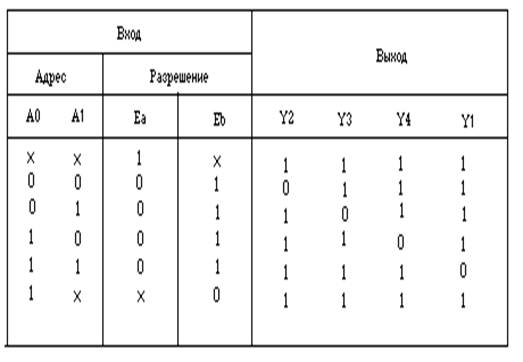

Согласно структурной схеме дешифратор позиций загрузки на основании входного двухразрядного двоичного кода должен устанавливать логический ноль на одном из четырех выходов. Кроме того он должен иметь два инверсных входа стробирования, подключаемых к схеме управления и к детектору нажатий. Наиболее подходящим решением в данном случае является использование в качестве ДПЗ одного из дешифраторов ИМС К555ИД4.

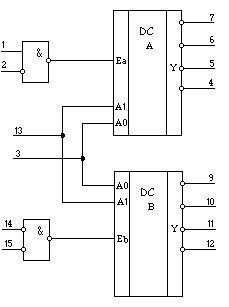

Микросхема К155ИД4 (рис. ) — два дешифратора, принимающих двухразрядный код адреса А0, А1. Дешифратор DC A имеет два входа разрешения: прямой Еа и инверсный Ёа, а дешифратор DC B — только инверсные входы разрешения дешифрации Еb.

Рис.

Если микросхема используется как демультиплексор, дешифратор DC A может принимать по входам Еа и Еа как прямой, так и инверсный адресные коды. Состояния для обоих дешифраторов как при дешифрации кода А0, А1, так и при демультиплексировании по адресу А0, А1 сведены в табл.

Табл.

Микросхема К555ИД4 потребляет ток 10 мА. Время задержки распространения сигнала от адресного входа А к выходу Y составляет 32 ns, время распространения от входа разрешения Е к выходу Y не превышает 30 ns для обоих вариантов исполнения.

Принципиальная схема ДПЗ построенного на К555ИД4 приведена на рис.

Рис.

На входы А0 и А1 подается двоичное число произведенных нажатий клавиш от счетчика нажатий, а на входы Е1 и Е2 – сигналы разрешения от детектора нажатий и схемы управления. Выходы 0,1,2,3 подключаются к соответствующим разрядам счетчика выдержки времени.

Блоки отсчета выдержки

_______________________________________________________

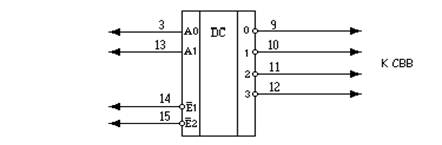

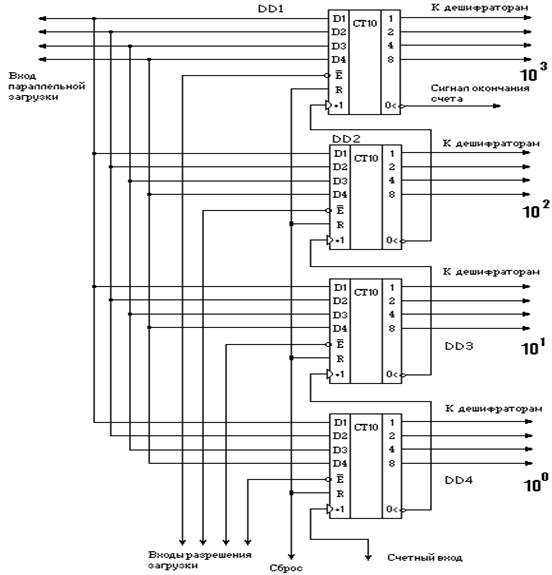

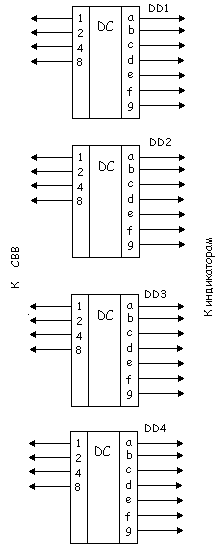

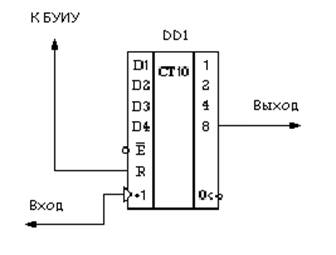

1) Счетчик выдержки времени

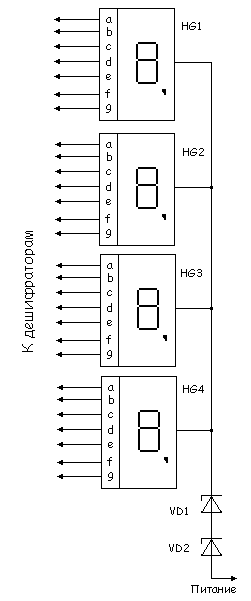

Счетчик выдержки времени является одним из основных узлов данного устройства. Он предназначен для подсчета количества поступающих от задающего генератора импульсов. Принципиальная схема счетчика приведена на рис. Счетчик работает в режиме вычитания – из заданного первоначально количества импульсов с приходом очередного импульса вычитается единица. Когда счетчик полностью обнулится, на его выходе "<0" (МС DD1) появляется логический ноль, который, воздействуя на БУИУ, отключит нагрузку. Загрузка значений в счетчик производится параллельным способом, путем подачи соответствующего двоичного значения на входы D0 - D4, и логического нуля на один из входов разрешения загрузки Е.

Рис.

Тактовые импульсы подаются на счетный вход +1 микросхемы DD4. Блок дешифраторов подключается к выводам 1-2-4-8 каждой из микросхем.

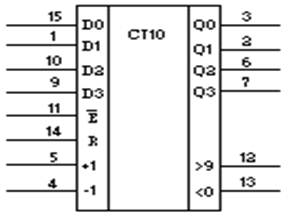

Для построения счетчика была использована микросхема К555ИЕ6, что позволило обойтись всего четырьмя микросхемами без каких либо дополнительных элементов. Цоколевка микросхемы показана на рис.

Рис.

Микросхема представляет собой реверсивный двоично-десятичный счетчик. Импульсные тактовые входы для счета на увеличение +1 (вывод 5) и на уменьшение -1 (вывод 4) в этой микросхеме раздельные. Состояние счетчика меняется по положительным перепадам тактовых импульсов от низкого уровня к высокому на каждом из этих тактовых входов.

Для упрощения построения счетчиков с числом разрядов, превышающих четыре, микросхема имеет выводы окончания счета на увеличение (">9", вывод 12) и на уменьшение ("<0", вывод 13). От этих выводов берутся тактовые сигналы переноса и заема для последующего и от предыдущего четырехразрядного счетчика. Дополнительной логики при последовательном соединении этих счетчиков не требуется: выводы ">9" и "<0" предыдущей микросхемы присоединяются к выводам "+1" и "-1" последующей. По входам разрешения параллельной загрузки РЕ и сброса R запрещается действие тактовой последовательности и даются команды загрузки четырехразрядного кода в счетчик или его сброса.

Если

на вход "–1" подается импульсный перепад от низкого уровня к высокому,

от содержимого счетчика вычитается 1. Аналогичный перепад, поданный

на вход +1, увеличивает

счет на 1. Если для счета

используется один из этих входов, на

другом тактовом входе следует

зафиксировать напряжение высокого логического

уровня. Первый триггер счетчика не может переключиться, если на его тактовом

входе зафиксировано напряжение низкого уровня. Во избежание ошибок менять

направление счета следует в моменты, когда запускающий тактовый импульс перешел на высокий уровень,

т. е. во время плоской вершины импульса.

На выходах ">9" и "<0" нормальный уровень—высокий. Если счет достиг максимума (цифра 9), с приходом следующего тактового перепада от высокого уровня к низкому на вход +1 (более 9) на выходе ">9" появится напряжение низкого уровня. После возврата напряжения на тактовом входе "+1" к высокому уровню, напряжение на выходе ">9" останется низким еще на время, соответствующее двойной задержке переключения логического элемента ТТЛ.

Аналогично на выходе "<0" появляется напряжение низкого уровня, если на вход "-1" пришел счетный перепад низкого уровня. Импульсные перепады от выходов ">9" и "<0" служат, таким образом, как тактовые для последующих входов "+1" и "-1" при конструировании счетчиков более высокого порядка. Такие многокаскадные соединения счетчиков ИЕ6 не полностью синхронные, поскольку на последующую микросхему тактовый импульс передается с двойной задержкой переключения.

Если на вход разрешения параллельной загрузки Е (вывод 11) подать напряжение низкого уровня, то код, зафиксированный ранее на параллельных входах DO—D3 (выводы 15, 1, 10 и 9), загружается в счетчик и появляется на его выходах QO—Q3 (выводы 3, 2, 6 и 7) независимо от сигналов на тактовых входах. Следовательно, операция параллельной загрузки — асинхронная.

Параллельный запуск триггеров запрещается, если на вход сброса R (вывод 14) подано напряжение высокого уровня. На всех выходах Q установится низкий уровень. Если во время (и после) операций сброса и загрузки придет тактовый перепад (от Н к В), микросхема примет его как счетный.

Счетчики К555ИЕ6 потребляют ток 34 мА. Максимальная тактовая частота 25 МГц. Время задержки распространения сигнала от входа "+1" до выхода ">9" 26 ns, аналогичные задержки от входа Е до выхода Q3 составляют 40 ns. Время действия сигнала сброса (от входа R до выходов Q) 35 ns.

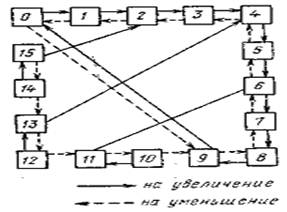

На рис. , показана диаграмма работы десятичного счетчика ИЕ6, где обозначены логические переходы сигналов при счете на увеличение и уменьшение. Кольцевой счет возможен в пределах 0...9, остальные шесть состояний триггерам запрещены. Составив определенную комбинацию входных сигналов, по табл. можно выбрать один из четырех режимов работы счетчика ИЕ6. Счет на увеличение здесь закончится при выходном коде ВННВ (9), на уменьшение — при НННН (0).

Рис.

Табл.

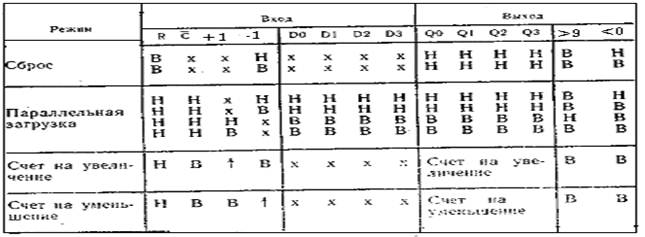

3) Блок индикации.

Для индикации состояния СВВ были использованы семисегментные индикаторы типа АЛС324Б. Схема соединения индикаторов показана на рис.

Рис.

При конструировании устройства индикаторы устанавливаются на передней панели, слева направо, начиная с HL1. Стабисторы D1 и D2 служат для предотвращения перегрузки преобразователя кода. Принцип их действия заключается в том что напряжение источника питания +5V распределяется между тремя сопротивлениями нагрузки и сопротивлениями D1 и D2, сопротивлением сегмента индикатора и сопротивлением транзисторного ключа микросхемы. Поскольку суммарное падение напряжения на сегменте индикатора и ключа микросхемы не должно превышать 2 – 2,5 V (при этом ток через эти элементы будет в пределах допустимого), в большинстве подобных схем раньше использовался ограничительный резистор, который устанавливался в разрыв провода между микросхемой и индикатором. При этом на каждый индикатор требовалось 7 таких резисторов.

Установить один общий резистор мешала его линейность, из–за которой, например, цифра 1 светилась очень ярко, а цифра 8 была практически не видна. Использование нелинейных элементов (стабисторов) позволило решить эту проблему. Благодаря нелинейной ВАХ падение напряжения на них остается практически постоянным, независимо от количества горящих сегментов, и поэтому яркость всех цифр одинакова. Применение такой схемы питания индикаторов позволило отказаться от использования 28 резисторов.

2) Преобразователь кода.

Преобразователь кода предназначен для перевода двоично – десятичного кода с выходов разрядов СВВ в код семисегментных индикаторов. Принципиальная схема этого блока показана на рис.

Рис.

Он состоит из четырех специализированных микросхем этого КР514ИД1. На входы этих микросхем подается четырех разрядный двоично – десятичный код а выходы подключаются к соответствующим разрядам индикатора. Как видно из схемы для управления индикатором применяется статический метод. Это позволило значительно упростить устройство индикации, хотя и потребовало использование большого количества соединительных линий. (28 штук).

Состояние выходов микросхемы КР514ИД1, сведены в таблицу.

Блоки управления

________________________________________________________________

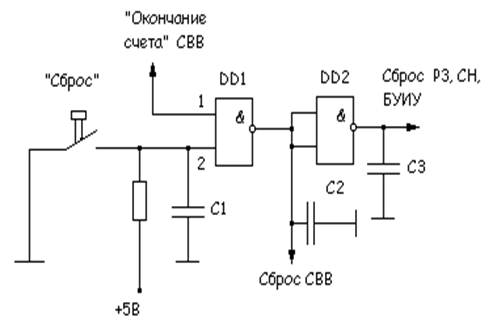

1 ) Схема обнуления.

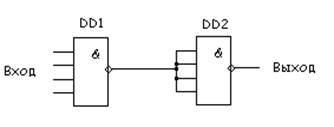

Принципиальная схема блока обнуления приведена на рис. Она состоит из 2 логических элементов DD1 и DD2 микросхемы К555ЛАЗ, причем элемент DD2 используется в качестве инвертора. Рассмотрим работу схемы.

Рис.

При первоначальном включении устройства конденсатор С1 заряжается через резистор R1. При этом в течении некоторого времени (порядка 0,1 секунды), на входе 2 DD1 присутствует логический ноль. В результате на выходе этого элемента устанавливается (независимо от состояния входа 1) логическая единица. Она подается на входы R микросхем СВВ, в результате чего последний обнуляется. Элемент DD2 необходим, поскольку входы сброса СН, РЗ и БУПУ в отличие от аналогичных входов СВВ, инверсные. Клавиша «Сброс» клавиатуры подключается параллельно конденсатору С1, а импульс сброса от СВВ подается вход 1. Это необходимо для того, чтобы время срабатывания схемы обнуления, которое складывается с временем выдержки, было минимальным и не оказывало на него существенного влияния .

После обнуления на выходе “окончание счета” СВВ и следовательно, на входе 1 DD1 устанавливается логическая единица, если конденсатор С1 заряжен а клавиша «Сброс» не нажата то схема перейдет в режим ожидания. На выходе “сброс СВВ” установится логический ноль разрешающий его работу. Конденсаторы С2 и С3 предназначены для предотвращения ложного срабатывания схемы из – за помех. Их емкость должны относиться между собой как (50 – 100) * С3 = С2, а максимальная емкость С2 выбирается так, чтобы время ее зарядки не оказывало заметного влияния на точность интервала выдержки.

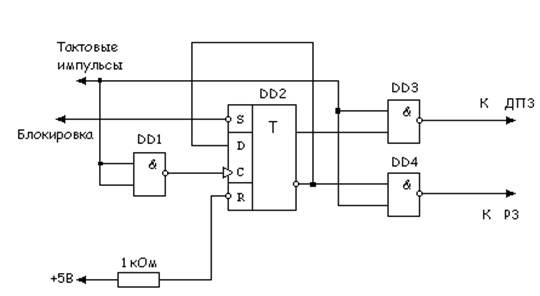

2) Схема управления

Принципиальная схема этого блока приведена на рис.

Он построен на одном из триггеров микросхемы К555ТМ2 и трех логических элементах микросхемы К555ЛА3. Характеристики этих микросхем были даны выше.

Блок предназначен для синхронного управления РЗ и ДПЗ. На вход “Тактовые импульсы” подаются импульсы с ТГ. Благодаря инвертору на элементе DD1 триггер переключается по спаду импульса.

Рис.

Для блокировки работы блока и следовательно окончания загрузки чисел с клавиатуры используется вход S триггера.

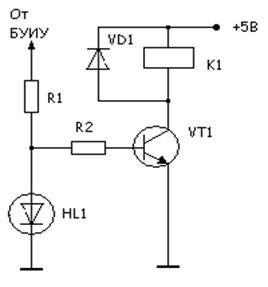

3) Исполнительное устройство.

Исполнительное устройство должно обеспечивать включение нагрузки на время выдержки или по прошествии этого времени. Принципиальная схема этого блока представлена на рис.

Рис.

Светодиод HL1 служит для индикации включения нагрузки. Помимо этого он, совместно с R1 выполняет роль делителя напряжения. С выхода этого делителя через резистор R2 напряжение подается на базу транзистора VT1 и открывает его. Резистор R2 ограничивает ток базы транзистора и, тем самым, предотвращает его влияние на БУИУ. Его сопротивление необходимо выбирать по возможности больше. В нашем случае оно было подобрано экспериментально и равно 10 кОм. В коллекторную цепь транзистора включается реле К1, которое своими контактами управляет нагрузкой. Диод VD1 необходим для замыкания токов самоиндукции, возникающих в обмотке реле при запирании транзистора. Тем самым он предотвращает пробой транзистора, а также возникновение помех по цепи питания микросхем. Сопротивление резистора R1 выбрано экспериментально, по приемлемой яркости свечения светодиода.

4) Блок управления исполнительным устройством.

Блок управления исполнительным устройством выполняет следующие функции:

- включает исполнительное устройство в начале интервала выдержки

- выключает исполнительное устройство после окончания выдержки

- отключает исполнительное устройство при нажатии на клавишу «Сброс»

- воспринимает нажатие на клавишу «Пуск» и подает сигнал управления на устройство блокировки.

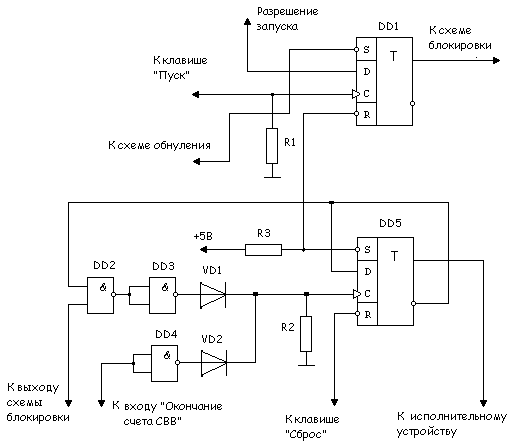

Принципиальная схема этого блока приведена на рис.

Рис.

На триггере DD1 построено устройство управления схемой блокировки. Вход D триггера подключается к третьему разряду CH. После четырех нажатий клавиш сюда подается логический ноль, разрешающий запуск отсчета времени. К входу С подключается клавиша «Пуск» клавиатуры. Когда эта клавиша не нажата, на С установлен логический ноль благодаря резистору R1. При нажатии на клавишу «Пуск» перепад 0–1 на входе С разрешает запись информации (нуля) на выход триггера и, следовательно разрешает прохождение импульсов делителя частоты к СВВ.

Вход S подключается схеме обнуления параллельно входу обнуления СН. На элементах DD1 – DD5 собрано устройство контроля, управляющее нагрузкой. После включения устройства в сеть или нажатия на клавишу «Сброс» триггер DD5 устанавливается в нулевое состояние. На вход D при этом подается логическая единица. Эта единица также устанавливается и на одном из входов элемента DD2, выполняющего в данном случае электронного ключа. После разблокирования схемы блокировки первый перепад 0–1 появившийся на ее выходе, пройдет через элементы DD2, DD3 и диод VD2 на вход с триггера. Триггер переключится в единичное состояние и подаст логическую единицу на исполнительное устройство. Логический ноль с его инверсного выхода поступит на DD2 и запретит прохождение через него следующих импульсов. В этом состоянии устройство будет находится до окончания счета, либо до нажатия на клавишу “Сброс”. По окончании счета логический ноль с соответствующего выхода СВВ поступит на входы элемента DD4, играющего роль инвертора, и далее через VD1, на вход С триггера. Логический ноль со входа D перепишется на выход триггера и отключит исполнительное устройство. Элементы VD1, VD2 и R2 представляют собой простейший логический элемент ИЛИ. Их применение позволило отказаться от микросхемы с элементами ИЛИ и обойтись имеющимися лишними элементами микросхемы К555ЛАЗ. Сопротивление резистора R2 подобрано экспериментально и равняется 2,7 кОм.

Характеристики использованных микросхем К555ТМ2 и К555ЛА3 приведены выше.

Генераторное оборудование

________________________________________________________________

1) Тактовый генератор

Тактовый генератор является одним из основных элементов цифрового таймера. От точности установки частоты этого генератора зависит точность интервала выдержки.

В цифровых таймерах применяют, как правило, высокостабильные кварцевые генераторы, которые устанавливают в специальные термостатирующие устройства, поддерживающие постоянную температуру окружающей среды.

Точность воспроизведения заданного временного интервала зависит также от частоты генератора. Чем она больше, тем больше коэффициент деления делителя частоты, и следовательно, тем больше делится значение погрешности установки частоты.

Кварцевые генераторы можно классифицировать по различным признакам.

1. По способам повышения стабильности частоты:

- Простой без дополнительных элементов, предназначенных для улучшения каких либо его параметров.

- Термокомпенсированный кварцевый генератор, отклонение частоты которого уменьшается с помощью специальной электрической цепи.

- Термостатированные кварцевые генераторы, элементы электрической цепи которого полностью или частично помещены в термостат для уменьшения влияния окружающей среды.

2.По допустимой нестабильности частоты КГ можно разделить на 7 групп:

- менее 0,001*10-6

- (0,001…0,01)*10-6

- (0,01…0,1) *10-6

- (0,1…1) *10-6

- (1…10) *10-6

- (10…100) *10-6

Внутри каждой группы стабильности могут быть различными. Целесообразно для унификации требований выбирать нестабильности по следующему ряду в одной группе: ±1; ±1,5; ±2; ±2,5; ±3; ±5; ±7,5 и ±10.

Обычно в кварцевых генераторах за классификационную стабильность принимают температурную стабильность частоты в рабочем интервале температур.

3.По диапазону частот:

- низкочастотные (1 —1000 кГц);

- среднечастотные (1—30 МГц);

- высокочастотные (выше 30 МГц).

4. Элементной базе и способам конструирования:

- на дискретных элементах;

- гибридные с резонатором;

- гибридные с пьезоэлементом;

- интегральные с пьезоэлементом;

- интегральные на пьезоэлементе

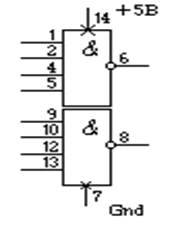

Поскольку конструирование кварцевых генераторов сложно и дорого, в макете таймера был использован простой RC генератор на логических элементах микросхемы К555ЛА3.

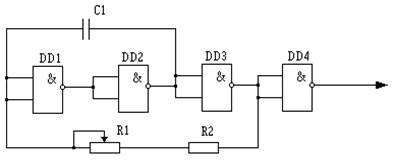

Принципиальная схема этого генератора приведена на рис.

Сам генератор собран на элементах DD1-DD3. Он представляет собой обычный

несимметричный мультивибратор. Частота выходных импульсов зависит от значений

элементов C1, R1, R2 и

вычисляется по формуле

F = 1/(3*(R1+R2)*C1)

Элемент DD4 используется в качестве буфера. Он предотвращает влияние нагрузки генератора на частоту.

2) Делитель частоты.

Делитель частоты предназначен для получения длительностей импульсов большей, чем длительность импульсов, вырабатываемых генератором. Он позволяет применять генераторы импульсов высокой частоты и тем самым значительно упрощает построение последних. К тому же применение делителя позволяет повысить точность воспроизведения заданного временного интервала, т.к. относительная погрешность установим частоты тактового генератора делится на коэффициент деления делителя К, т.е. уменьшается в К раз. Как было сказано в предыдущей главе, при построении макета использовался простейший тактовый генератор на частоту порядка 10Гц. Это позволило также упростить и делитель частоты применив в нем всего одну микросхему – двоично–десятичный счетчик К555ИЕ6.

Принципиальная схема делителя представлена на рис.

Рис.

На вход “+1” микросхемы подаются импульсы с тактового генератора. Выход “8” подключается ко входу СВВ и БУПУ. Такая схема делителя позволила полностью исключить схему блокировки. Ее роль исполняет сам делитель. Как было сказано ранее, если на вход R подать логическую единицу то на выходах 1–2–4–8 микросхемы установится логический ноль независимо от состояний остальных входов. Это означает, что микросхема блокируется и не реагирует на импульсы, поступающие на вход “+1”, т.е. не пропускает их.

В реальных таймерах делитель частоты строится, как правило на коэффициент деления К = 105…107 . В сочетании с высокостабильным кварцевым генератором это позволяет получить очень точное значение выдержек. Например в электронных частотомерах интервал счета в 1 секунду получают путем деления частоты кварцевого генератора 5 МГц на 5000000.

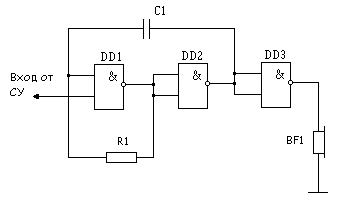

3) Устройство сигнализации.

Устройство сигнализации представляет собой простейший генератор прямоугольных импульсов, к выходу которого подключен микротелефонный капсюль. Схема показана на рис.

Рис.

Сам генератор собран на элементах DD1, DD2. Для управления подачей звуковых сигнала используется один из входов элемента DD1. Включение генератора осуществляется подачей на этот вход логической единицы. Элемент DD3 служит в качестве буферного. Он предотвращает влияние сопротивления капсюля на частоту генерации. Конденсатор С3 предотвращает протекание постоянного тока через капсюль при отсутствии генерации. Его емкость выбирается в пределах 0,01 – 0,1 мкФ, в зависимости от требуемой громкости и тональности звучания. Резистор R1 выводит элемент DD1 в линейный усилительный режим. Его значение для элементов ТТЛШ рекомендовано 220 Ом конденсатор С1 создает положительную обратную связь, необходимую для самовозбуждения схемы. Частота автогенерации, как сказано выше, равняется

F=1/(3*R1*C1)

При емкости конденсатора С1=1мкФ и сопротивлением R=220Ом частота генерации равняется

F=1/(3*220*10-6)=1500Гц

Список литературы

___________________________________________________

1. В.Л. Шило «Популярные цифровые микросхемы» М. 1989 г

2. Н. Н. Васерин «Применение полупроводниковых индикаторов» М. 1991 г.

3. Ю. И. Степанов «Справочник по ЕСКД» К. 1975 г.

4. А. Уильямс «Применение интегральных схем» М. 1987 г.

5. С. А. Бирюков «Цифровые устройства на интегральных микросхемах» М. 1991 г.