Реферат: Вычислительная техника

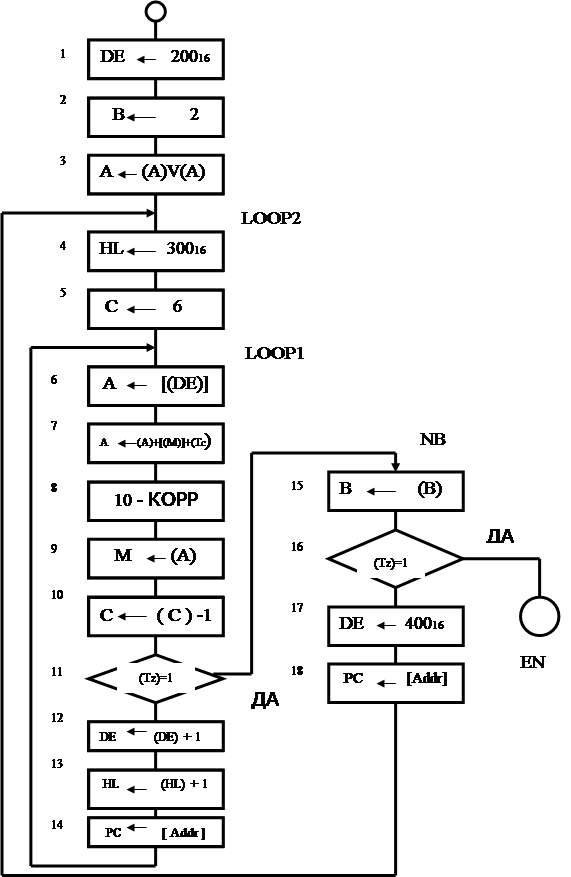

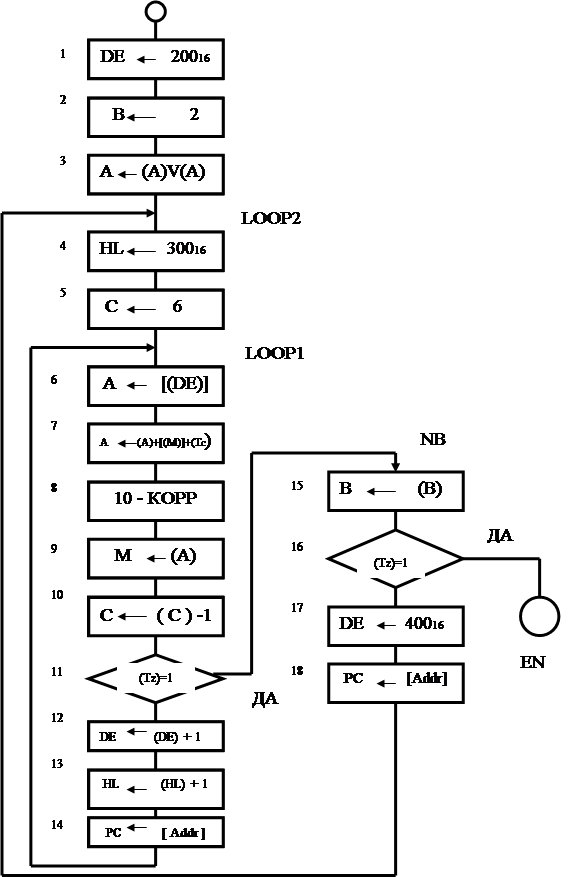

часть: Проектирование вырожденного автомата .

Спроектировать на элементах ТТЛ “ генератор 4-х разрядных кодов “ некоторой системы счисления .

Т.е. синтезировать синхронный счётчик М–разрядный ( М < 16 ), на вход которого подаётся регулярная внешняя последовательность тактовых импульсов.

Каждое состояние счётчика ( т.е. цифра заданной системы ) сохраняется в течение одного полного такта. Значение цифр появляется на выходах Q3, Q2, Q1, Q0. Автомат также должен выработать синхронный перенос ( в след. разряд заданной системы), которым служит последний тактовый импульс в цикле счёта. Для его выделения должен быть сформирован строб “y” , т.е. булева функция , которая активна на последнем такте цикла. А само выделение должно обеспечивать минимальную задержку выходного импульса переноса.

В схеме автомата должны быть цепи , осуществляющие авто сброс в исходное состояние при каждом включении питания.

Требуется :

- составить таблицу функционирования автомата ;

- минимальную функцию возбуждения и строба ;

- построить осциллограммы всех выходных функций, включающие функции строба и сигнала переноса ;

- построить схему автомата .

Решение поставленной задачи :

а.) Составим таблицу функционирования автомата :

| Q3 | Q2 | Q1 | Q0 | J3 | K3 | J2 | K2 | J1 | K1 | J0 | K0 | y | |||

| 0 | 0 | 0 | 0 | 0 | 0 | Ф | 0 | Ф | 0 | Ф | 1 | Ф | 0 | ||

| 1 | 0 | 0 | 0 | 1 | 0 | Ф | 0 | Ф | 1 | Ф | Ф | 1 | 0 | ||

| 2 | 0 | 0 | 1 | 0 | 0 | Ф | 0 | Ф | Ф | 0 | 1 | Ф | 0 | ||

| 3 | 0 | 0 | 1 | 1 | 0 | Ф | 1 | Ф | Ф | 1 | Ф | 1 | 0 | ||

| 4 | 0 | 1 | 0 | 0 | 0 | Ф | Ф | 0 | 0 | Ф | 1 | Ф | 0 | ||

| 5 | 0 | 1 | 0 | 1 | 0 | Ф | Ф | 0 | 1 | Ф | Ф | 1 | 0 | ||

| 6 | 0 | 1 | 1 | 0 | 0 | Ф | Ф | 0 | Ф | 0 | 1 | Ф | 0 | ||

| 7 | 0 | 1 | 1 | 1 | 1 | Ф | Ф | 1 | Ф | 1 | Ф | 1 | 0 | ||

| 8 | 1 | 0 | 0 | 0 | Ф | 0 | 0 | Ф | 0 | Ф | 1 | Ф | 0 | ||

| 9 | 1 | 0 | 0 | 1 | Ф | 0 | 0 | Ф | 1 | Ф | Ф | 1 | 0 | ||

| 10 | 1 | 0 | 1 | 0 | Ф | 0 | 0 | Ф | Ф | 0 | 1 | Ф | 0 | ||

| 11 | 1 | 0 | 1 | 1 | Ф | 0 | 1 | Ф | Ф | 1 | Ф | 1 | 0 | ||

| 12 | 1 | 1 | 0 | 0 | Ф | 1 | Ф | 1 | 0 | Ф | 1 | Ф | 1 | ||

|

|

0 | 0 | 0 | 0 |

б.) Составим карты Карно и при помощи них найдём минимизированные функции возбуждения и строба .

|

|||||

|

|||||

| 0 | 0 | 0 | 0 | ||

|

|

0 | 1 | 0 | ||

|

|

Х | Х | Х | ||

| Ф | Ф | Ф | Ф |

|

J3 = Q2Q1Q0

|

|||||

|

|||||

|

|

Ф | Ф | Ф | ||

|

|

Ф | Ф | Ф | ||

|

|

Х | Х | Х | ||

| 0 | 0 | 0 | 0 |

|

K3 = Q2

|

|||||

|

|||||

![]()

| 0 | 0 | 1 | 0 | ||

|

|

Ф | Ф | Ф | ||

|

|

Х | Х | Х | ||

| 0 | 0 | 1 | 0 |

|

J2 = Q1Q0

|

|||||

|

|||||

![]()

| Ф | Ф | Ф | Ф | ||

|

|

0 | 1 | 0 | ||

|

|

Х | Х | Х | ||

| Ф | Ф | Ф | Ф |

|

K2 = Q3 v Q1Q0

|

|||||

|

|||||

|

|

1 | Ф | Ф | ||

|

|

1 | Ф | Ф | ||

|

|

Х | Х | Х | ||

| 0 | 1 | Ф | Ф |

|

J1 = Q0

|

|||||

|

|||||

| Ф | Ф | 1 | 0 | ||

|

|

Ф | 1 | 0 | ||

|

|

Х | Х | Х | ||

| Ф | Ф | 1 | 0 |

|

K1 = Q0

|

|||||

|

|||||

| 1 | Ф | Ф | 1 | ||

|

|

Ф | Ф | 1 | ||

|

|

Х | Х | Х | ||

| 1 | Ф | Ф | 1 |

|

J0 =

Q3Q2

J0 =

Q3Q2

|

|||||

|

|||||

| Ф | 1 | 1 | Ф | ||

|

|

1 | 1 | Ф | ||

|

|

Х | Х | Х | ||

| Ф | 1 | 1 | Ф |

|

K0 = 1

|

|||||

|

|||||

| 0 | 0 | 0 | 0 | ||

|

|

0 | 0 | 0 | ||

|

|

Х | Х | Х | ||

| 0 | 0 | 0 | 0 |

|

y = Q3Q2

в.) Построим осциллограммы всех выходных функций , вкл функцию строба и сигнала переноса .

|

|

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() С

С

![]()

![]()

![]()

![]()

![]()

![]() Q0

Q0

![]()

![]()

![]() Q1

Q1

![]()

![]()

![]() Q2

Q2

![]() Q3

Q3

![]()

![]()

![]() y

y

![]()

![]()

![]()

![]()

![]() Cвых

Cвых

г.) Построение схемы автомата .

II часть : Проектирование интерфейса ЗУ некоторого МПУ .

Построить интерфейс ЗУ на реальных МС , приведённых в таблице .

Блоки ПЗУ и ОЗУ должны содержать резервные места для модернизации . Резерв может быть до 50% рабочего и объёма блока , но не менее 1 МС выбранного типа .

При условии восьмиразрядного выхода требуется :

- определить объём пространства памяти , включая резервные сегменты ;

- составить таблицу адресов , начиная с адреса 0ХХ0, где ХХ = n – номер студента по журналу в 16-ричной системе ;

- построить упрощённую схему интерфейса .

При построении блока ПЗУ использовать МС ППЗУ серии КР556 для Lпзу < 6 Кб и МС СППЗУ ( К573 ) для Lозу > 7Кб .

При построении блока ОЗУ - МС с технологией : ТТЛ для Lозу < 3 Кб , И*ИЛ для 7Кб < Lозу < 9 Кб , МОП для 4КБ < Lозу < 6Кб .

При полу целом числе сегментов в блоке допускается использование МС другой технологии с ёмкостью 0,5 сегмента . Остаток неполного сегмента отнести к резерву .

Решение поставленной задачи :

а.) Определим объём пространства памяти , включая резервные сегменты .

Для ПЗУ можно выбрать пять МС СППЗУ типа К573РФ2 с организацией 2К * 8 = 2Кб .

Тогда объём одного сегмента можно выбрать равным 2 Кб = 80016. Возьмем пять таких МС и , таким образом , получили объём ПЗУ равным 10 Кб , но нам необходимо набрать 11 Кб , поэтому возьмём ещё две МС СППЗУ типа К573РФ1 с организацией 1К*8 = 1Кб для организации шестого сегмента , половина которого будет использована , а другая половина будет в резерве.

Для резерва возьмём две МС СППЗУ типа К573РФ2 с организацией 2К * 8 = 2Кб , т.е. объём резерва получился равным 5 Кб.

С резервом в 5 Кб для ПЗУ получили восемь сегментов.

Для ОЗУ можно выбрать МС nМОП типа КМ132РУ8А с организацией 1К * 4 = 0,5 Кб. Но для построения одного сегмента потребуется четыре такие МС .

С резервом в 2Кб для ОЗУ потребуется три таких сегмента .

Значит, общий объём блока ЗУ с резервом должен составлять 8+3 = 11 сегментов .

б.) Составим таблицу распределения адресов .

Ф

Ф

0

0